Vivado在使用A7芯片时,使用内部逻辑分析仪时,在非AXI总线下最多只能绑定64组信号(例化一个或者多个ILA模块,信号组数相加不能超过64),如果超过64组会出现错误。

Xilinx Vivado软件ILA使用心得

- Xilinx(130366)

相关推荐

热点推荐

急急急!我正在使用vivado2019.2,请帮忙生成一个项目。

和文件要求在vivado2019.2上严格正确执行,要求无报错。

能解决的大神请加QQ 2257993511,希望这两天解决。

2025-12-19 23:17:52

探索Xilinx Kria KR260机器人入门套件:开启机器人应用开发新旅程

探索Xilinx Kria KR260机器人入门套件:开启机器人应用开发新旅程 在当今科技飞速发展的时代,机器人技术的应用越来越广泛。对于电子工程师来说,拥有一款优秀的开发套件至关重要。今天,我们

2025-12-15 14:45:02 231

231

231

231探索AMD XILINX Versal Prime Series VMK180评估套件,开启硬件创新之旅

探索AMD XILINX Versal Prime Series VMK180评估套件,开启硬件创新之旅 在电子设计的领域中,快速实现原型设计并确保高性能是每一位工程师的追求。AMD XILINX

2025-12-15 14:40:02 229

229

229

229AMD Vivado Design Suite 2025.2版本现已发布

AMD Vivado Design Suite 2025.2 版本现已发布,新增对 AMD Versal 自适应 SoC 的设计支持,包含新器件支持、QoR 功能及易用性增强。

2025-12-09 15:11:32 722

722

722

722IKSEMI发布高性能车规级CAN芯片组:IN2515与ILA82C251,全面替代MCP2515及PCA82C251

半导体品牌IKSEMI凭借其自主研发的IN2515CAN控制器与ILA82C251CAN收发器,为汽车电子系统提供了安全、可靠且完整的CAN总线通信解决方案。这两款芯片均已通过严苛的AEC-Q100

2025-12-02 09:25:55 261

261

261

261

Xilinx FPGA串行通信协议介绍

Xilinx FPGA因其高性能和低延迟,常用于串行通信接口设计。本文深入分析了Aurora、PCI Express和Serial RapidIO这三种在Xilinx系统设计中关键的串行通信协议。介绍了它们的特性、优势和应用场景,以及如何在不同需求下选择合适的协议。

2025-11-14 15:02:11 2357

2357

2357

2357

NVMe高速传输之摆脱XDMA设计44:工程设计考量?

。

基于 VC709 FPGA 的 Block Design 工程设计如图 1 所示。 图中 CPU 模块中包含了 Xilinx 提供的 Microblaze CPU 软核以及一些内存与复位模块, 除时钟

2025-11-12 09:52:14

请问如何将蜂鸟E203移植到Xilinx NEXYS A7 FPGA 开发板上?

如何将蜂鸟E203移植到Xilinx NEXYS A7 FPGA 开发板上?有参考教程吗?小白求教

主要是引脚分配,我这边有移植到Xilinx Artix-7 系列XC7A100T-fgg484的案

2025-11-11 07:44:12

使用Vivado 2018.2编译E203的mcs文件,遇到的问题求解

Hi 各位,我在尝试使用Vivado 2018.2编译E203的mcs文件,遇到如下两个问题:

1. 按照书中步骤运行,执行完make mcs之后得到的mcs文件与git中预编译出来的mcs文件有

2025-11-11 06:04:55

请问如何在e203中安装linux操作系统?

本人用的板子是Xilinx的XC7A100TFGG484-2L,编译软件是vivado2017.4。目前比特流已经成功生成,我已经把其固化进了板子中。现在的我想在我固化后的板子里面装一个linux操作系统,应该如何做?

2025-11-07 07:32:38

vivado连接Atry A7-35T死机怎么解决?

前提条件:

1)开发板是Digilent的ARTY A7-35T开发版,也就是《手把手教你设计CPU-RISC-V处理器》中介绍的那块板子

2)vivado安装正常,可以启动,跑make mcs

2025-11-07 06:05:07

利用 NucleiStudio IDE 和 vivado 进行软硬件联合仿真

本文利用NucleiStudio IDE 和 vivado 对 NICE demo协处理器进行软硬件联合仿真。

1. 下载demo_nice例程:https://github.com

2025-11-05 13:56:02

vivado的hardware manager找不到HummingBird Evaluation kit,是什么原因?

购买了HummingBird Evaluation kit,按照书本的指示,

(1)连接FPGA JTAG

(2)连接电源,并上电

(3)打开vivado,并进入Hardware manager,发现没有找到HummingBird Evaluation kit

可能的原因是什么?多谢!

2025-11-05 07:11:49

Windows环境下用Vivado调试E203

第一步 选择RTL文件

创建Vivado工程后,将e203_hbirdv2-masterrtle203下的所有Verilog文件加入工程;

此外还有fpgamcu200tsrc目录

2025-11-05 06:25:59

开源RISC-V处理器(蜂鸟E203)学习(二)修改FPGA综合环境(移植到自己的Xilinx FPGA板卡)

../../../home/Xilinx/Vivado/2019.1/data/boards/board_files/

回到e203工程的FPGA目录下,重新运行命令,成功启动vivado并加载整个工程

2025-10-31 08:46:40

Hbirdv2在vivado2018.3上的仿真工作

一、队伍介绍

本篇为蜂鸟E203系列分享第一篇。本篇介绍的内容是Hbirdv2在vivado2018.3上的仿真工作。

二、前言

仿真前,我们首先需要获得仿真需要的.verilog文件,我们

2025-10-31 08:43:38

Vivado仿真之后没有出现仿真结果的解决方法

;Run Behavioral Simulation之后,会出现如下图界面,此时,在Tcl Console中并没有出现仿真结果。

没有出现仿真结果的原因是没有给Vivado时间进行仿真,解决方法

2025-10-31 06:24:20

利用vivado实现对e200_opensource 蜂鸟E203一代的仿真

分享一代E203的vivado调试方法(windows/linux皆可)。比赛小队名:强强联合队。报名编号:CICC1316

1.新建vivado项目

此处注意勾选Do not specify

2025-10-31 06:14:34

生成Bitstream的DRC LUTLP-1错误的解决办法

vivado综合和实现完成后,在生成Bit文件时出现已知设计原理的DRC错误。下面图中的DRC LUTLP-1的loop错误是设计可接受的的。

且对仿真结果不影响,综合实现都通过,到生成

2025-10-30 07:42:10

vivado时序分析相关经验

vivado综合后时序为例主要是有两种原因导致:

1,太多的逻辑级

2,太高的扇出

分析时序违例的具体位置以及原因可以使用一些tcl命令方便快速得到路径信息

2025-10-30 06:58:47

Windows系统下用vivado将电路烧写到MCU200T板载FLASH的方法

文件自动完成FPGA硬件电路的烧写。这样就不必每次调试软件之前都需要重新打开vivado工程下载bitstream,可以更加方便地进行嵌入式软件开发。

首先打开vivado工程,综合,实现

2025-10-29 08:21:12

ILA 抓取MCU200T的内部信号

我们在调BUG的过程中单纯利用引脚输出中间变量的方法可能比较困难,因此我们在实际的开发过程中使用了ILA内嵌式逻辑分析仪来进行内部信号的捕捉和观察。

1、在E203的 vivado工程中打开IP

2025-10-29 08:03:17

FPGA的图像采集过程

读取所有128个寄存器的值并存入RAM,RAM的存入地址即为寄存器的地址。读写模式选择通过一个开关控制,在写操作完成后会产生一个同步信号初始化下一模块以进行后续的操作。

在Vivado中通过加入ILA

2025-10-29 06:23:17

将e203 例化AXI总线接口

将系统外设总线内部axi接口引出给gpio,注意vivado中gpio地址分配应保证移植

Debug:

通过Xil_Out32函数给gpio的地址写1或者0,注意这里地址是gpio地址也就是核中给

2025-10-29 06:08:12

DDR存储拓展教程

电复位初始化:

***注:关于vivado自带的嵌入式逻辑分析仪ila的使用可以直接百度,网上一堆图文教程,本人在此不再赘述。

六、通过nuclei studio软件读写测试

我们

2025-10-28 07:25:32

在Windows10上运行vivado使用tcl文件创建E203项目路径错误的问题

软件版本是vivado2020.1,开发板是MCU200T。由于习惯使用了Windows系统所以想在Windows上创建vivado项目进行开发。但是由于Makefile更适合Linux系统,所以

2025-10-28 07:19:22

win10环境下使用vivado生成.bit与.mcs文件

,这里介绍一种可以直接在windows环境下使用vivado生成system.bit和system.mcs文件的方法。

1.在windows环境安装vivado,准备好e203_hbirdv2工程

2025-10-27 08:25:28

Vivado仿真e203_hbirdv2跑whetstone跑分(开源)

环境:Vivado2018.3、NucleiStudio_IDE_202102-win64

内容:Vivado仿真e203_hbirdv2跑whetstone跑分

以下提供可以在Vivado

2025-10-27 07:21:04

在VIVADO中对NICE进行波形仿真的小问题的解决

https://www.rvmcu.com/community-topic-id-386.html

以上链接为如何生成.verilog,并在VIVADO中生成波形的例子。我们在实践过程中,发现了两个

2025-10-27 06:41:49

没有开发板的情况,在Vivado上进行蜂鸟E203的基础内核的drystone跑分

由于开发板可能不能第一时间拿到手,而这时候我们要开始相关的工作,所以我们需要找到一种方法在没有开发板下能够推进进度,本文主要介绍在Vivado下进行drystone的仿真跑分。

创建一个Vivado

2025-10-27 06:35:08

在利用Xilinx开发板烧录E203V2软件程序,无MCU下载器时利用FPGA Jtag下载器烧录软件程序

解决问题:在利用Xilinx开发板开发E203V2项目时,会有两个下载器,分别是FPGA Jtag下载器,用于下载硬件代码如(bit、mcs),和MCU下载器,用于下载Nuclei studio

2025-10-24 13:12:00

没有开发板的情况下,在Vivado上进行蜂鸟E203的基础内核的drystone跑分

由于开发板可能不能第一时间拿到手,而这时候我们要开始相关的工作,所以我们需要找到一种方法在没有开发板下能够推进进度,本文主要介绍在Vivado下进行drystone的仿真跑分。

创建一个Vivado

2025-10-24 07:36:49

vcs和vivado联合仿真

我们可能就需要用到vcs核vivado联合仿真。

1.Vivdao仿真库编译

打开vivado软件,点击Tools–>Compile Simulation Libraries

2025-10-24 07:28:03

FPGA开发板vivado综合、下载程序问题汇总

在做vivado综合时和FPGA下载程序时,我们碰到以下问题,并找出了对应的解决方案。

1.could not open include file”e203_defines.v”问题

在做

2025-10-24 07:12:12

如何在vivado上基于二进制码对指令运行状态进行判断

vivado仿真运行判断状态是否正确。

获取二进制代码

在Nucleistudio中打开相关项目的Properties,按路径打开C/C++ Build ->setting,找到

2025-10-24 06:46:36

在vivado上基于二进制码对指令运行状态进行判断

vivado仿真运行判断状态是否正确。

获取二进制代码

在Nucleistudio中打开相关项目的Properties,按路径打开C/C++ Build ->setting,找到

2025-10-24 06:31:26

Vivado中向FPGA的Flash烧录e203的方法

Hardware Manager。

将板子与电脑通过数据线连接,这里使用的DDR200T开发板需要将数据线连接到FPGA_JTAG接口,打开开发板电源,在Vivado中选择Open Target-Auto

2025-10-23 08:28:02

Nucleistudio+Vivado协同仿真教程

编译完成后,我们会在工程目录下发现生成了.verilog文件,此即为我们仿真需用到的文件,可以将改文件复制保存在tb目录下

联合仿真

在我们前面创建的Vivado工程中添加仿真文件

2025-10-23 06:22:05

如何在Vivado上仿真蜂鸟SOC,仿真NucleiStudio编译好的程序

如标题所示,我们分享如何在Vivado上仿真蜂鸟SOC,仿真NucleiStudio编译好的程序

具体步骤

1. 将蜂鸟soc移植到Vivado

只要将端口映射好,注意配置好时钟和bank

2025-10-21 11:08:55

正点原子FPGA达芬奇PRO核心板无法连接vivado,求救!!!

我自己画的底板,底板主要提供5V、接地以及JTAG连接器。但是插上XC7A35T的核心板后,vivado显示找不到target(vivado截图见图1)。图2-3是我的底板原理图,原理图和pcb文件在附件,求大佬指点迷津!!*附件:PCB_Project_1.rar

2025-10-13 16:05:54

AMD Vivado设计套件2025.1版本的功能特性

随着 AMD Spartan UltraScale+ 系列现已投入量产,解锁其功能集的最快途径便是采用最新 AMD Vivado 工具版本( 2025.1 或更高版本)和全新操作指南资源。该集

2025-09-23 09:15:55 1390

1390

1390

1390

AMD Vivado ChipScope助力硬件调试

许多硬件问题只有在整个集成系统实时运行的过程中才会显现出来。AMD Vivado ChipScope 提供了一套完整的调试流程,可在系统运行期间最大限度提升对可编程逻辑的观测能力,助力设计调试。

2025-09-05 17:08:41 1023

1023

1023

1023一文详解xilinx 7系列FPGA配置技巧

本文旨在通过讲解不同模式的原理图连接方式,进而配置用到引脚的含义(手册上相关引脚含义有四、五页,通过本文理解基本上能够记住所有引脚含义以及使用场景),熟悉xilinx 7系列配置流程,以及设计原理图时需要注意的一些事项,比如flash与FPGA的上电时序。

2025-08-30 14:35:28 9291

9291

9291

9291

vivado仿真时GSR信号的影响

利用vivado进行设计xilinx FPGA时,写完设计代码和仿真代码后,点击run simulation(启动modelsim进行仿真)。

2025-08-30 14:22:17 1157

1157

1157

1157

FPGA利用DMA IP核实现ADC数据采集

本文介绍如何利用FPGA和DMA技术处理来自AD9280和AD9708 ADC的数据。首先,探讨了这两种ADC的特点及其与FPGA的接口兼容性。接着,详细说明了使用Xilinx VIVADO环境下

2025-07-29 14:12:22 4847

4847

4847

4847Vivado无法选中开发板的常见原因及解决方法

在使用 AMD Vivado Design Suite 对开发板(Evaluation Board)进行 FPGA 开发时,我们通常希望在创建工程时直接选择开发板,这样 Vivado 能够自动配置

2025-07-15 10:19:43 1521

1521

1521

1521

EDA是什么,有哪些方面

,常见工具如Altera的Quartus、Xilinx的Vivado。

PCB设计:实现电路板布局、网络连接和阻抗控制,典型软件包括Altium Designer、Cadence Allegro

2025-06-23 07:59:40

AMD Vivado Design Suite 2025.1现已推出

AMD Vivado Design Suite 2025.1 现已推出,支持 AMD Spartan UltraScale+ 和新一代 Versal 器件。这一最新版本还新增了多项功能,可显著提升 Versal SSIT 器件的 FMAX 值,并对所有系列产品在 IP 集成和功能验证方面的易用性进行了改进。

2025-06-16 15:16:04 1342

1342

1342

1342FPGA调试方式之VIO/ILA的使用

在Vivado中,VIO(Virtual Input/Output)是一种用于调试和测试FPGA设计的IP核,它允许设计者通过JTAG接口实时读取和写入FPGA内部的寄存器,从而检查设计的运行状态并修改其行为。VIO IP核提供了一个简单易用的接口,使得用户可以轻松地与FPGA内部寄存器进行交互。

2025-06-09 09:32:06 3371

3371

3371

3371

FPGA远程烧写bit文件和调试ILA指南

在 FPGA 开发过程中,烧写bit文件和使用ILA进行调试是再常见不过的操作。但如果 FPGA 板卡被放在机房,或者通过PCIe插在服务器上,那么每次调试时我们都不得不带着笔记本电脑跑去机房或服务器旁,接上 JTAG 线后才能进行调试,非常不便。

2025-06-05 16:41:28 2214

2214

2214

2214

10年LED驱动设计工程师的恒流IC使用心得

以前的LED灯具都是用恒压电源,当时不了解LED的性能,按照厂家给的数据每只小灯珠给到20MA,经过我们测试后,灯珠总是烧掉,才知道厂家的数据是不可靠的,我们减小了电流使用。那时是在2002年,做些MR16小灯泡,广告牌之类的应用。我是2007年才开始做恒流驱动,什么HV9910,PT4107,PT6901,SN3910,IR的,试验多了,但是最先成功的是QX9910,出过一些货,但是QX9910有很多不良品,老化后的产品也不太稳定,经常有闪灯现象,现在还有一些剩余的做纪念品了。我认为,要想做好驱动,先要找好芯片。

当初在07年的时候,恒流IC很难找到,价格也贵的离奇,一片HV9910要8元,一片IR的 S2540要25元,其实就是一个半桥芯片,拿来唬人,还有什么日本的一些芯片也是拿来唬人的,其实就是一般的恒压IC,我在这些无聊的芯片上走了很长时间的弯路,严重影响了进度。

HV9910系列产品在第二代IC也很流行,但是技术原因,高压直接进IC,容易炸机。后来出来了很多仿制品,仿的最好是SMD802,多个输出短路保护,曾被大量采用,随着更新换代,这种IC现在也落伍了。 很多种IC还没有正式投产就夭折了。 09年推出了BP2808,这种非隔离的IC用了几年都是长胜不衰,做1000片也很难坏一个电源,因为BP2808是第三代IC,性能稳定,它能输出30W以上的功率,并可长期使用,效率更高,轻松95%。 这种驱动芯片都有一个共同的缺点,就是EMCT EMI不好过,经大家长期的探索认为在MOS电源输入端加二个差模电感就能解决EMC,而EMI的解决办法是有几种,有的在MOS管的漏极加个磁珠,但这种方法加大了损耗来换取的,我的办法是在漏源极(S-D)用100P以上的陶瓷电容加到上面的,这种方法能有效提高效率,还能控制EMI。

晶丰在不断的进取,现在又推出BP3105,在宽电压的范围内,恒流精度在1%,这样击败了国内外所有的方案公司,国内的第一家调光恒流IC:BP3109也不错的,它的设计是亮度在一定情况下截止,避免了闪亮现象,成本很低。听说下半年还有更好的IC推出。

BP2808也有仿制的,但是晶丰明源现在已调整价格,贵三、二毛还是用原厂的稳定,这种仿制的IC在一家供货样品时就出了问题,试验四个烧了二个灯板,有几家向我推广我没敢用。

但是现在国内最便宜的IC是芯联的,CL1100原边控制小功率电源,适应灯杯系列产品。芯联是靠抄板起家,这样成本就低,所以卖的价格便宜,性能还可以接受,稳定性也很好,因此出货量很大,也是最流行的芯片之一,当然该公司也有更大功率的芯片。

GR8210,是台湾绿达公司的产品,在试验时表现还不错,效率和功率因数都很好,它是在BP2808的基础上改进了EMC,但是在出货量大的情况下就不是很理想,里面有10%以上的不良品,另外同样的串连方式,在并联数量变化时,电感量也要跟着变换,所以对电感的要求特高,好处是EMC在内部得到控制,容易过EMC。这种IC的成本较高,到现在也没有几家量产,不宜水土。

低压DC-DC成本最低属MC34063了,一个芯片只要0.23元,经过使用是3*1W,1*3W做的还不错,电流再大就不好说了。

获取完整文档资料可下载附件哦!!!!如果内容有帮助可以关注、点赞、评论支持一下哦~

2025-06-05 16:18:13

基于AD9613与Xilinx MPSoC平台的高速AD/DA案例分享

本文主要介绍基于Xilinx UltraScale+MPSoC XCZU7EV的高速AD采集与高速DA输出案例

2025-06-03 14:22:30 740

740

740

740

学电路设计分享学习心得、技术疑问及实战成果

《硬件开发与电路设计速成实战篇(入门到精通)》系列课程活动:学习完《硬件开发与电路设计速成实战篇(入门到精通)》系列课程,可到张飞电子技术社区分享学习心得、提出技术

2025-05-20 08:07:43 483

483

483

483

如何使用One Spin检查AMD Vivado Design Suite Synth的结果

本文讲述了如何使用 One Spin 检查 AMD Vivado Design Suite Synth 的结果(以 Vivado 2024.2 为例)。

2025-05-19 14:22:26 1111

1111

1111

1111

安森美WebDesigner+设计工具使用心得

安森美(onsemi)近期推出的开发工具试用活动已圆满收官,本次活动吸引了众多工程师的积极参与,通过实际应用体验安森美先进的开发工具,共同挖掘其在设计中的潜力。之前推文已分享过用WebDesigner+ 设计工具完成120W DC-DC隔离电源设计、通过Elite Power仿真工具,简化125KW 储能系统设计,今天分享的试用报告聚焦WebDesigner工具,一起来了解下。

2025-05-16 15:19:00 776

776

776

776

生物制造车间中CCLINKIE从站转EtherCAT从站协议网关应用心得

在生物制造车间,各类设备是生产的核心“成员”,但它们之间的“交流障碍”曾让我十分头疼。CCLinkie和Ethercat协议就像不同的语言,让设备难以协同工作。直到JH-ECT012疆鸿智能CCLinkie转Ethercat协议网关的出现,才打破了这一僵局。 车间里的设备种类繁杂,有像发酵罐、离心机这样的“元老”设备,它们大多使用CCLinkie协议与控制系统相连;而新引进的高精度检测仪器和先进的自动化执行机构,比如智能传感器、高速机械臂,则倾向于使用Ethercat协议。这

2025-05-16 14:37:28 380

380

380

380Xilinx Shift RAM IP概述和主要功能

Xilinx Shift RAM IP 是 AMD Xilinx 提供的一个 LogiCORE IP 核,用于在 FPGA 中实现高效的移位寄存器(Shift Register)。该 IP 核利用

2025-05-14 09:36:22 912

912

912

912适用于Versal的AMD Vivado 加快FPGA开发完成Versal自适应SoC设计

设计、编译、交付,轻松搞定。更快更高效。 Vivado 设计套件提供经过优化的设计流程,让传统 FPGA 开发人员能够加快完成 Versal 自适应 SoC 设计。 面向硬件开发人员的精简设计流程

2025-05-07 15:15:09 1169

1169

1169

1169

Vivado 2018.3软件的使用教程

大家好,欢迎来到至芯科技FPGA炼狱营地,准备开启我们的伟大征程!正所谓“兵马未动,粮草先行”,战前的准备自是必不可少,在FPGA的漫漫沙场,我们何以入场,何以取胜呢?在这里我们为各位战友准备了vivado 2018.3的使用教程。

2025-04-30 14:14:18 3068

3068

3068

3068

详解Xilinx的10G PCS PMA IP

如果要在Xilinx的FPGA上使用万兆以太网通信,大致有三种方法构建协议栈。第一种使用GTX等Serdes作为底层的PHY,上层通过HDL实现构建MAC和IP层,这种方式难度会比较大,底层需要完成PHY层的设计,最终我想通过这种方式实现万兆以太网的搭建。

2025-04-18 15:16:30 1732

1732

1732

1732

蜂鸟N203移植到xilinx ZCU104板子上,用JTAG调试的时出现报错怎么解决?

求助各位大佬,蜂鸟N203移植到xilinx ZCU104板子上,用JTAG调试的时候出现这样的错误

在vivado里面跟JTAG有关的约束如下:

在调试的时候,用的是Nuclei官方的调试器

2025-04-17 06:33:29

Vivado HLS设计流程

为了尽快把新产品推向市场,数字系统的设计者需要考虑如何加速设计开发的周期。设计加速主要可以从“设计的重用”和“抽象层级的提升”这两个方面来考虑。Xilinx 推出的 Vivado HLS 工具可以

2025-04-16 10:43:12 1432

1432

1432

1432

福禄克ST20MAX红外测温仪究竟有多好用

“精准测量、智能预约、坚固耐用、贴心设计…” 小福带着首批ST20MAX客户试用心得来啦!ST20MAX 究竟有多好用?让我们一探究竟!

2025-04-10 13:55:27 723

723

723

723一文详解Vivado时序约束

Vivado的时序约束是保存在xdc文件中,添加或创建设计的工程源文件后,需要创建xdc文件设置时序约束。时序约束文件可以直接创建或添加已存在的约束文件,创建约束文件有两种方式:Constraints Wizard和Edit Timing Constraints,在综合后或实现后都可以进行创建。

2025-03-24 09:44:17 4561

4561

4561

4561

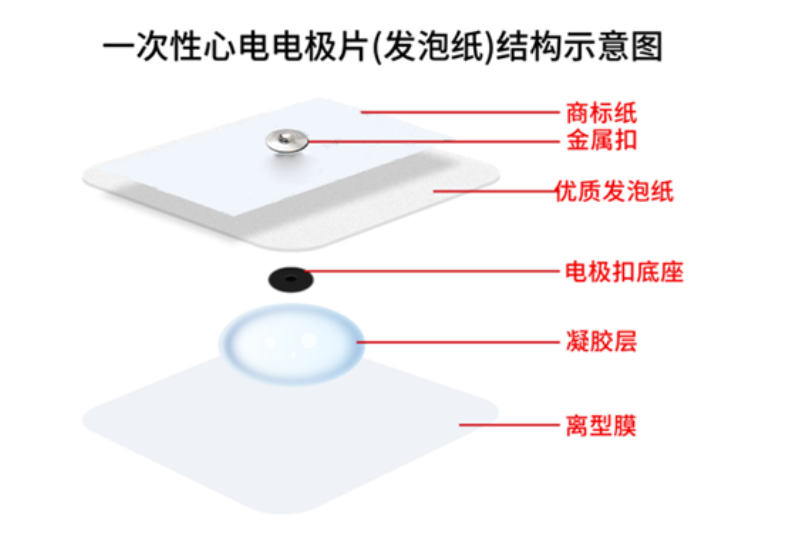

一次性使用心电电极片性能测试 深圳一测

一次性使用心电电极片性能测试 :YICE0196 心电电极电性能测试仪、 心电电极电性能测试仪(SEAM) 心电电极性能测试仪

2025-03-19 11:27:20 1229

1229

1229

1229

蜂鸟N203移植到xilinx ZCU104板子上,用JTAG调试的时候出现错误怎么解决?

求助各位大佬,蜂鸟N203移植到xilinx ZCU104板子上,用JTAG调试的时候出现这样的错误

在vivado里面跟JTAG有关的约束如下:

在调试的时候,用的是Nuclei官方的调试器

2025-03-07 16:46:40

e203在vivado硬件里自定义指令识别为非法指令怎么解决?

e203自定义指令硬件模块设计,修改内核,综合没错误,软件也修改工具链通过并产生verilog文件,但在vivado硬件里自定义指令识别为非法指令怎么解决

2025-03-07 07:34:21

Vivado FIR IP核实现

Xilinx的FIR IP核属于收费IP,但是不需要像 Quartus那样通过修改license文件来破解。如果是个人学习,现在网络上流传的license破解文件在破解Vivado的同时也破解

2025-03-01 14:44:19 2709

2709

2709

2709

【应用】SFM3304医用气体流量传感器使用心得

SFM3000在医疗气体流量监测领域展现出高可靠性,其一次性设计显著降低交叉感染风险,尤其适用于ICU、急诊等场景。该传感器在性能与易用性间取得了良好平衡,是医疗设备升级的理想选择。

2025-02-26 17:22:49 956

956

956

956

影像测量仪软件功能

前言影像测量仪软件功能主菜单栏:存放软件的主要功能和不常用功能。为了保持界面清洁,很多不常用功能可在主菜单栏找到。图像区:显示图像并进行元素测量操作的区域。图形区:测量结果在该区域以几何方式显示,可

2025-02-20 10:04:18

AMD Vivado Design Suite IDE中的设计分析简介

本文档涵盖了如何驱动 AMD Vivado Design Suite 来分析和改善您的设计。

2025-02-19 11:22:26 989

989

989

989

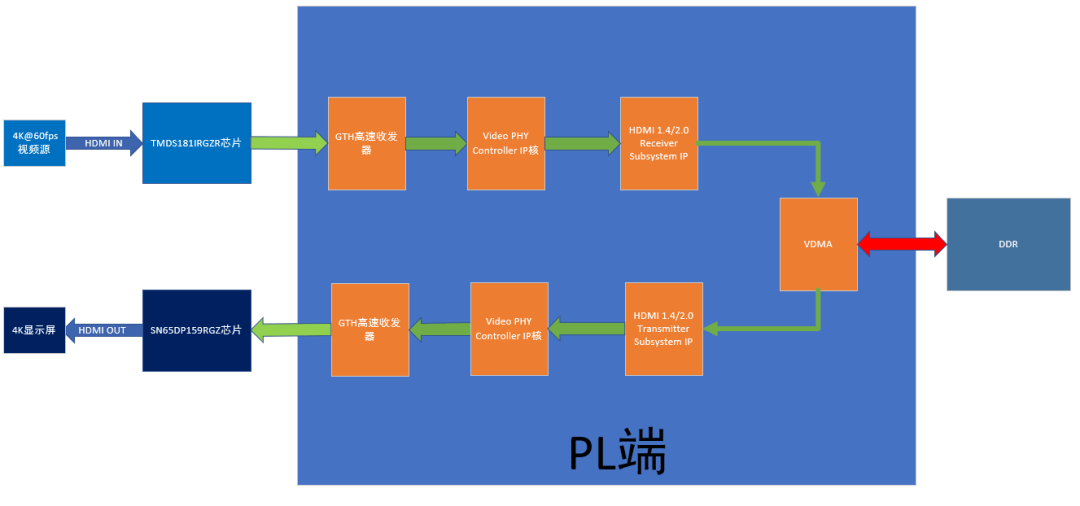

解锁4K,Xilinx MPSoC ARM + FPGA高清视频采集与显示方案!

当下,随着数字化多媒体技术以令人惊叹的速度不断演进,高清视频处理成为众多领域关注的焦点。今天为大家分享4K HDMI 高清视频方案,基于Xilinx UltraScale+ MPSoC

2025-01-24 10:27:05 979

979

979

979

xilinx FPGA IOB约束使用以及注意事项

xilinx FPGA IOB约束使用以及注意事项 一、什么是IOB约束 在xilinx FPGA中,IOB是位于IO附近的寄存器,是FPGA上距离IO最近的寄存器,同时位置固定。当你输入或者输出

2025-01-16 11:02:01 1655

1655

1655

1655

Vivado Design Suite用户指南: 设计分析与收敛技巧

电子发烧友网站提供《Vivado Design Suite用户指南: 设计分析与收敛技巧.pdf》资料免费下载

2025-01-15 15:28:44 2

2

2

2【米尔-Xilinx XC7A100T FPGA开发板试用】 UART测试

硬件:

一 米尔-Xilinx XC7A100T FPG

二 12V电源适配器

三 下载器

四 win10笔记本

软件:

一 Vivado (指导手册有详细的安装下载流程)

二 官方示例工程

这个

2025-01-12 10:10:40

【米尔-Xilinx XC7A100T FPGA开发板试用】Key-test

硬件:

一Xilinx XC7A100T FPGA开发板

二12V电源适配器

三下载器

四 win10笔记本

软件:

一Vivado (指导手册有详细的安装下载流程)

二官方按键示例工程

按键示例

2025-01-09 16:08:51

Vivado Xilinx FFT IP核v9.0使用说明

一 傅里叶变换FFT 想必大家对傅里叶老人家都不陌生了,网上也有这方面的很多资料。通过FFT将时域信号转换到频域,从而对一些在时域上难以分析的信号在频域上进行处理。在这里,我们需要注意采样频率、FFT采样点数这两个参数: 根据奈奎斯特采样定理,采样频率需大于信号频率的两倍; FFT采样点数,代表对信号在频域的采样数; 采样频率Fs和采样点数N决定了信号的频域分辨力,即分辨力=Fs/N,即N越大,频域分辨力越好,反之频域分辨力越差。 二

2025-01-08 11:33:44 3264

3264

3264

3264

ADS1298作为心电信号采集的模拟前端, 使用心电图机检定仪进行共模抑制比的测试时,结果不是很理想怎么改善?

产品使用了ADS1298作为心电信号采集的模拟前端, 使用心电图机检定仪进行共模抑制比的测试时,结果不是很理想。右腿驱动和屏蔽驱动都使用了,还可能是哪些方面的原因,或者有什么方法可以改善。

1.是不是使用镀金的连接器会好一点。

2.导联线放在屏蔽盒子中。

2025-01-08 08:05:01

电子发烧友App

电子发烧友App

评论