set_property BITSTREAM.CONFIG.UNUSEDPIN Pulldown [current_design]

set_property BITSTREAM.CONFIG.UNUSEDPIN Pullup [current_design]

set_property BITSTREAM.CONFIG.UNUSEDPIN Pullnone [current_design]

Vivado约束未使用引脚

相关推荐

CYUSB3304-68LTXC如果未使用SUSPEND引脚,是否可以不连接此引脚?

如果未使用 SUSPEND 引脚,是否可以不连接此引脚? 我想移除 LED,因为我不需要使用 LED 发送通知。

2024-02-22 07:50:46

求助,关于CX3上未使用的I/O引脚的简单问题

这是一个关于 CX3 上未使用的 I/O 引脚的简单问题。CYUSB306X 数据表(第 20 页)建议 \" 应使用内部上拉电阻 \" 将所有未使用的 I/O 拉高。 但是,我

2024-02-22 06:55:29

如何处理 MBR (CY8CMBR3106S) 中那些未使用的引脚?

很抱歉我对 MBR (CY8CMBR3106S) 有些困惑。 希望你能帮我澄清一下。

#1。 如何处理 MBR (CY8CMBR3106S) 中那些未使用的引脚?!

我们能否让它们漂浮而不是将它

2024-01-22 07:28:13

如何禁止vivado自动生成 bufg

在Vivado中禁止自动生成BUFG(Buffered Clock Gate)可以通过以下步骤实现。 首先,让我们简要了解一下什么是BUFG。BUFG是一个时钟缓冲器,用于缓冲输入时钟信号,使其更稳

2024-01-05 14:31:06 454

454

454

454FPGA物理约束之布局约束

在进行布局约束前,通常会对现有设计进行设计实现(Implementation)编译。在完成第一次设计实现编译后,工程设计通常会不断更新迭代,此时对于设计中一些固定不变的逻辑,设计者希望它们的编译结果

2024-01-02 14:13:53 434

434

434

434

VIVADO安装问题解决

vivado出现安装问题刚开始还以为是安装路径包含中文空格了,重装的注意了一下,发现还是这个问题。。。。后来又一顿操作猛如虎,终于发现了问题。出这个问题的原因是vivado压缩包解压的路径包含中文了把解压文件放到不含中文的地方,再重新安装,安装路径也不能含中文。然后。。。。。然后就安装完成了

2023-12-22 10:56:33 0

0

0

0FPGA物理约束之布线约束

IS_ROUTE_FIXED命令用于指定网络的所有布线进行固定约束。进入Implemented页面后,Netlist窗口如图1所示,其中Nets文件展开后可以看到工程中所有的布线网络。

2023-12-16 14:04:31 507

507

507

507

SV约束随机化总结

constraint 约束随机化类中的变量

在main_phase 之前就已经提前产生一个变量的随机值。

用法:一般在类中定义一个rand 类型的变量, 然后根据需求写约束就可以

2023-12-14 14:30:06 188

188

188

188

FPGA器件几个比较常用的配置配置约束

Xilinx Vivado工具的配置约束隐藏得比较深,如图1所示,在进入配置页面前,首先需要点击PROGRAM AND DEBUG->Generate Bitstream执行工程的全编译,然后点击IMPLEMENTATION->OpenImplemented Design进入实现页面。

2023-12-02 12:19:19 219

219

219

219

物理约束实践:I/O约束

I/O约束(I/O Constraints)包括I/O标准(I/OStandard)约束和I/O位置(I/O location)约束。

2023-11-18 16:42:28 506

506

506

506

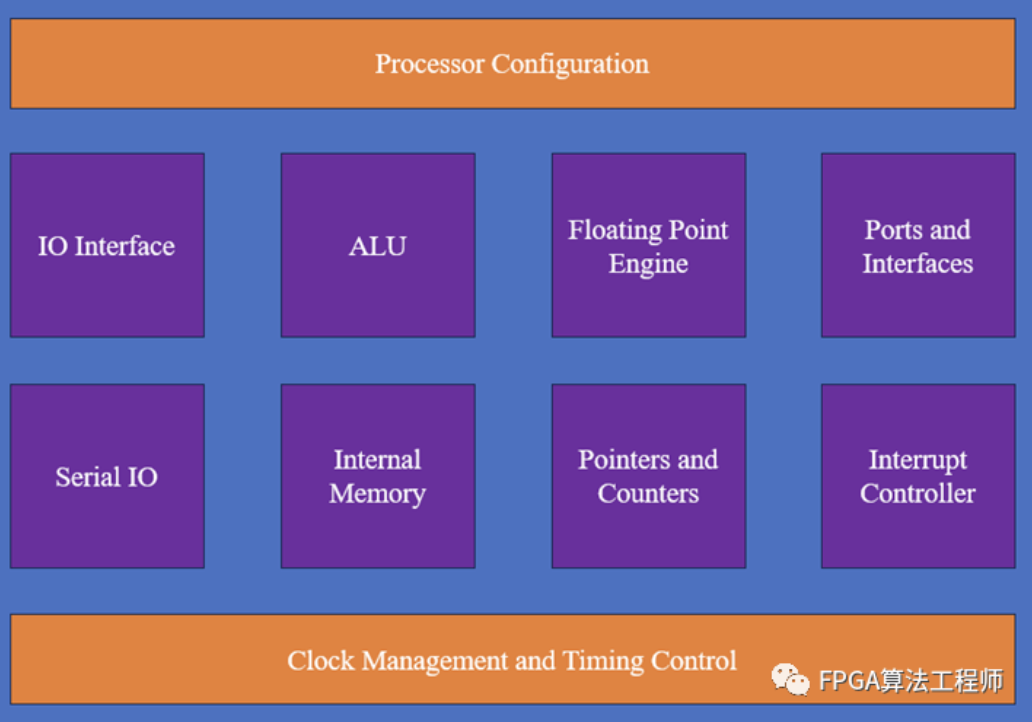

FPGA时序约束--基础理论篇

。

时序约束可以让VIvado和Quartus等FPGA开发软件,在布线时检测综合出来的逻辑电路是否满足这个时序要求,并生成时序报告。

一、建立/保持时间

1、基本概念

设定时序约束的目的就是为了满足

2023-11-15 17:41:10

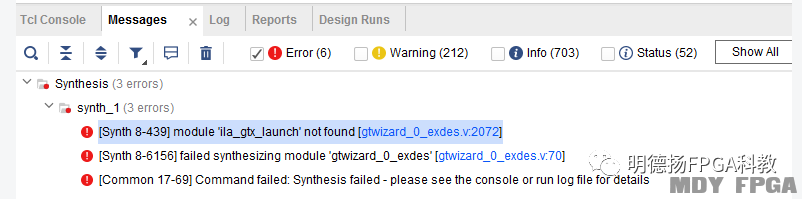

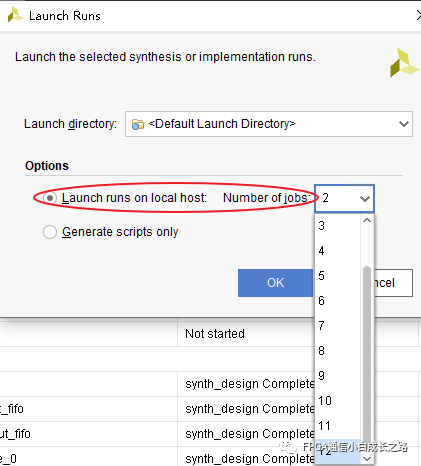

vivado 2018.1 综合失败且不报错、不生成runme.log日志文件,求大神帮忙

本人是一名FPGA小白,目前在学习如何使用vivado软件,买了一块ALINX的开发板,按照它的使用教程走到了综合(Synthesis)这一步,但是反复多次,都是综合失败并且综合时间很长,如图

2023-09-22 10:10:24

FPGA的约束设计和时序分析

在进行FPGA的设计时,经常会需要在综合、实现的阶段添加约束,以便能够控制综合、实现过程,使设计满足我们需要的运行速度、引脚位置等要求。通常的做法是设计编写约束文件并导入到综合实现工具,在进行

2023-09-21 07:45:57

Vivado设计流程指导手册

Vivado 设计分为 Project Mode 和 Non-project Mode 两种模式,一般简单设计中,我们常用的是 Project Mode。在本手册中,我们将以一个简单的实验案例,一步一步的完成 Vivado的整个设计流程。

2023-09-20 07:37:39

vivado使用误区与进阶资料

想到要写这一系列关于工具和方法学的小文章是在半年多前,那时候Vivado®已经推出两年,陆续也接触了不少客户和他们的设计。我所在的部门叫做“Tools & Methodology

2023-09-20 06:31:14

为什么说Vivado是基于IP的设计?

Vivado是Xilinx公司2012年推出的新一代集成开发环境,它强调系统级的设计思想及以IP为核心的设计理念,突出IP核在数字系统设计中的作用。

2023-09-17 15:37:31 1059

1059

1059

1059

将VIVADO HLS设计移植到CATAPULT HLS平台

电子发烧友网站提供《将VIVADO HLS设计移植到CATAPULT HLS平台.pdf》资料免费下载

2023-09-13 09:12:46 2

2

2

2Vivado使用指南

Vivado界面中也有Add Source的快捷接口,如下图所示:进入Add Source界面后选择对应要添加的文件类型;Constraints:约束文件(含时序约束和物理约束);Design source

2023-09-06 17:55:44

Vivado中BRAM IP的配置方式和使用技巧

FPGA开发中使用频率非常高的两个IP就是FIFO和BRAM,上一篇文章中已经详细介绍了Vivado FIFO IP,今天我们来聊一聊BRAM IP。

2023-08-29 16:41:49 2604

2604

2604

2604

如何给每个RM添加约束?

在常规非DFX(DynamicFunction eXchange)的Vivado设计中,我们可能会碰到给某一个指定的模块添加特定的约束。这时一个简单的方法就是将这些约束单独写在一个.xdc或.tcl

2023-08-17 09:23:39 302

302

302

302

如何给每个RM添加约束?对RM添加约束的步骤有哪些呢?

在常规非DFX(Dynamic Function eXchange)的Vivado设计中,我们可能会碰到给某一个指定的模块添加特定的约束。

2023-08-17 09:22:56 457

457

457

457

关于蜂鸟E203协处理器参考示例的问题

问题一:在vivado中编写约束文件时,由于nice接口的指令是由CPU、协处理器和内存互相发送的,因此是否只需要约束clk和复位信号即可?

问题二:从软件示例程序中可知,数据是由软件输入的,那

2023-08-16 07:24:08

从里可以找到DDR200T的DDR3的配置和约束文件?

在配置DDR200T的DDR3时,一些关键参数的选择在手册中并没有给出,以及.ucf引脚约束文件也没有提供,请问这些信息应该从哪里得到?

2023-08-16 07:02:57

关于蜂鸟FPGA约束文件和MCU200T引脚对应问题

①蜂鸟FPGA约束文件是适用于MCU200T板子吗?

②如果适用,那么在FPGA约束文件中的引脚约束是怎么对应到MCU 200T板子中?

eg:

比如这几条约束是怎么对应到MCU 200T板子中的引脚呢?

2023-08-16 06:58:04

基于 FPGA Vivado 信号发生器设计(附源工程)

今天给大侠带来基于 FPGA Vivado 信号发生器设计,开发板实现使用的是Digilent basys 3。话不多说,上货。

需要源工程可以在以下资料获取里获取。

资料汇总|FPGA软件安装包

2023-08-15 19:57:56

Vivado的Implementation阶段约束报警告?

帮到不经常看群消息的小伙伴,另一方面也算是我们的技术积累。 Q:Vivado的Implementation阶段约束报警告? [Vivado 12-627] No clocks matched

2023-08-08 14:10:48 710

710

710

710vivado软件和modelsim软件的安装方法

本文详细介绍了vivado软件和modelsim软件的安装,以及vivado中配置modelsim仿真设置,每一步都加文字说明和图片。

2023-08-07 15:48:00 1478

1478

1478

1478

如何实现基于FPGA Vivado的74系列IP封装呢?

双击桌面图标打开Vivado 2017.2,或者选择开始>所有程序>Xilinx Design Tools> Vivado 2017.2>Vivado 2017.2;

2023-07-30 09:39:11 399

399

399

399

Vivado调用Modelsim仿真

Modelsim是十分常用的外部仿真工具,在Vivado中也可以调用Modelsim进行仿真,下面将介绍如何对vivado进行配置并调用Modelsim进行仿真,在进行仿真之前需要提前安装Modelsim软件。

2023-07-24 09:04:43 1817

1817

1817

1817

vivado创建工程流程

vivado的工程创建流程对于大部分初学者而言比较复杂,下面将通过这篇博客来讲解详细的vivado工程创建流程。帮助自己进行学习回顾,同时希望可以对有需要的初学者产生帮助。

2023-07-12 09:26:57 1098

1098

1098

1098

Vivado综合阶段什么约束生效?

Vivado综合默认是timing driven模式,除了IO管脚等物理约束,建议添加必要的时序约束,有利于综合逻辑的优化,同时综合后的design里面可以评估时序。

2023-07-03 09:03:19 414

414

414

414用 TCL 定制 Vivado 设计实现流程

需要维护不同的输入文件,例如约束等,输出文件也不是标准网表格式,并且形式各异,导致整体运行时间过长,冗余文件较多。

Vivado 中则统一了约束格式和数据模型,在设计实现的任何一个阶段 都支持 XDC

2023-06-28 19:34:58

如何在Vivado中添加时序约束呢?

今天介绍一下,如何在Vivado中添加时序约束,Vivado添加约束的方法有3种:xdc文件、时序约束向导(Constraints Wizard)、时序约束编辑器(Edit Timing Constraints )

2023-06-26 15:21:11 1834

1834

1834

1834

FPGA时序约束之伪路径和多周期路径

前面几篇FPGA时序约束进阶篇,介绍了常用主时钟约束、衍生时钟约束、时钟分组约束的设置,接下来介绍一下常用的另外两个时序约束语法“伪路径”和“多周期路径”。

2023-06-12 17:33:53 864

864

864

864FPGA时序约束之衍生时钟约束和时钟分组约束

在FPGA设计中,时序约束对于电路性能和可靠性非常重要。在上一篇的文章中,已经详细介绍了FPGA时序约束的主时钟约束。

2023-06-12 17:29:21 1226

1226

1226

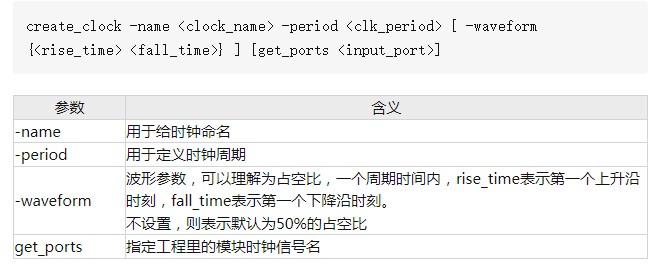

1226FPGA主时钟约束详解 Vivado添加时序约束方法

在FPGA设计中,时序约束的设置对于电路性能和可靠性都至关重要。在上一篇的文章中,已经详细介绍了FPGA时序约束的基础知识。

2023-06-06 18:27:13 6195

6195

6195

6195

约束、时序分析的概念

很多人询问关于约束、时序分析的问题,比如:如何设置setup,hold时间?如何使用全局时钟和第二全局时钟(长线资源)?如何进行分组约束?如何约束某部分组合逻辑?如何通过约束保证异步时钟域之间

2023-05-29 10:06:56 371

371

371

371

Vivado综合参数设置

如果你正在使用Vivado开发套件进行设计,你会发现综合设置中提供了许多综合选项。这些选项对综合结果有着潜在的影响,而且能够提升设计效率。为了更好地利用这些资源,需要仔细研究每一个选项的功能。本文将要介绍一下Vivado的综合参数设置。

2023-05-16 16:45:50 1856

1856

1856

1856

Vivado布线和生成bit参数设置

本文主要介绍Vivado布线参数设置,基本设置方式和vivado综合参数设置基本一致,将详细说明如何设置布线参数以优化FPGA设计的性能,以及如何设置Vivado压缩BIT文件。

2023-05-16 16:40:45 2955

2955

2955

2955

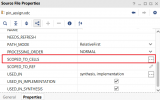

简述Vivado中的Elaborate的作用

在Vivado的界面中,有个RTL ANALYSIS->Open Elaborated Design的选项,可能很多工程师都没有使用过。因为大家基本都是从Run Synthesis开始的。

2023-05-05 16:00:18 803

803

803

803

在Vivado中实现ECO功能

关于 Tcl 在 Vivado中的应用文章从 Tcl 的基本语法和在 Vivado 中的 应用展开,继上篇《用 Tcl 定制 Vivado 设计实现流程》介绍了如何扩展甚 至是定制 FPGA

2023-05-05 15:34:52 1612

1612

1612

1612

Vivado使用进阶:读懂用好Timing Report

《XDC 约束技巧》系列中讨论了XDC 约束的设置方法、约束思路和一些容易混淆的地方。我们提到过约束是为了设计服务,写入 Vivado中 的 XDC 实际上就是用户设定的目标,Vivado

2023-05-04 11:20:31 2368

2368

2368

2368

Xilinx FPGA时序约束设计和分析

在进行FPGA的设计时,经常会需要在综合、实现的阶段添加约束,以便能够控制综合、实现过程,使设计满足我们需要的运行速度、引脚位置等要求。通常的做法是设计编写约束文件并导入到综合实现工具,在进行

2023-04-27 10:08:22 768

768

768

768Vivado生成IP核

在vivado生成ip核后缺少一大片文件,之前是可以用的,中途卸载过Modelsim,用vivado打开过ISE工程,因为工程中很多IP核不能用所以在重新生成过程中发现了这个问题,还请大神告知是怎么回事?

2023-04-24 23:42:21

i.MX8M Plus UART参考手册引脚复用表中未显示的其他引脚的ALT模式是什么?

在 8M Plus 上,引脚配置器显示的 UART 信号可用引脚数量是参考手册中的引脚多路复用表的两倍。那么,哪一个是正确的,如果引脚配置器是正确的,那么参考手册引脚复用表中未显示的其他引脚的 ALT 模式是什么?以 UART4 uart_rx 为例。

2023-04-18 07:21:56

Vivado逻辑分析仪使用教程

,用户设置的调试信息会以Tcl XDC调试命令的形式保存到XDC约束文件中,在实现阶段,Vivado会读取这些XDC调试命令,并在布局布线时加入这些ILA IP核。此时,我们所做出的所有的更改和设置,都还

2023-04-17 16:33:55

Tcl在Vivado中的应用

Xilinx的新一代设计套件Vivado相比上一代产品 ISE,在运行速度、算法优化和功能整合等很多方面都有了显著地改进。但是对初学者来说,新的约束语言 XDC 以及脚本语言 Tcl 的引入则成为

2023-04-15 09:43:09 956

956

956

956Vivado 开发软件下板验证教程

打开I/O planning。打开后,在界面下方打开I/O Ports。在这个界面,我们需要分配引脚以及电平标准才能下板,此次实验,我们以SANXIN-B04为基础进行下板。管脚约束如下表:分配好之后

2023-04-14 20:18:05

XDC约束技巧之I/O篇(下)

继《XDC 约束技巧之 I/O 篇(上)》详细描述了如何设置 Input 接口 约束后,我们接着来聊聊怎样设置 Output 接口约束,并分析 UCF 与 XDC 在接口约束上的区别。

2023-04-10 11:00:42 623

623

623

623XDC约束技巧之I/O篇(上)

《XDC 约束技巧之时钟篇》中曾对 I/O 约束做过简要概括,相比较而言,XDC 中的 I/O 约束虽然形式简单,但整体思路和约束方法却与 UCF 大相径庭。加之 FPGA 的应用特性决定了其在接口

2023-04-06 09:53:30 729

729

729

729使用Vivado点量led灯-Vivado基本开发流程

管脚约束文件。也可直接通过编写管脚约束文件直接进行管脚约束。语法如下:管脚约束如下:set_property PACKAGE_PIN "引脚编号" [get_ports “端口名称

2023-04-05 23:21:24

XDC约束技巧之CDC篇

上一篇《XDC 约束技巧之时钟篇》介绍了 XDC 的优势以及基本语法,详细说明了如何根据时钟结构和设计要求来创建合适的时钟约束。我们知道 XDC 与 UCF 的根本区别之一就是对跨时钟域路径(CDC

2023-04-03 11:41:42 1135

1135

1135

1135XDC约束技巧之时钟篇

Xilinx的新一代设计套件Vivado中引入了全新的约束文件 XDC,在很多规则和技巧上都跟上一代产品 ISE 中支持的 UCF 大不相同,给使用者带来许多额外挑战。Xilinx 工具专家告诉你,其实用好 XDC 很容易,只需掌握几点核心技巧,并且时刻牢记:XDC 的语法其实就是 Tcl 语言。

2023-03-28 09:51:10 1802

1802

1802

1802 电子发烧友App

电子发烧友App

评论