MotorControl Workbench 5.4.4生成代码只支持增量编码器和霍尔编码器。怎么改绝对值编码器

?分别需要改哪几个函数?请问一下,大家有没有这方面的例子?

2024-03-14 06:21:52

RK3568驱动指南|驱动基础进阶篇-进阶8 内核运行ko文件总结

2024-01-31 14:58:59 180

180

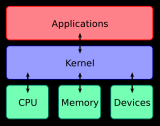

我们常说,看一个系统是不是自研,就看它的内核,常见的内核分为:宏内核和微内核,当然还有两者结合体,他们到底有什么区别? 白话宏内核和微内核 有一天,你结婚了,你和你的爱人住一套房子,你的父母和你爱人

2024-01-30 16:43:10 145

145

电子发烧友网站提供《使用P4和Vivado工具简化数据包处理设计.pdf》资料免费下载

2024-01-26 17:49:11 0

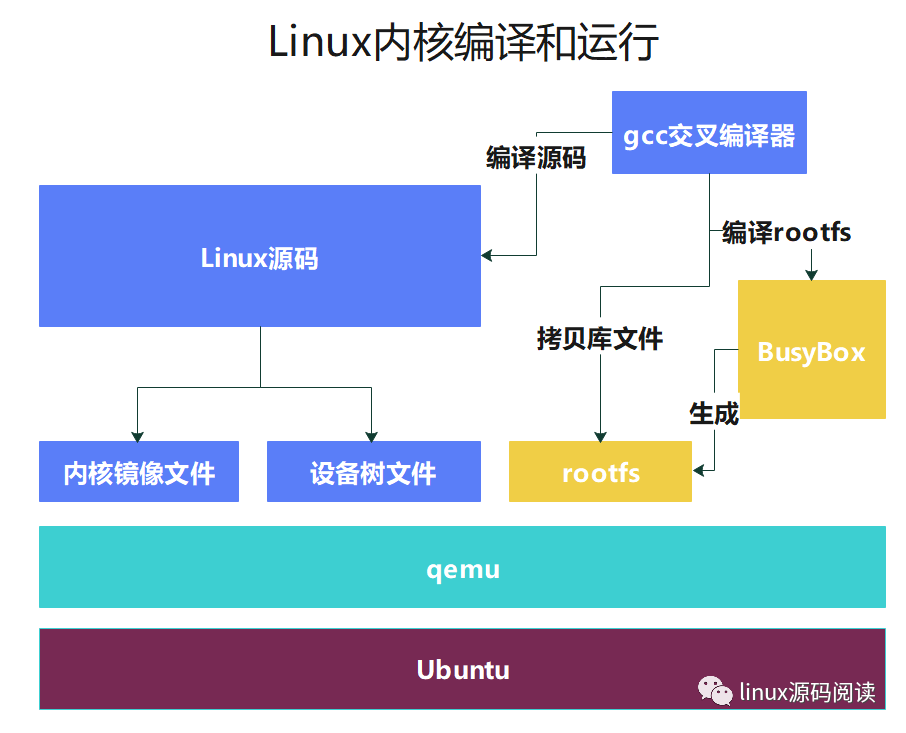

0 Linux内核主要由以下几个部分组成: 进程管理:Linux内核负责管理和调度系统中的进程。它通过进程调度算法来决定哪个进程在什么时间运行以及如何分配系统资源。 内存管理:Linux内核负责管理系统

2024-01-22 14:34:43 636

636 前面我们已经介绍了内核注意到信号的到来,调用相关函数更新进程描述符以便进程接收处理信号。但是,如果目标进程此时没有运行,内核则推迟传递信号。现在,我们看看内核如何处理进程挂起的信号。

2024-01-17 09:51:05 391

391

在Vivado中禁止自动生成BUFG(Buffered Clock Gate)可以通过以下步骤实现。 首先,让我们简要了解一下什么是BUFG。BUFG是一个时钟缓冲器,用于缓冲输入时钟信号,使其更稳

2024-01-05 14:31:06 454

454 有些时候在写完代码之后呢,Vivado时序报红,Timing一栏有很多时序问题。

2024-01-05 10:18:36 291

291 Vivado在前一段时间更新了2023.2版本,经过一段时间的使用这个版本还是很丝滑的,用起来挺舒服。

2024-01-02 09:39:41 828

828

vivado出现安装问题刚开始还以为是安装路径包含中文空格了,重装的注意了一下,发现还是这个问题。。。。后来又一顿操作猛如虎,终于发现了问题。出这个问题的原因是vivado压缩包解压的路径包含中文了把解压文件放到不含中文的地方,再重新安装,安装路径也不能含中文。然后。。。。。然后就安装完成了

2023-12-22 10:56:33 0

0 vivado软件的安装教程以及license

2023-12-21 19:50:00

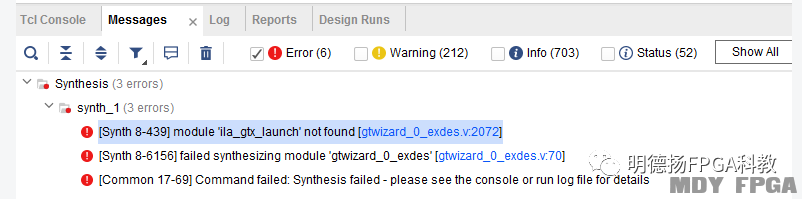

【关键问题!!!!重要!!!】VIVADO会在MESSAGE窗口出提示很多错误和警告信息!

2023-12-15 10:11:22 666

666

文章是基于Vivado的 2017.1的版本,其他版本都大同小异。 首先在Vivado界面的右侧选择IP Catalog 选项。

2023-12-05 15:05:02 317

317 近几天调试开发板,主芯片是XC7A100T,用Vivado给开发板下载bit文件,正常工作。

2023-12-04 09:54:28 339

339 请问ADSP21489可运行几个2000阶的FIR滤波器?

2023-11-29 07:01:28

在使用JTAG仿真器在vivado环境下抓信号时,报如下错误:

2023-11-14 10:37:20 1052

1052 补丁和不断完善代码,BPF程序变成了一个更通用的执行引擎,可以完成多种任务。简单来说,BPF提供了一种在各种内核时间和应用程序事件发生时运行一小段程序的机制。其允许内核在系统和应用程序事件发生时运行一小段程序,这样就将内核变得完全可编程,允许用户定制和控制他们的

2023-11-10 10:34:39 410

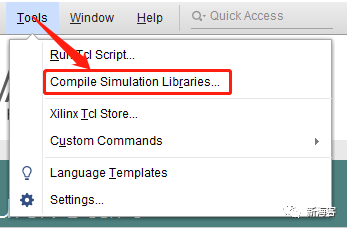

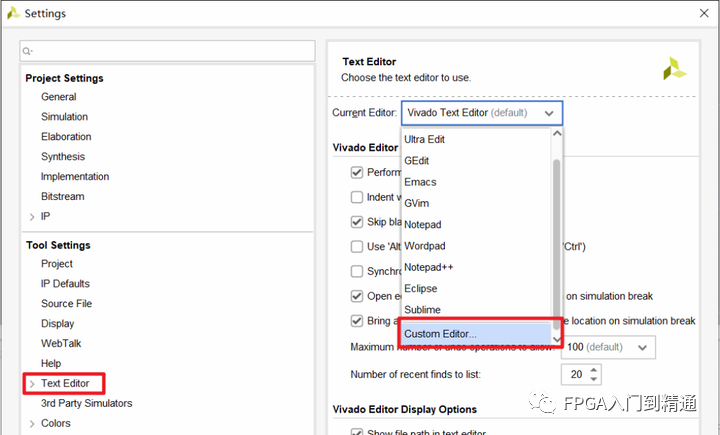

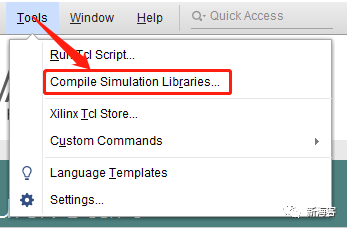

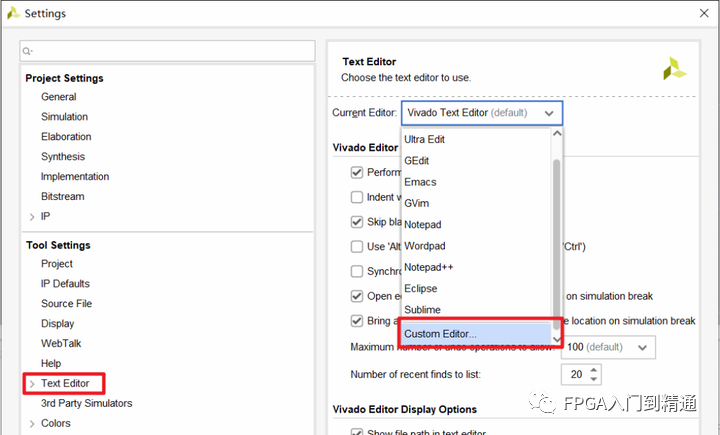

410 Vivado自带的仿真工具在一些基本功能的仿真测试时是可以满足的,但如果你的工程较为庞大,那么自带的仿真工具将有些勉强,除了在数据输出方面的卡顿,在仿真速度上也可能无法接受,这里可以借助第三方仿真工具进行工程仿真测试,Vivado2018各版本支持的仿真工具见下。

2023-11-08 14:47:30 512

512

stm32f103mini板子芯片改mm32f103不运行是什么原因,是不是硬件还要修改

2023-11-02 07:40:57

《Vivado Design Suite 用户指南:编程和调试》 文档涵盖了以下设计进程: 硬件、IP 和平台开发 : 为硬件平台创建 PL IP 块、创建 PL 内核、功能仿真以及评估 AMD

2023-10-25 16:15:02 352

352

AT32 工程在 M3 内核芯片上运行进入硬件错误处理函数(HardFault_Handler)?

2023-10-20 06:48:18

内核是使用Xilinx Vivado设计套件交付的经过全面验证的解决方案设计。此外,还提供了Verilog示例设计。

2023-10-16 10:57:17 358

358

符合实际情况的,以此进行优化。 加载位置 内核镜像可以由 kernel 自解压,也可以由 uboot 进行解压。 对于 kernel 自解压的情况,如果压缩过的 kernel 与解压后的 kernel

2023-10-04 15:07:00 335

335 module taints kernel 几个可能原因: 模块没有声明 GPL 协议 当前linux内核版本和编译模块使用的内核版本不一致 使用内核源代码未包含的树外模块 printk和printf 在内核中的打印函数是 printk , printk 和 printf 的行

2023-09-26 16:58:48 460

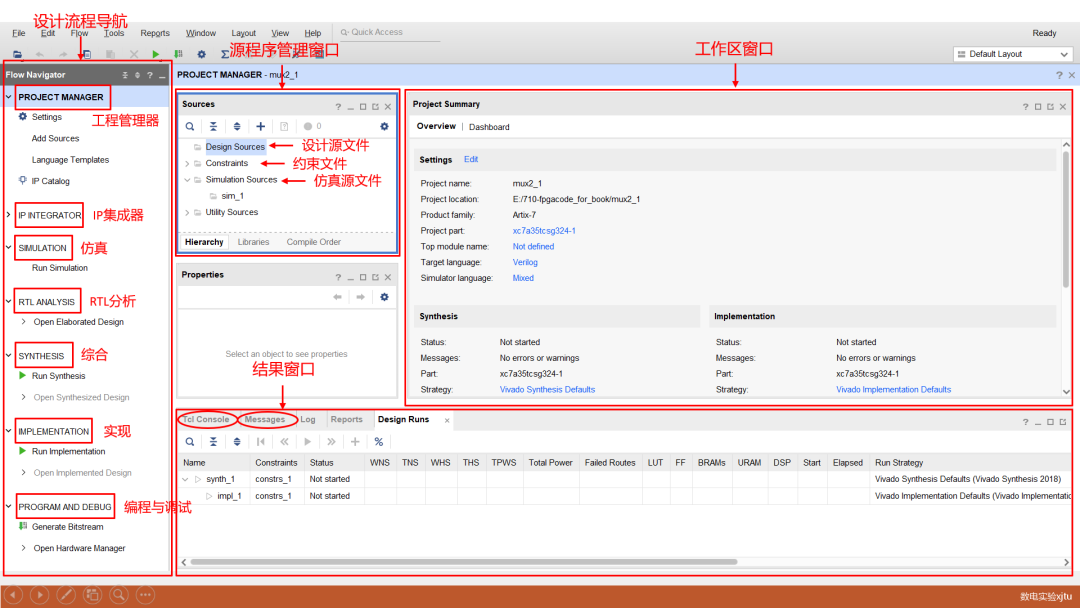

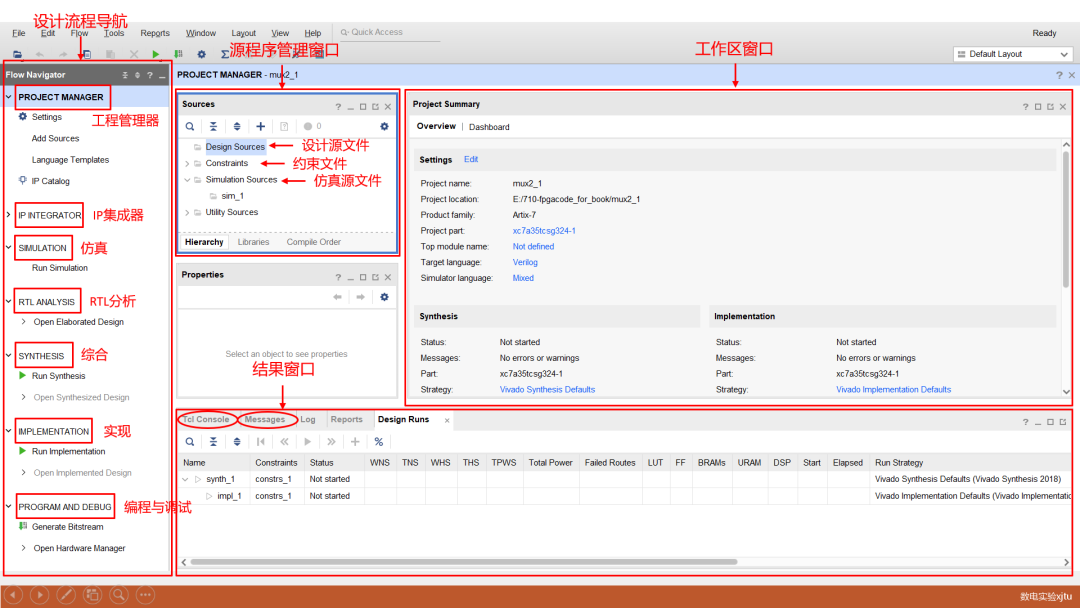

460 Vivado 设计分为 Project Mode 和 Non-project Mode 两种模式,一般简单设计中,我们常用的是 Project Mode。在本手册中,我们将以一个简单的实验案例,一步一步的完成 Vivado的整个设计流程。

2023-09-20 07:37:39

想到要写这一系列关于工具和方法学的小文章是在半年多前,那时候Vivado®已经推出两年,陆续也接触了不少客户和他们的设计。我所在的部门叫做“Tools & Methodology

2023-09-20 06:31:14

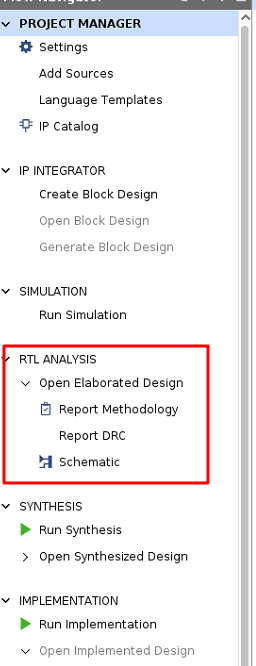

Vivado设计主界面,它的左边是设计流程导航窗口,是按照FPGA的设计流程设置的,只要按照导航窗口一项一项往下进行,就会完成从设计输入到最后下载到开发板上的整个设计流程。

2023-09-17 15:40:17 1491

1491

Vivado是Xilinx公司2012年推出的新一代集成开发环境,它强调系统级的设计思想及以IP为核心的设计理念,突出IP核在数字系统设计中的作用。

2023-09-17 15:37:31 1059

1059

电子发烧友网站提供《Vivado设计套件用户指南(设计流程概述).pdf》资料免费下载

2023-09-15 09:55:07 1

1 电子发烧友网站提供《Vivado Design Suite教程:动态功能交换.pdf》资料免费下载

2023-09-14 15:13:43 0

0 电子发烧友网站提供《Vivado设计套件用户指南:使用Tcl脚本.pdf》资料免费下载

2023-09-14 14:59:39 0

0 电子发烧友网站提供《Vivado ML版中基于ML的路由拥塞和延迟估计.pdf》资料免费下载

2023-09-14 11:41:08 0

0 电子发烧友网站提供《Vivado设计套件Tcl命令参考指南.pdf》资料免费下载

2023-09-14 10:23:05 1

1 电子发烧友网站提供《Vivado设计套件用户指南.pdf》资料免费下载

2023-09-14 09:55:18 2

2 电子发烧友网站提供《Vivado Design Suite用户指南:使用约束.pdf》资料免费下载

2023-09-13 15:48:39 0

0 电子发烧友网站提供《Vivado Design Suite用户指南:综合.pdf》资料免费下载

2023-09-13 15:47:40 0

0 电子发烧友网站提供《Vivado设计套件用户指南:逻辑仿真.pdf》资料免费下载

2023-09-13 15:46:41 0

0 电子发烧友网站提供《Vivado Design Suite用户指南:使用Tcl脚本.pdf》资料免费下载

2023-09-13 15:26:43 0

0 电子发烧友网站提供《Vivado设计套件用户:使用Vivado IDE的指南.pdf》资料免费下载

2023-09-13 15:25:36 3

3 电子发烧友网站提供《Vivado Design Suite用户指南:I/O和时钟规划.pdf》资料免费下载

2023-09-13 15:10:58 0

0 电子发烧友网站提供《Vivado Design Suite用户指南:编程和调试.pdf》资料免费下载

2023-09-13 14:47:21 0

0 电子发烧友网站提供《Vivado设计套件用户指南:编程和调试.pdf》资料免费下载

2023-09-13 11:37:38 0

0 电子发烧友网站提供《UltraFast Vivado HLS方法指南.pdf》资料免费下载

2023-09-13 11:23:19 0

0 电子发烧友网站提供《Vivado隔离验证器用户指南.pdf》资料免费下载

2023-09-13 11:11:15 0

0 电子发烧友网站提供《将VIVADO HLS设计移植到CATAPULT HLS平台.pdf》资料免费下载

2023-09-13 09:12:46 2

2 Xilinx官网:www.xilinx.com; 2)选中Support菜单下的Downloads&Licensing;3)选择对应系统;2.2Vivado安装(2015.4为例)1)运行

2023-09-06 17:55:44

在给Vivado中的一些IP核进行配置的时候,发现有Shared Logic这一项,这里以Tri Mode Ethernet MAC IP核为例,如图1所示。

2023-09-06 17:05:12 528

528

FPGA开发中使用频率非常高的两个IP就是FIFO和BRAM,上一篇文章中已经详细介绍了Vivado FIFO IP,今天我们来聊一聊BRAM IP。

2023-08-29 16:41:49 2604

2604

:Vivado使用‘/’);

3) 在Tcl命令框中,输入命令:source ./ Oscilloscope.tcl。输入完毕按回车,运行Tcl;

4) 等待Tcl综合、实现、生成比特流文件;

5) 在

2023-08-17 19:31:54

新人小白求助各位大佬,在vivado中配置了e203项目,但是在仿真阶段发现,PC值直到仿真结束都是0,x3寄存器的值为X,但是ITCM中读入了指令,不知道在哪个环节出了问题,希望大佬可以为我指点迷津。

2023-08-12 07:56:14

} [get_drc_checks NSTD-1].NOTE: When using the Vivado Runs infrastructure (e.g. launch_runs Tcl command), add

2023-08-12 07:54:28

原来仿真使用的是vivado simulator,最近将vivado的仿真器改成modelsim,发现仿真的时候modelsim的transcript没法打印出e203实时运行的信息。请问要在modelsim中设置什么地方吗

2023-08-11 09:47:12

帮到不经常看群消息的小伙伴,另一方面也算是我们的技术积累。 Q:Vivado的Implementation阶段约束报警告? [Vivado 12-627] No clocks matched

2023-08-08 14:10:48 710

710 本文详细介绍了vivado软件和modelsim软件的安装,以及vivado中配置modelsim仿真设置,每一步都加文字说明和图片。

2023-08-07 15:48:00 1478

1478

Vivado IP核提供了强大的FIFO生成器,可以通过图形化配置快速生成FIFO IP核。

2023-08-07 15:36:28 1616

1616

双击桌面图标打开Vivado 2017.2,或者选择开始>所有程序>Xilinx Design Tools> Vivado 2017.2>Vivado 2017.2;

2023-07-30 09:39:11 399

399

电子发烧友网报道(文/李弯弯)日前,在2023世界半导体大会暨南京国际半导体博览会上,高通全球副总裁孙刚发表演讲时谈到,目前高通能够支持参数超过10亿的模型在终端上运行,未来几个月内超过100亿参数

2023-07-26 00:15:00 1058

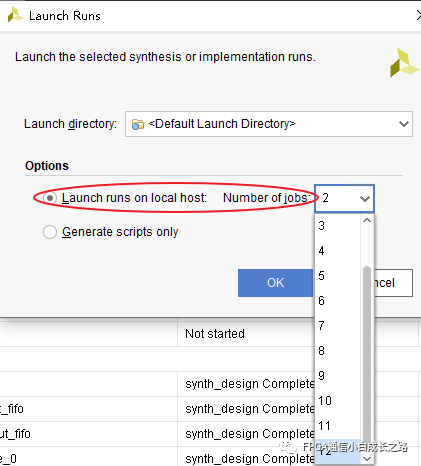

1058 Vivado中对工程进行综合时,会弹出如下对话框

2023-07-24 15:28:54 489

489

Modelsim是十分常用的外部仿真工具,在Vivado中也可以调用Modelsim进行仿真,下面将介绍如何对vivado进行配置并调用Modelsim进行仿真,在进行仿真之前需要提前安装Modelsim软件。

2023-07-24 09:04:43 1817

1817

vivado开发软件自带了仿真工具,下面将介绍vivado的仿真流程,方便初学者进行仿真实验。

2023-07-18 09:06:59 2131

2131

vivado的工程创建流程对于大部分初学者而言比较复杂,下面将通过这篇博客来讲解详细的vivado工程创建流程。帮助自己进行学习回顾,同时希望可以对有需要的初学者产生帮助。

2023-07-12 09:26:57 1098

1098

使用“时钟校准去歪斜”时,在 Vivado 中会显示下列消息以指明是否启用该功能特性

2023-07-07 14:14:50 347

347

Linux操作系统是当今世界上最为广泛使用的开源操作系统之一,内核则是一个操作系统的核心和灵魂所在。对于一名Linux驱动开发者来说,了解Linux内核的运行机制和Linux内核提供的一些关键功能(如虚拟内存管理、进程管理、文件系统、网络协议栈等)都是我们日常工作和学习的重点。

2023-07-06 11:46:41 1041

1041

Vivado综合默认是timing driven模式,除了IO管脚等物理约束,建议添加必要的时序约束,有利于综合逻辑的优化,同时综合后的design里面可以评估时序。

2023-07-03 09:03:19 414

414 IDE 上运行 Tcl 脚本主要有以下几个渠道。

Tcl Console

Vivado IDE 的最下方有一个 Tcl Console,在运行过程中允许用户输入 Tcl/XDC 命令或是 source

2023-06-28 19:34:58

今天介绍一下,如何在Vivado中添加时序约束,Vivado添加约束的方法有3种:xdc文件、时序约束向导(Constraints Wizard)、时序约束编辑器(Edit Timing Constraints )

2023-06-26 15:21:11 1834

1834

FPGA开发过程中,vivado和quartus等开发软件都会提供时序报告,以方便开发者判断自己的工程时序是否满足时序要求。

2023-06-23 17:44:00 531

531

想让Linux内核代码跑起来,得先搭建编译和运行代码的环境。

2023-06-23 11:56:00 322

322

在仿真Vivado IP核时分两种情况,分为未使用SECURE IP核和使用了SECURE IP核。

2023-06-20 14:23:57 622

622

Vivado Schematic中的实线和虚线有什么区别?

2023-06-16 16:53:42 698

698

电子发烧友网站提供《为EBAZ4205创建Xilinx Vivado板文件.zip》资料免费下载

2023-06-16 11:41:02 1

1 电子发烧友网站提供《在Artix 7 FPGA上使用Vivado的组合逻辑与顺序逻辑.zip》资料免费下载

2023-06-15 09:14:49 0

0 在仿真Vivado IP核时分两种情况,分为未使用SECURE IP核和使用了SECURE IP核。

2023-06-06 14:45:43 1240

1240

Vivado Schematic中的实线和虚线有什么区别?

2023-06-06 11:13:39 670

670

我目前正在评估 imxrt1170 的新产品,但我无法获得任何在 m4 内核上运行的示例。所有示例都在 m7 上完美运行,但由于未知原因,它们不会在 m4 上运行。事实上,mculink 没有连接

2023-05-18 08:09:29

Vivado 软件提供了HDL编写中常用的示例,旨在帮助初学者更好地理解和掌握HDL编程,这里分享一下verilog代码示例。

2023-05-16 16:58:06 627

627 如果你正在使用Vivado开发套件进行设计,你会发现综合设置中提供了许多综合选项。这些选项对综合结果有着潜在的影响,而且能够提升设计效率。为了更好地利用这些资源,需要仔细研究每一个选项的功能。本文将要介绍一下Vivado的综合参数设置。

2023-05-16 16:45:50 1856

1856

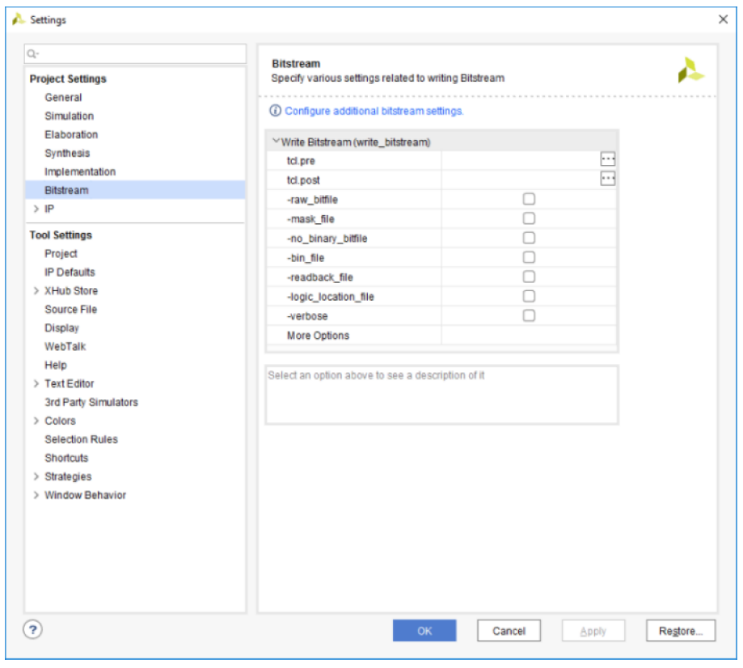

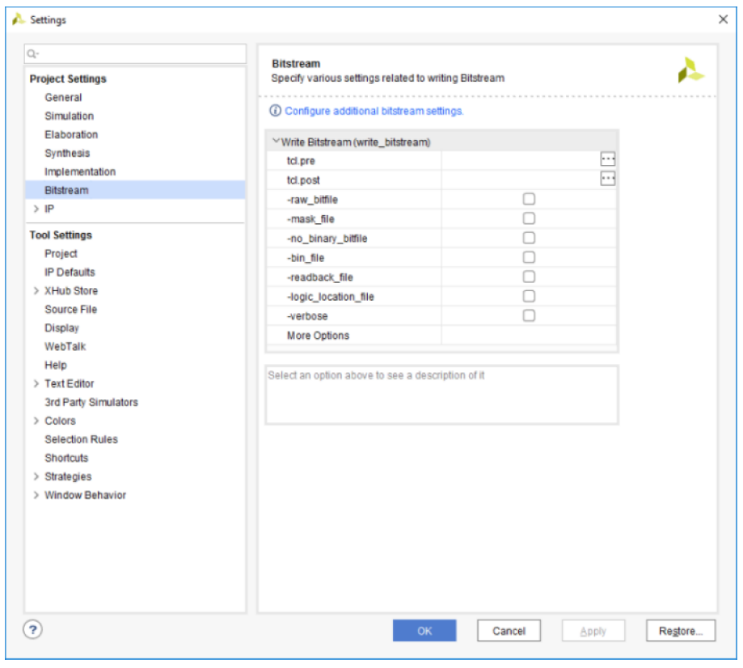

本文主要介绍Vivado布线参数设置,基本设置方式和vivado综合参数设置基本一致,将详细说明如何设置布线参数以优化FPGA设计的性能,以及如何设置Vivado压缩BIT文件。

2023-05-16 16:40:45 2955

2955

Vivado是一个非常强大的工具,但是在一些方面可能不能完全满足我们的需求,比如代码编辑器的功能。幸运的是,Vivado允许我们关联第三方编辑器来扩展其代码编辑器的功能。本文将介绍如何配置Vivado与第三方编辑器一起使用,并提供一些实用技巧和建议。

2023-05-16 16:36:18 771

771

有一天使用Vivado调用questasim(modelsim估计也一样),仿真报错

2023-05-08 17:12:56 1758

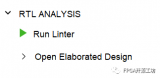

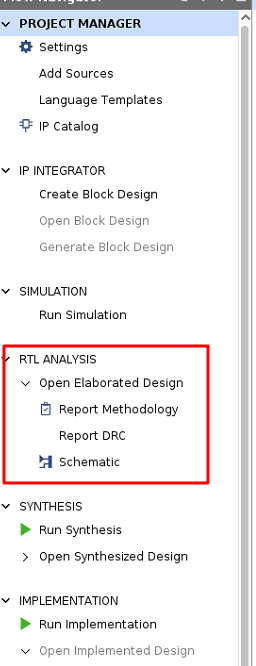

1758 在Vivado的界面中,有个RTL ANALYSIS->Open Elaborated Design的选项,可能很多工程师都没有使用过。因为大家基本都是从Run Synthesis开始的。

2023-05-05 16:00:18 803

803

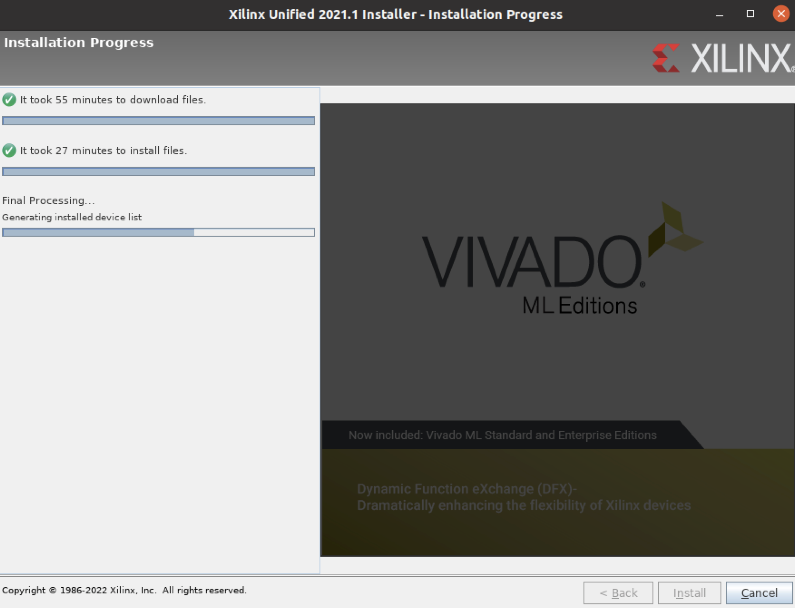

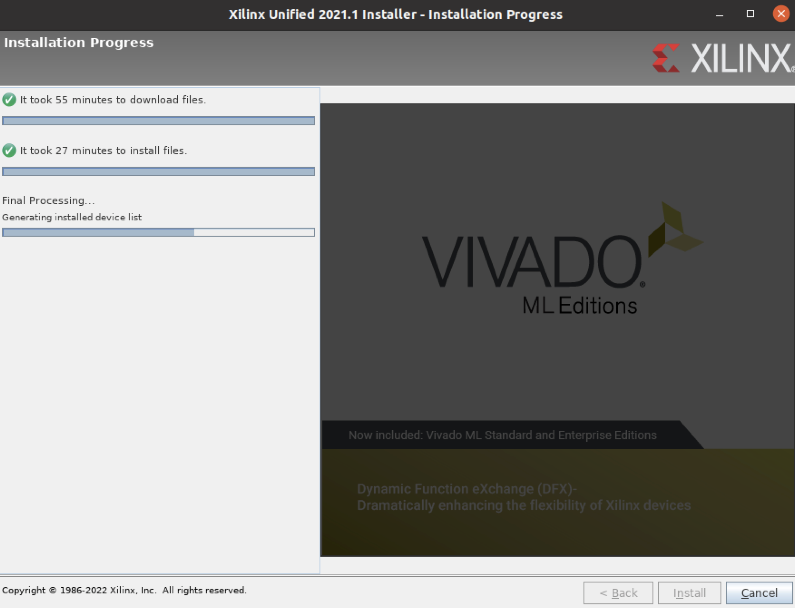

在ubuntu上安装vivado2021.1时,一直卡在最后一步:generating installed device list

安装其他版本也出现过该问题。

2023-05-05 15:51:38 1672

1672

关于 Tcl 在 Vivado中的应用文章从 Tcl 的基本语法和在 Vivado 中的 应用展开,继上篇《用 Tcl 定制 Vivado 设计实现流程》介绍了如何扩展甚 至是定制 FPGA

2023-05-05 15:34:52 1612

1612

今天推出Xilinx已发布的《Vivado使用误区与进阶》系列:用TCL定制Vivado设计实现流程。

2023-05-05 09:44:46 674

674

《XDC 约束技巧》系列中讨论了XDC 约束的设置方法、约束思路和一些容易混淆的地方。我们提到过约束是为了设计服务,写入 Vivado中 的 XDC 实际上就是用户设定的目标,Vivado

2023-05-04 11:20:31 2368

2368

在vivado生成ip核后缺少一大片文件,之前是可以用的,中途卸载过Modelsim,用vivado打开过ISE工程,因为工程中很多IP核不能用所以在重新生成过程中发现了这个问题,还请大神告知是怎么回事?

2023-04-24 23:42:21

你好是否有机会让 busfreq 驱动程序在主线内核上运行?在我看来,如果没有它,我无法以高于 1M 波特的速度可靠地运行 UART...(我正在寻找 3M 波特串行通信)

2023-04-18 10:30:12

Xilinx的新一代设计套件Vivado相比上一代产品 ISE,在运行速度、算法优化和功能整合等很多方面都有了显著地改进。但是对初学者来说,新的约束语言 XDC 以及脚本语言 Tcl 的引入则成为

2023-04-15 09:43:09 956

956 Vivado是Xilinx推出的可编程逻辑设备(FPGA)软件开发工具套件,提供了许多TCL命令来简化流程和自动化开发。本文将介绍在Vivado中常用的TCL命令,并对其进行详细说明,并提供相应的操作示例。

2023-04-13 10:20:23 1544

1544 ACCYKITZYBOW/VIVADO

2023-03-30 12:05:04

VIVADO DEBUG FLOATING LICENSE

2023-03-30 12:04:13

VIVADO DEBUG NODE-LOCKED LICENSE

2023-03-30 12:04:13

VIVADO DEBUG FLOATING LICENSE

2023-03-30 12:04:13

VIVADO DEBUG NODE-LOCKED LICENSE

2023-03-30 12:04:13

今天我要跟大家分享一下Linux内核的重要性。内核就像Linux系统运行的大心脏,对系统的运行起到了至关重要的作用。那么Linux内核到底难不难学呢?今天我就大概和大家科普一下,后期还会向大家

2023-03-24 15:16:40 558

558

内核是与计算机硬件接口的易替换软件的最低级别。它负责将所有以“用户模式”运行的应用程序连接到物理硬件,并允许称为服务器的进程使用进程间通信(IPC)彼此获取信息。

2023-03-24 11:23:33 1510

1510

电子发烧友App

电子发烧友App

硬声App

硬声App

145

145

636

636 391

391

454

454 0

0 317

317 410

410 512

512

352

352

358

358

335

335 460

460 1491

1491

1059

1059

0

0 0

0 2

2 528

528

2604

2604

710

710 1478

1478

399

399

1058

1058 1817

1817

1098

1098

1041

1041

414

414 1834

1834

0

0 1856

1856

2955

2955

771

771

803

803

1672

1672

1612

1612

2368

2368

956

956 1544

1544 558

558

1510

1510

评论