用于开发过程中模型的静态检查,包括规范检查、复杂度度量,提供MAAB、HIS、CG、MISRA_AC_SLSF、MISRA_AC_TL、dSPACE标准规范及检查,

2024-03-01 11:29:03

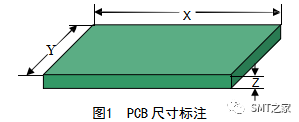

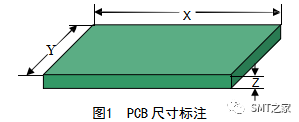

一站式PCBA智造厂家今天为大家讲讲pcb layout设计需要注意哪些细节?pcb layout设计规范。Printed Circuit Board (PCB)是一种电子零件,它是连接

2024-02-23 09:19:41 142

142 工业机器人在恶劣条件下运行,即使设计时进行完善的设计规范,维护率可以降低,但是,仍必须定期进行常规检查和预防性维护。

2024-01-26 11:47:26 136

136

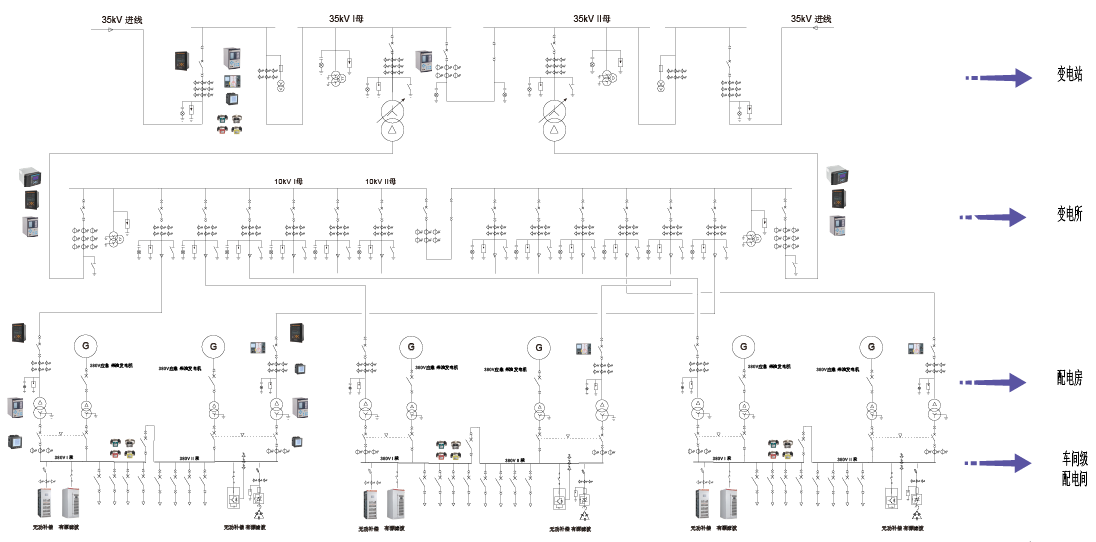

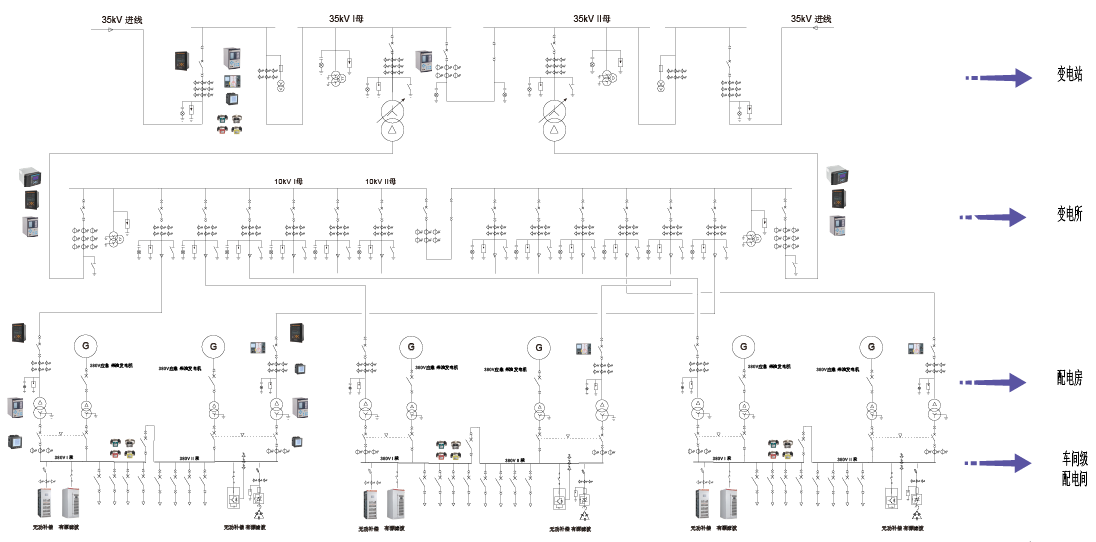

的隐患,快速排除故障,保障整个药企厂区生产供电的稳定、可靠。 2、参考标准 GB 50457-2019 《医药工业洁净厂房设计规范》 GB 50052-2009 《供配电系统设计规范》 GB 50054-2011 《低压配电设计规范》 GB/T 14285-2006 《继电保护和安全自动装置技术规

2024-01-17 15:19:23 92

92

本规范规定了我公司 PCB 设计流程和设计原则,为 PCB 设计人员提供必须遵循的规则和约定。

2024-01-12 11:06:26 690

690

电子发烧友网站提供《华为印制电路板(PCB)设计规范.pdf》资料免费下载

2024-01-02 10:44:52 11

11 电子发烧友网站提供《印制电路板设计规范.pdf》资料免费下载

2024-01-02 10:37:18 0

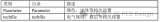

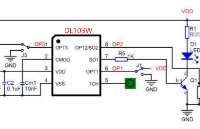

0 单通道双输出LED灯光控制触摸芯片DL103W应用之PCB设计规范,详细介绍了相关的设计注意事项

2023-12-27 09:12:12 297

297

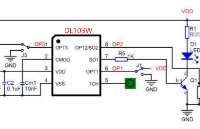

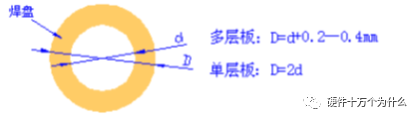

PCB 焊盘与孔设计工艺规范 1. 目的 规范产品的PCB焊盘设计工艺,规定PCB焊盘设计工艺的相关参数,使得PCB 的设计满足可生产性、可测试性、安规、EMC、EMI 等的技术规范要求,在产品

2023-12-22 19:40:02 505

505

MC(Electromagnetic Compatibility)设计规范是确保电子设备在电磁环境中正常工作并减少电磁干扰的重要标准。本规范旨在为电子设备的EMC设计提供指导,以确保其符合相关标准和法规,提高设备的电磁兼容性。

2023-12-17 17:36:42 574

574 我国对于膨胀节有着相关规定,例如《采暖通风与空气调节设计规范》4.8.17条;采暖管道必须计算其热膨胀。当利用管段的自然补偿不能满足要求时,应设置补偿器。其它如电力化工设计规范都有此要求,甚至有的还要求用软件进行计算,如电厂设计院一般用GLIF,而化工设计院一般用Caesar 等等。

2023-12-04 16:25:40 506

506

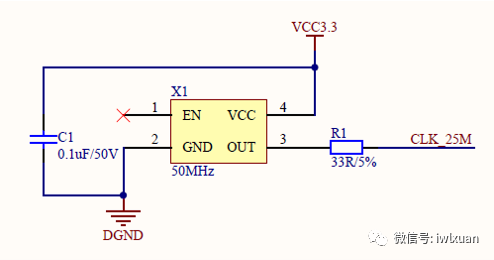

PCB 布线与布局1 PCB 布线与布局隔离准则:强弱电流隔离、大小电压隔离,高低频率隔离、输入输出隔离、数字模拟隔离、输入输出隔离,分界标准为相差一个数量级。隔离方法包括:空间远离、地线隔开。2 晶振要尽量靠近 IC,且布线要较粗3 晶振外壳接地4 时钟布线经连接器输出时,连接器上的插针要在时钟线插针周围布满接地插针5 让模拟和数字电路分别拥有自己的电源和地线通路,在可能的情况下,应尽量加宽这两部分电路的电源与地线或采用分开

2023-11-10 17:11:37 2

2 一、查找表(Look-Up-Table)的原理与结构

采用这种结构的PLD芯片我们也可以称之为FPGA:如altera的ACEX、APEX系列、Xilinx的Spartan、Virtex系列等

2023-11-03 11:18:38

代码规范化如何学习,单片机也要求规范化么?

2023-10-12 07:19:17

非常详细的PCB设计规范

2023-10-11 18:06:41 26

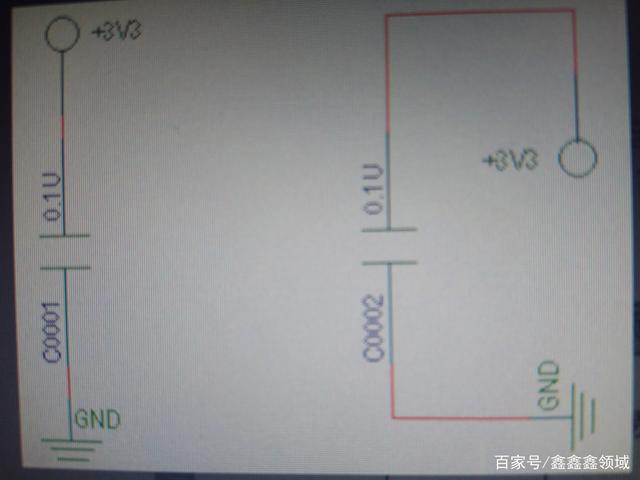

26 如果时钟线有过孔,在过孔的相邻位置,在第二层(地层)和第三层(电源层)之间加一个旁路电容、如图2.5-1所示,以确保时钟线换层后,参考层(相邻层)的高频电流的回路连续。

2023-10-09 15:25:48 222

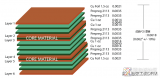

222 的特殊叠层结构特性阻抗的控制

射频PCB与数模混合类PCB的布线规则和技巧射频PCB与数模混合类PCB布线完成后的收尾处理PCB板级的ESD处理方法和技巧

PCB板级的EMC/EMI处理方法和技巧PCB中的DFM 设计

FPC柔性PCB设计设计规范的必要性

2023-09-27 07:54:33

一、OpenHarmony应用开发涉及的主要因素

二、OpenHarmony应用开发UX设计规范

UX设计规范的主要内容与部分图标示例

2.OpenHarmony应用设计原则

设计原则,当为

2023-09-25 15:03:24

详述罗列PCBlayout各条款规则

2023-09-20 07:34:42

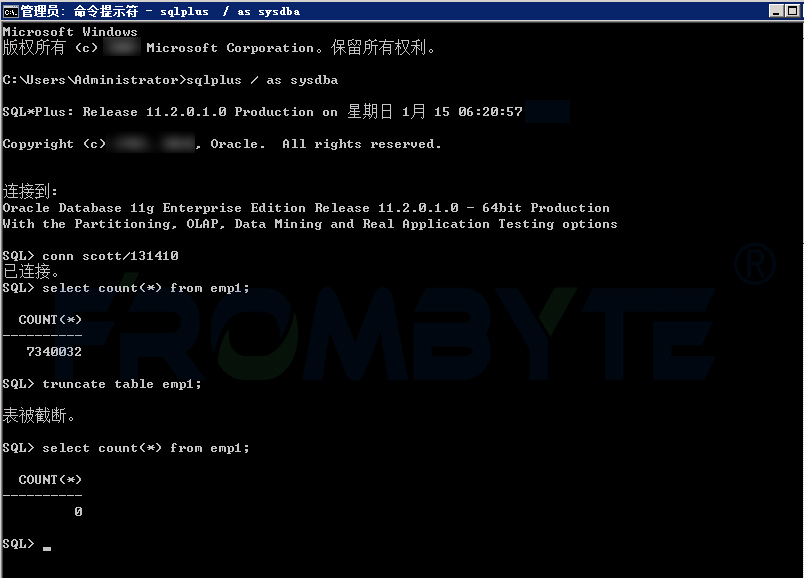

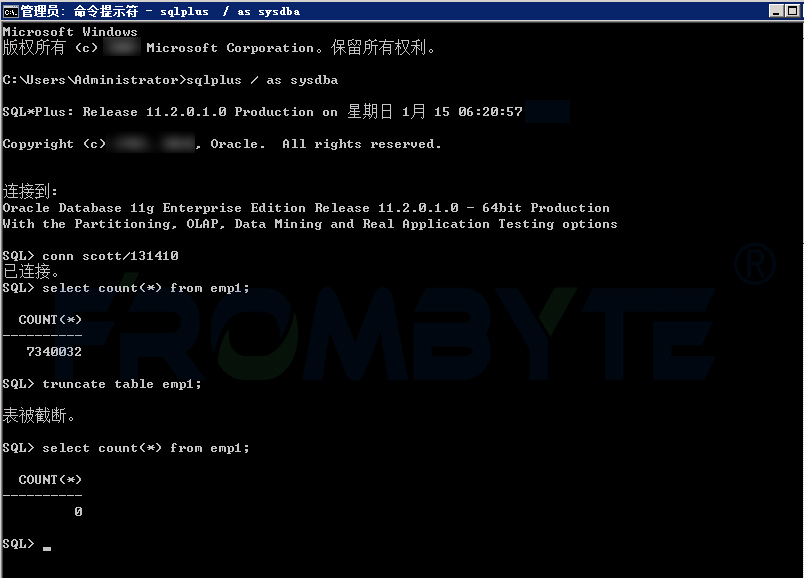

北京某单位Oracle 11g R2数据库误执行truncate table CM_CHECK_ITEM_HIS,表数据丢失,查询该表时报错。数据库备份无法使用,表数据无法查询。

2023-09-11 15:30:22 309

309

2023-09-11 08:30:04 0

0 本文档描述了按严重程度分类的勘误表。

每种描述都包括:

实现偏离规范的缺陷的当前状态和发生错误行为的条件,以及与典型应用程序相关的勘误表的含义,以及可能的情况下的应用程序和限制

2023-09-05 07:05:23

本文档描述了按严重程度分类的勘误表。

每个描述包括:·缺陷的当前状态·实现偏离规范的位置和发生错误行为的条件·勘误表对典型应用程序的影响·可能的情况下的应用和限制

2023-09-05 06:37:05

本文档描述了按严重程度分类的勘误表。

每种描述都包括:

·缺陷的当前状态·实施偏离规范的地方和发生错误行为的条件·勘误表对典型应用程序的影响·在可能的情况下“变通办法”的应用和限制

2023-09-05 06:28:08

开关电源 PCB 设计规范 一、 安全距离(AC100V~240V) 1, 保险之前标准,基本绝缘的电源距离≥2.5mm,加强绝缘的电源≥3.4mm,不足则开槽,槽宽≥0.8 mm. 2, 保险之后

2023-09-04 17:25:32 2303

2303 本文档描述了按严重程度分类的勘误表。

每种描述都包括:

勘误表的当前状态。

如果实现偏离了规范和发生错误行为所需的条件。

勘误表对典型应用程序的影响。

在可能的情况下,解决方法的应用和限制。

2023-09-04 07:58:45

本文档描述了按严重程度分类的勘误表。

每个描述包括:·缺陷的当前状态·实现偏离规范的位置和发生错误行为的条件·勘误表对典型应用程序的影响·可能的情况下的应用和限制

2023-09-04 07:49:46

LPDDDD2(DMC-342)本文件描述了按严重程度分类的勘误表。每个描述包括:

缺陷的当前状态,其中实现偏离了规范,以及错误行为发生的条件,关于典型应用程序的勘误表的含义,“变通办法”的应用和限制(如可能)

2023-09-04 07:32:06

本文件描述了按严重程度分类的勘误表。每个描述包括:

缺陷的当前状态 实现偏离规范和错误行为发生的条件 勘误表对典型应用的启示 在可能的情况下,“变通办法”的应用和限制。

2023-09-04 06:18:27

本文档描述了按严重程度分类的勘误表。

每种描述都包括:

·勘误表的当前状态。

·如果实施偏离规范和发生错误行为所需的条件。

·勘误表对典型应用的影响。

·在可能的情况下,解决办法的应用和限制。

2023-09-01 11:07:49

本文档描述了按严重程度分类的勘误表。

每种描述都包括:

勘误表的当前状态。

实现偏离规范和发生错误行为所需的条件的。

关于典型应用的勘误表的含义。

在可能的情况下使用解决办法的应用程序和限制

2023-09-01 07:34:56

本文档描述了按严重程度分类的勘误表。

每种描述都包括:

实施偏离规范的缺陷的当前状态以及发生错误行为的条件勘误表对典型应用程序的影响可能的应用程序和解决办法的限制本文档描述了可能影响任何正在开发将在本ARM产品的实施上运行的软件的勘误表。

2023-08-30 08:29:21

本文档描述了按严重程度分类的勘误表。

每种描述都包括:

实施偏离规范的缺陷的当前状态以及发生错误行为的条件勘误表对典型应用程序的影响应用程序和限制(在可能的情况下)本文档描述了可能影响任何正在开发将在此ARM产品的实施上运行的软件的勘误表

2023-08-30 08:20:22

本文档描述了按严重程度分类的勘误表。

每个描述包括:·缺陷的当前状态·实现偏离规范的位置和发生错误行为的条件·勘误表对典型应用程序的影响·可能的情况下的应用和限制

2023-08-30 07:50:19

本文档描述了按严重程度分类的勘误表。

每种描述都包括:

·缺陷的当前状态·实施偏离规范的情况和发生错误行为的条件·勘误表对典型应用程序的影响·在可能的情况下‘变通办法’的应用和限制本文档描述的勘误表可能会影响任何正在开发将在此ARM产品的实施上运行的软件的人。

2023-08-30 07:44:08

本文档描述了按严重程度分类的勘误表。

每种描述都包括:

实施偏离规范的缺陷的当前状态以及发生错误行为的条件勘误表对典型应用程序的影响可能的应用程序和解决办法的限制本文档描述了可能影响任何正在开发将在本ARM产品的实施上运行的软件的勘误表。

2023-08-30 06:06:13

本文档描述了按严重程度分类的勘误表。

每种描述都包括:

·勘误表的当前状态。

·如果实施偏离规范和发生错误行为所需的条件。

·勘误表对典型应用的影响。

·在可能的情况下,解决办法的应用和限制。

2023-08-29 08:08:30

本文档描述了按严重程度分类的勘误表。

每种描述都包括:

·缺陷的当前状态·实施偏离规范的情况和发生错误行为的条件·勘误表对典型应用程序的影响·在可能的情况下‘变通办法’的应用和限制本文档描述的勘误表可能会影响任何正在开发将在此ARM产品的实施上运行的软件的人。

2023-08-29 07:52:19

本文档描述了按严重程度分类的勘误表。

每种描述都包括:·缺陷的当前状态·实施偏离规范的情况和发生错误行为的条件·勘误表对典型应用程序的影响·可能的情况下,“变通办法”的应用和限制本文档描述的勘误表可能会影响正在开发将在此ARM产品的实施上运行的软件的任何人。

2023-08-24 07:13:36

本文档描述了按严重程度分类的勘误表。

每种描述都包括:

勘误表的当前状态。

如果实现偏离了规范和发生错误行为所需的条件。

勘误表对典型应用程序的影响。

在可能的情况下解决方法的应用和限制

2023-08-24 06:51:11

本文档描述了按严重程度分类的勘误表。

每种描述都包括:

勘误表的当前状态。

如果实现偏离了规范和发生错误行为所需的条件。

勘误表对典型应用程序的影响。

在可能的情况下,解决方法的应用和限制。

2023-08-24 06:23:09

在这半年时间内,我除了负责一个智能接线盒产品的研发工作,还承担了一个非常重要的工作-福x系统设计规范的翻译以及解释。

2023-08-23 09:06:52 849

849

本文档描述了按严重程度分类的勘误表。

每个描述包括:·缺陷的当前状态·实现偏离规范的位置和发生错误行为的条件·勘误表对典型应用程序的影响·可能的情况下的应用和限制

2023-08-22 08:20:20

本文档描述了按严重程度分类的勘误表。

每个描述包括:·缺陷的当前状态·实现偏离规范的位置和发生错误行为的条件·勘误表对典型应用程序的影响·可能的情况下的应用和限制

2023-08-22 06:47:06

本文档描述了按严重程度分类的勘误表。

每种描述都包括:

实现偏离规范的缺陷的当前状态和发生错误行为的条件,以及与典型应用程序相关的勘误表的含义,以及可能的情况下的应用程序和限制

2023-08-22 06:33:59

本文档描述了按严重程度分类的勘误表。

每种描述都包括:

勘误表的当前状态。

如果实现偏离了规范和发生错误行为所需的条件。

勘误表对典型应用程序的影响。

在可能的情况下,解决方法的应用和限制。

2023-08-22 06:24:33

本文档描述了按严重程度分类的勘误表。

每个描述包括:·缺陷的当前状态·实现偏离规范的位置和发生错误行为的条件·勘误表对典型应用程序的影响·可能的情况下的应用和限制

2023-08-22 06:12:07

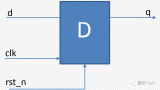

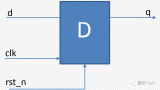

D触发器结构如下图所示,先有时钟上升沿,然后才有D的值赋给Q,没有上升沿Q值保持不变,时序逻辑在时钟上升沿/下降沿后才变化

2023-08-18 10:23:36 1148

1148

本文包含以下几方面内容,程序设计,模块例化、运算符,模块设计模板

目标:用最简单,最简洁的方式,设计最易读,最高效的代码

2023-08-17 10:14:50 256

256

2023-08-16 11:31:35 0

0 注:以R起头的是对编写Verilog代码的IP设计者所做的强制性规定,以G起头的条款是建议采用的规范。每个设计者遵守本规范可锻炼命名规范性。

2023-08-15 16:23:41 1088

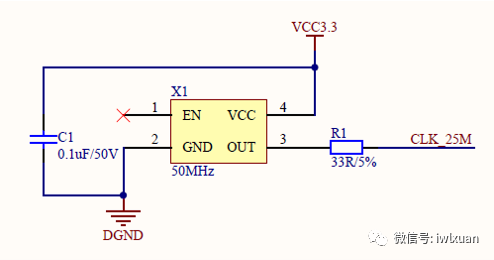

1088 小编在本节介绍FPGA芯片外围电路设计规范和配置过程,篇幅比较大,时钟的设计原则就有17条,伙伴们耐心读一读。

2023-08-15 16:18:11 3369

3369

本文档描述了按严重程度分类的勘误表。

每种描述都包括:

勘误表的当前状态。

如果实现偏离了规范和发生错误行为所需的条件。

勘误表对典型应用程序的影响。

在可能的情况下解决方法的应用和限制

2023-08-12 07:22:33

本规范描述了AMBA ATB协议。本规范中对ATB的所有引用均指AMBA ATB。本文件中的信息取代CoreSight体系结构规范中的ATB信息

2023-08-11 07:39:54

本文件描述了按严重程度分类的勘误表。每个描述包括:

勘误表的当前状态。实现偏离规范和发生错误行为所需的条件。勘误表对典型应用的影响。在可能的情况下,变通方法的应用和限制。

2023-08-11 07:06:20

AMBA LTI协议规范与ARM系统内存管理单元(MMU)架构一致,是对AMBA分布式翻译接口(DTI)的补充,以提供更高的性能和更高效的翻译服务。

LTI是点对点协议,定义了IO管理器和转换缓冲

2023-08-11 06:54:57

本文档描述了按严重程度分类的勘误表。

每种描述都包括:

缺陷的当前状态

实施偏离规范的情况和发生错误行为的条件

勘误表对典型应用程序的影响

在可能的情况下‘变通办法’的应用和限制本文档描述的勘误表可能会影响任何正在开发将在此ARM产品的实施上运行的软件的人。

2023-08-11 06:39:56

本文件描述了按严重程度分类的勘误表。每个描述包括:

勘误表的当前状态。实现偏离规范和发生错误行为所需的条件。勘误表对典型应用的影响。变通方法的应用和限制(如可能)

2023-08-10 07:38:30

本文件描述了按严重程度分类的勘误表。每个描述包括:

勘误表的当前状态。实现偏离规范和发生错误行为所需的条件。勘误表对典型应用的影响。变通方法的应用和限制(如可能)

2023-08-10 07:28:14

本文件描述了按严重程度分类的勘误表。每个描述包括:

勘误表的当前状态。实现偏离规范和发生错误行为所需的条件。勘误表对典型应用的影响。变通方法的应用和限制(如可能)

2023-08-10 07:08:42

本文件描述了按严重程度分类的勘误表。每个描述包括:

勘误表的当前状态。实现偏离规范和发生错误行为所需的条件。勘误表对典型应用的影响。在可能的情况下,变通方法的应用和限制。

2023-08-10 06:56:32

本文件描述了按严重程度分类的勘误表。每个描述包括:

勘误表的当前状态。实现偏离规范和发生错误行为所需的条件。勘误表对典型应用的影响。变通方法的应用和限制(如可能)

2023-08-10 06:53:03

本文件描述了按严重程度分类的勘误表。每个描述包括:

勘误表的当前状态。实现偏离规范和发生错误行为所需的条件。勘误表对典型应用的影响。变通方法的应用和限制(如可能)

2023-08-10 06:40:39

本文件描述了按严重程度分类的勘误表。每个描述包括:

勘误表的当前状态。实现偏离规范和发生错误行为所需的条件。勘误表对典型应用的影响。变通方法的应用和限制(如可能)

2023-08-10 06:37:58

本文件描述了按严重程度分类的勘误表。每个描述包括:

勘误表的当前状态。实现偏离规范和发生错误行为所需的条件。勘误表对典型应用的影响。在可能的情况下,变通方法的应用和限制。

2023-08-09 07:31:29

本文件描述了按严重程度分类的勘误表。每个描述包括:

勘误表的当前状态。实现偏离规范和发生错误行为所需的条件。勘误表对典型应用的影响。在可能的情况下,变通方法的应用和限制。

2023-08-08 07:38:34

工作频率低于1MHz时,噪声一般由电场或磁场引起,(磁场引起时干扰,一般在几百赫兹以内),1MHz以上,考虑电磁干扰。单板上的屏蔽实体包括变压器、传感器、放大器、DC/DC模块等。更大的涉及单板间、子架、机架的屏蔽。

2023-07-31 14:21:36 759

759

详细理解设计需求,从需求中整理出电路功能模块和性能指标要求、

2023-07-28 10:54:18 549

549

电线和端子有焊接和压接两种方法。端子压接工艺因为加工工艺简单,设备费用低,加工工时短等优点,在过去的几年中被广泛使用,近几年因为铝导体和大截面端子的使用,端子的焊接工艺也逐渐应用增多。

2023-07-25 10:48:40 565

565

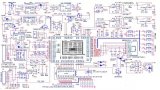

规范印制电路板工艺设计,满足印制电路板可制造性设计的要求,为硬件设计人员提供印制电路板工艺设计准则,为工艺人员审核印制电路板可制造性提供工艺审核准则。

2023-07-20 14:49:42 546

546 今天要介绍的时序分析基本概念是lookup table。中文全称时序查找表。

2023-07-03 14:30:34 664

664

点击上方 蓝字 关注我们 FPGA设计规范 1.设计必须文档化。要将设计思路,详细实现等写入文档,然后经过严格评审通过后才能进行下一步的工作。这样做乍看起来很花时间,但是从整个项目过程

2023-06-19 09:35:01 963

963 SMT-PCB拼版设计规范

2023-06-15 10:59:11 878

878

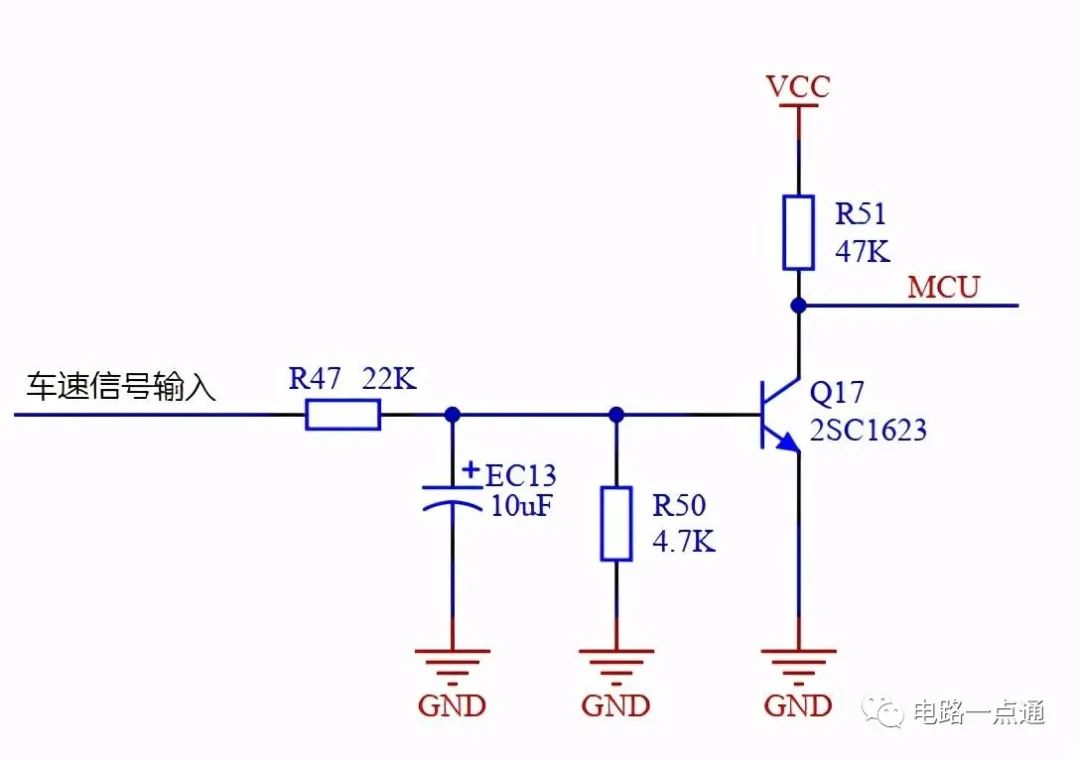

01 硬件电路设计规范 1、 详细理解设计需求,从需求中整理出电路功能模块和性能指标要求; 2、 根据功能和性能需求制定总体设计方案,对 CPU 进行选型, CPU 选型有以下几点要求

2023-05-31 09:23:31 833

833

PCB 制造是按照的一组规范从 PCB 设计构建物理 PCB的过程。对设计规范的理解非常重要,因为它会影响 PCB 的可制造性、性能和生产良率。

2023-05-30 09:11:45 403

403

设计规范和有限元分析软件的融合。目前分析设计绝大部分采用有限元软件完成,但规范对如何运用有限元软件进行压力容器及其元件的设计和评估并未给出详细的指导。

2023-05-23 14:52:25 630

630

失效分析为设计工程师不断改进或者修复芯片的设计,使之与设计规范更加吻合提供必要的反馈信息。

2023-05-13 17:16:25 1365

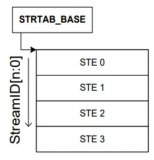

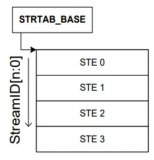

1365 incoming transaction的StreamID可以找到一个STE。SMMU支持两种Stream table格式,格式由Stream table base registers设置。

2023-05-11 09:22:57 710

710

上图就是SMMU Level 1 Stream Table Descriptor的数据格式,简称Level1 STD。

2023-05-06 14:44:44 478

478

本标准适用于公司电子产品的 PCB 工艺设计,主要适用于 PCB 的设计、PCB 投板工艺审查、单板工艺审查等活动。

2023-05-02 15:14:00 2972

2972

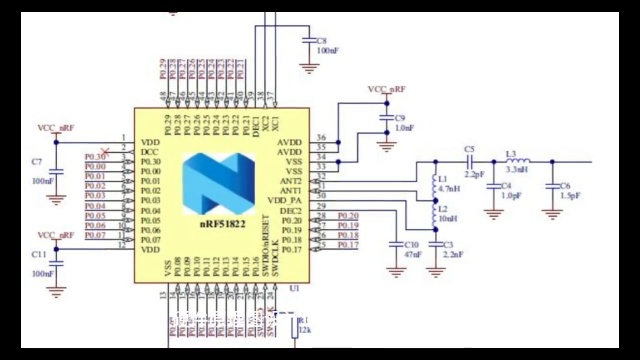

近些年来,由于蓝牙设备,可穿戴设备,无线局域网络设备和移动设备的市场快速增长,对于RF电路的需求也越来越多,特别是未来几年物联网的投入使用,RF电路市场更加是迅猛增长。但是RF电路的设计就跟电磁干扰一样,一直是工程师们最难解决的问题。想要成功设计出一块好的RF电路,就必须要仔细将整个设计过程中每个步骤和细节都要仔细规划,稳中求胜。

射频电路的设计和普通pcb的设计,在理论上有很多的不一样。首先,射频电路存在不确定性,但是这并不妨碍我们可以设计出一块好的射频电路,其实是射频电路的设计当中,还是有很多的规则技巧可以使用的。但是到了实际过程中,这些规则和技巧可能会因为某种限制而无法使用,所以如何处理这个问题,成了RF设计课程中的一个重要难题。

无线产品的开发时,射频电路布线是一个十分关键的要素。可能在原理的设计上已经非常完美了,但是现实当中总是会有一些问题来制约这个电路的性能。实际测试当中并不能达到理想的状态,这些问题很多都是在布线过程中做得不够完备的原因。下面我们就在布线这个问题切入,来讲解一下射频电路的设计中需要注意的一些小技巧。

PCB的结构

首先在进行布线之前,我们要确定一下电路板的结构,就像建一栋房子之前,我们要先规划好房子的层数。电池板的结构和电路设计的复杂程度,电磁兼容等很多因素有关,在实际生产设计中,不会有单层板出现,所以我们下面多层板来进行举例。

比如一个四层板,在设计时一般会将第二层作为完整的地平面,把重要的信号分布在top层。这样可以很好的控制阻抗,在六层板以及更多层板的设计当中,都和四层板的设计一样,都是需要一个完整的地平面,然后利用top层进行,信号走线。

控制阻抗

布线过程中需要注意的就是控制阻抗,比如走线时应该尽量控制走线的特征是50Ω,而电阻跟线宽有关系,在进行原理设计和仿真的时候,应该利用公式计算出特征阻抗在50Ω上下,符合要求的就可以设计为一条射频走线了。

元器件摆放

在pcb设计中,我们一般遵循一个规则,就是走线尽可能短,也就是说元件一般是和电源靠近,然后相应的元件紧密排列。这样既保证了pcb的美观明了,同时也缩短了布线的长度,在射频电路的设计时,我们也应该遵循这条设计规则。

射频走线

在进行走线时,除了上面所说的长度要尽可能短,还有一点和普通pcb设计不同的就是,射频电路走线应该用圆弧型来实现拐角,而不是一般的45°/135°拐角。因为射频信号线是不能有任何折点的。如果射频信号线在实际过程中产生了不可避免的交叉,这时就必须要使用过孔来引导一部分的信号进行传输,这部分信号无论是走底层还是中间层的哪一层,视频走线都一定需要一个参考平面。但是一定要注意,地平面一定要连续。

原作者:Samking EDA设计精品智汇馆

2023-04-25 17:29:11

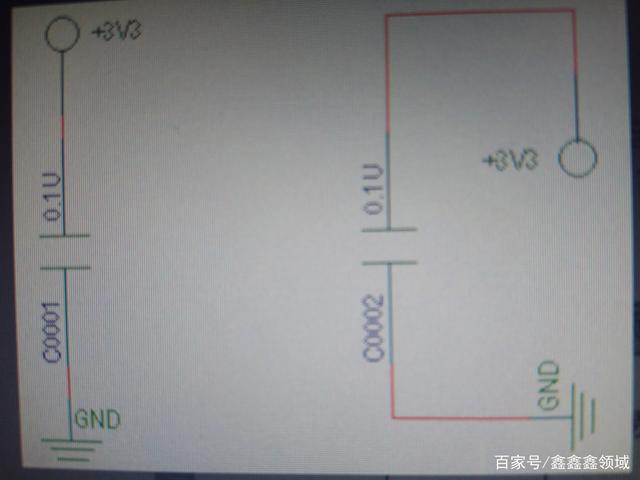

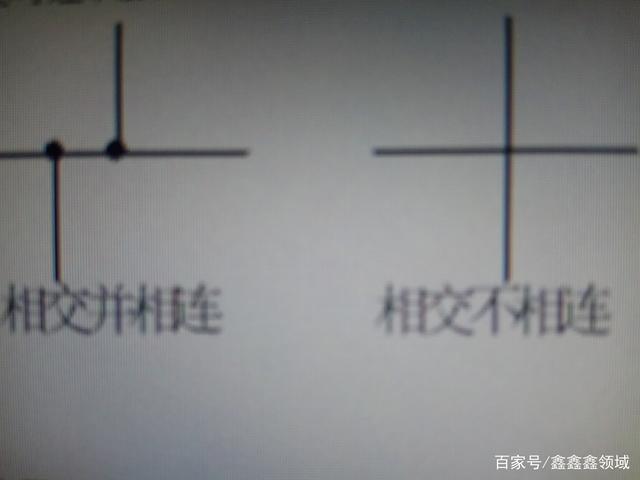

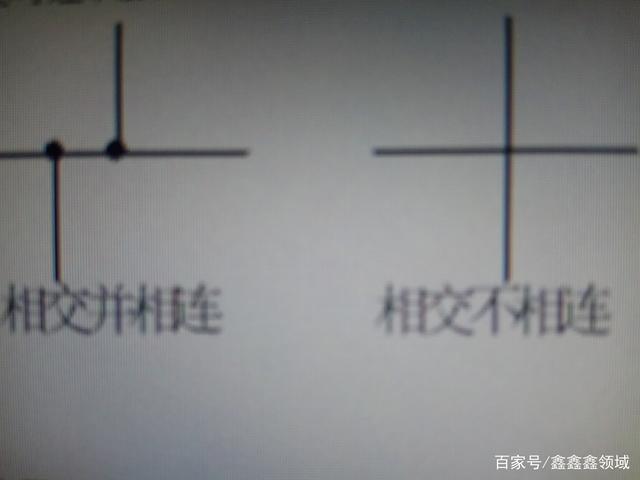

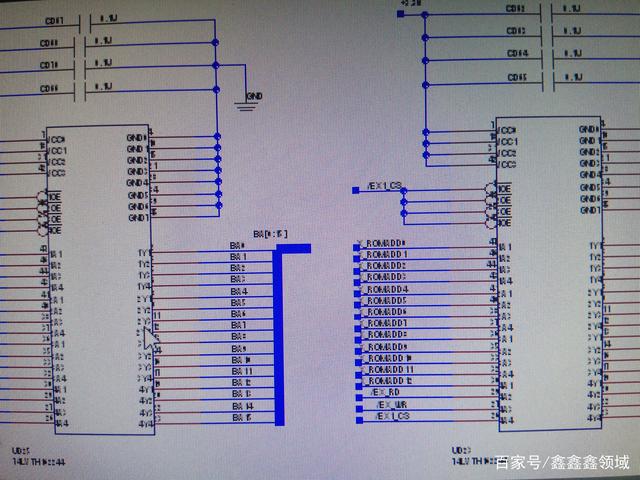

网络标号不能放在两根线的交叉处,否则网络标号的归属不清,会引起两个网路的短接。

2023-04-23 16:31:23 892

892

一条电气连接线不应在另一条线交叉处改变方向,也不应穿过其他连接线的连接点或者元器件引脚的末端。

2023-04-23 16:19:00 1242

1242

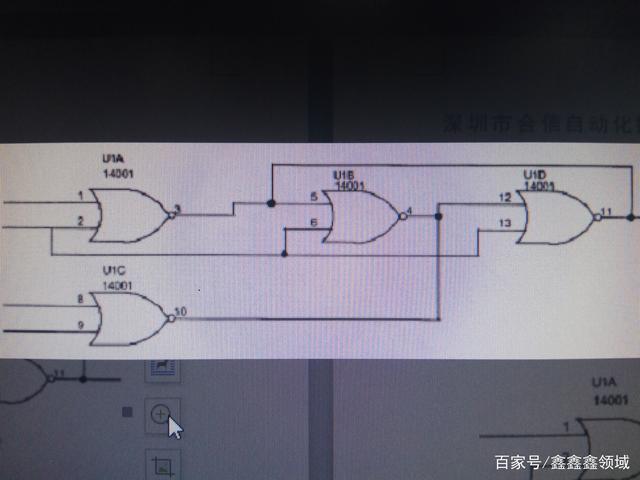

在原理图中,对于多个单元运放IC和逻辑电路IC一般要按照电路功能将每个单元分开放置,便于对电路的理解和视图,也符合电路功能单元集中布局的规则。

2023-04-23 16:06:38 1625

1625

在布局时,首先优先考虑功能布局法,功能相关或者相同的单元电路应该靠近绘制,以使电路关系表达的清晰明了。

2023-04-23 16:03:43 984

984

在文件imx8mm.dtsi中,opp 表报告了 SoC数据表表10 中记录的相同 3 个工作点:1.2、1.6 和 1.8 GHz

但是,在文件clk-pll14xx.c中,表

2023-04-23 11:14:12

,应采用双箭头的进板标识。(对于回流焊,可考虑采用工装夹具来确定其过回流焊的方向)。 5.4.3 两面过回流焊的 PCB 的BOTTOM 面要求无大体积、太重的表贴器件需两面都过回流焊的 PCB

2023-04-20 10:48:42

设备 PCB 安规设计规范》》 XXXOE0199001 《《电子设备的强迫风冷热设计规范》》 XXXE0199002 《《电子设备的自然冷却热设计规范》》 IEC60194 《《印制板设计、制造

2023-04-20 10:39:35

。 4. 对于原理图中不符合硬件原理图设计规范的地方,要明确指出,并积极协助原理图设计者进行修改。 5. 在与原理图设计者交流的基础上制定出单板的PCB设计计划,填写设计记录表,计划要包含设计过程中

2023-04-19 16:18:50

过孔(via)是多层PCB的重要组成部分之一,钻孔的费用通常占PCB制板费用的30%到40%。从设计的角度来看,一个过孔主要由两个部分组成,一是中间的钻孔(drill hole),二是钻孔周围的焊盘区,这两部分的尺寸大小决定了过孔的大小。很显然,在高速,高密度的PCB设计时,设计者总是希望过孔越小越好,这样板上可以留有更多的布线空间,此外,过孔越小,其自身的寄生电容也越小,更适合用于高速电路。 但孔尺寸的减小同时带来了成本的增加,而且过孔的尺寸不可能无限制的减小,它受到钻孔(drill)和电镀(plating)等工艺技术的限制:孔越小,钻孔需花费的时间越长,也越容易偏离中心位置;且当孔的深度超过钻孔直径的6倍时,就无法保证孔壁能均匀镀铜。 因此综合设计与生产,我们需要考虑以下问题: 1、全通过孔内径原则上要求0.2mm(8mil)及以上,外径的是0.4mm(16mil)以上,有困难地方必须控制在外径为0.35mm(14mil); 提示小助手:按照经验PCB常用过孔尺寸的内径和外径的大小一般遵循X*2±2mil(X表示内径大小)。比如8mil内径大小的过孔可以设计成8/14mil、8/16mil或者8/18mil;比如12mil的过孔可以设计为12/22mil、12/24mil、12/26mil; 2、BGA在0.65mm及以上的设计建议不要用到埋盲孔,成本会大幅度增加。用到埋盲孔的时候一般采用一阶盲孔即可(TOP层-L2层或BOTTOM-负L2),过孔内径一般为0.1mm(4mil),外径为0.25mm(10mil),如图1-1所示。 图1-1 一阶盲孔示意 3、过孔不能放置在小于0402电阻容焊盘大小的焊盘上;理论上放置在焊盘上引线电感小,但是生产的时候,锡膏容易进去过孔,造成锡膏不均匀造成器件立起来的现象(‘立碑’现象)。一般推荐间距为4-8mil,如图1-2。 图1-2 过孔到焊盘打孔示意 4、过孔与过孔之间的间距不宜过近,钻孔容易引起破孔,一般要求孔间距0.5mm及以上,0.35mm-0.4mm极力避免,0.3mm及以下禁止,如图1-3所示; 图1-3 过孔与过孔之间的家间距 5、如图1-4,除散热过孔外,≤0.5mm的过孔,需塞孔盖油(内径是0.4mm内需堵孔)。 1)特别是有金属外壳的器件,本体下原则不打过孔,打了过孔的一定塞孔盖油,以免造成外壳与过孔短路。 2)根据板厂生产反馈,会经常提到BGA下过孔离焊盘太近,需要移动过孔。这种情况都是由于过孔不是距BGA焊盘等距造成的,由于目前BAG下过孔、测试孔的位置不与BGA各焊盘等距是一种常态,PCB设计人员对此也不重视,导致工程问题不断,对焊接质量也是一种隐患。因此,我们直接推荐打孔打到两焊盘的中心位置,特别是BGA里面由于Pitch间距较小,打孔之后也需要对BGA下的过孔塞孔盖油,以免容易造成BGA球连锡短路。 图1-4 过孔应用情景 6、耳机端子、按键、FPC等固定焊盘为防焊盘铜皮掉落,在条件允许的情况下焊盘打1-2个过孔(过孔均匀放置),可以有效提高“固定性”,如图1-5。 图1-5 固定焊盘过孔的放置 7、扇孔 在PCB设计中过孔的扇出很重要,扇孔的方式会影响到信号完整性、平面完整性、布线的难度,以至于影响到生产的成本。 1)常规CHIP器件的扇孔推荐及缺陷做法,如图1-6所示,可以看出推荐做法可以在内层两孔之间过线,参考平面也不会被割裂,反之不推荐做法增加了走线难度,也把参考平面割裂,破坏平面完整性。 图1-6 常规CHIP器件扇出方式对比 同样,这个样的器件扇孔方式适用于打孔换层的情景,如图1-7所示。 图1-7 打孔换层应用情景 2)BGA扇孔方式 BGA扇孔同样过孔不宜打孔在焊盘上,推荐打孔在两个焊盘的中间位置。很多工程师为了出线方便随意挪动BGA里面过孔的位置甚至打在焊盘上面,如图1-8所示,造成BGA区域过孔不规则易造成后期焊接虚焊的问题,同时可能破坏平面完整性。 图1-8 BGA盘中孔示例原作者:郑振宇 凡亿PCB

2023-04-17 17:37:39

规范来控制产品设计,在产品开发的后期,甚至在大批量生产阶段才发现这样或那样的组装问题,此时想通过设计更改来修正,无疑会增加开发成本并延长产品的上市周期。但是,如果不进行修改,批量生产造成的损失就会

2023-04-14 16:17:59

确保信号完整性的一个重要部分是信号走线的物理布线。PCB设计人员经常承受压力,不仅要缩小设计,还要保持信号完整性。找到平衡点就是要知道问题可能发生的位置以及在系统出现故障之前可以推送信封的距离。 高速电流无法应对信号迹线中的不连续性。最常见和有问题的不连续性是如图A所示的直角拐角。虽然直角拐角在低频下工作没有问题,但在高速时它们会辐射。相反,直角可以用斜角90º角(图B)或两个间隔45°角(图C)代替。 对于高速信号,甚至不应考虑小于90º的角。 另一个常见问题是存根痕迹。除非有特殊原因使用它们,否则应从电路板上删除所有存根。问题在于,在高频下,短截线可能会辐射,也会对信号走线产生一系列阻抗问题。 高速设计的另一个关键领域是差分对的布线。差分对通过以互补的方式驱动两个信号迹线来操作。差分对提供出色的抗噪声能力和更高的S / N比。然而,实现这些优势有两个限制: 1、两条走线必须相互靠近布线; 2、两条迹线的长度必须匹配。 当一对必须绕弯道布线时,问题会出现,如下图所示。问题是在两个未对齐的组件之间路由差分对。图A中的解决方案存在缺陷,因为外侧的轨道明显长于内侧的轨道。正确的解决方案如图B所示。这里左转后跟右转,所以两条轨道的长度相等。这说明了路由差分对的一般规则:沿相反方向跟随每个弯曲。原作者:杨多多 志博PCB

2023-04-12 15:20:37

微电网设计规范需要综合考虑空气质量、安全、可靠性、可持续性、节能、供需平衡等多个方面的要素,以下是微电网设计规范的主要内容:

1. 负载和能源管理: 能量和负载应该合理匹配,并对负载进行

2023-04-09 10:30:52 1070

1070 配电箱的一级、二级、三级箱是根据电压级别进行划分的。在国家的《建筑电气设计规范》中,将配电箱的一级、二级、三级箱进行了如下的规定:

2023-04-04 18:11:18 27442

27442 变电站设计规范是根据国家相关法律法规和标准制定的,旨在保障变电站的安全运行,最大限度地减少电力设备事故和电力设备损害。下面是变电站设计规范的基本要求和细节:

2023-04-03 16:07:38 1438

1438 智能工具……免费领取【PCB可制造性设计规范手册】下载DFM软件并登录后,点击“订单管理”-“D分商城”,无需积分兑换,点击“商品详情”即可免费获取

2023-03-30 20:13:57

,并且有多种模块规范可供选择。 本规范推荐用户选择泛用性较广的协议规范进行硬件开发设计,例如:COMe、 So-DIMM、Q7 等。以 COMe Type7 设计规范为例,核心模块可集成 1 个处理

2023-03-30 14:57:01 3

3

电子发烧友App

电子发烧友App

评论