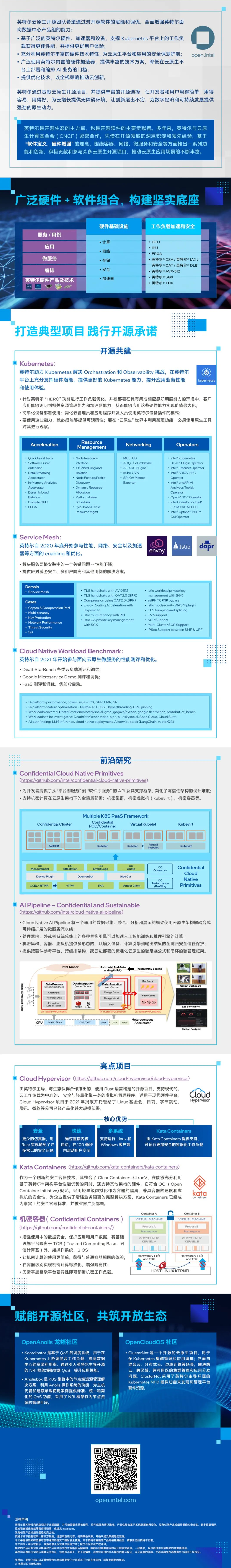

编者按:最近英特尔举办了一场引人注目的“架构日”活动,公布了未来多年的产品技术路线图、技术战略规划以及一系列新技术。外媒The Next Platform随即发布了一篇深度分析文章,对Tick-Tock模式演进和Foveros 3D芯片封装技术进行了深度解析。作者认为,面临压力,英特尔能从现有工艺中释放出超乎想象的更高性能;而Foveros将在不久的将来为英特尔计算引擎的构建奠定基础。

以下为部分摘选:

创新离不开动力。从财务角度来看,RISC/Unix供应商的衰落以及AMD在服务器市场的缺席使英特尔大为受益,它在数据中心的霸权也从未如此强大,收入和利润不断突破记录。

这也来源于超大规模运营商和云构建商的崛起所带来的机遇,同时也带给英特尔一些竞争压力,这些压力在之前往往来自于直接竞争对手、OEM和ODM。虽然英特尔在数据中心计算服务器方面仍幸运地保持增长且接近垄断,并扩展到网络和存储设备且都取得了一些成绩,但缺乏竞争确实损害了英特尔的工程优势。

对于英特尔来说轻松赚钱是好事。服务器市场的增长速度比弱小竞争对手吞食市场份额的速度要快得多,AMD Epyc和Marvell ThunderX2的攻击以及IBM Power9的一系列动作并没有真正打击到英特尔的核心服务器业务。延迟了两年的10纳米工艺虽然扰乱了英特尔的路线图,但也没造成什么确切影响。然而在2019年,随着AMD和Marvell使用台积电的先进工艺推出下一代产品,战火将会蔓延,并很可能会波及英特尔。

挫败这些攻击,是英特尔公司处理器核心和视觉计算高级副总裁、英特尔边缘计算解决方案总经理兼首席架构师Raja Koduri,以及高级副总裁兼硅工程事业部总经理Jim Keller的工作。Koduri和Keller是分别负责让AMD Radeon GPU和Epyc CPU产品线重生的人物。这两位和其他英特尔高管在最近举行的架构日活动中,在英特尔联合创始人Robert Noyce旧居发布了攻防计划。在这里,英特尔从高处俯瞰硅谷,试图在数据中心拿下更大一块地盘。

罗马不是一天建成的,也不是一天毁灭的

大家都熟悉英特尔十多年来采用的Tick-Tock模式。英特尔将芯片改进的过程分为两个部分以降低风险,其中Tick阶段是晶体管制造工艺的缩小,Tock阶段是基于前阶段工艺的架构改进。使用Tick-Tock模式,英特尔可以维持稳定的性能提升,该模式也运作得非常好,直到Tick阶段需要花费更长的时间且Tock阶段变得越来越难。

英特尔从14纳米开始打破Tick-Tock模式,延长为Tick-Tick-Tick-Tick模式,试图从一个芯片工艺节点获得更高的性能。这种改变很有必要,10纳米工艺的推迟导致了14纳米Tick阶段的拉伸以及10纳米Tick阶段的延期,接着影响到依赖于10纳米工艺的一大堆Tock阶段。

从中得到的经验可能就是Tock阶段不能过分依赖于前面的Tick阶段,需要学习混搭不同工艺的芯片将它们塞进一个2D封装,或者堆叠成3D封装。实际上只需要在最有用的芯片上使用最先进的Tick工艺,而把其它的小芯片组件放在封装上,比如把消耗大量电能的内存控制器和I/O控制器放在芯片之外,这样成熟的晶体管蚀刻工艺尺寸会更大,但制造成本也更低。

关于制程,有一点非常重要。面临压力,英特尔能从现有工艺中释放出超乎想象的更高性能。当前14纳米FinFET工艺蚀刻的酷睿台式机处理器就是一个很好的例子,并且这也适用于凌动或服务器的至强芯片。下表显示了过去几年酷睿芯片最高时钟速率随工艺优化的演变:

制程更新本质上是更平滑的优化,即使新的工艺已经推出,每个制程节点仍会持续更长的时间。这种更平滑的方式可以帮助缓解一些竞争压力,但随着英特尔增加10纳米设备而减少14纳米设备,导致了2018年PC芯片和一些服务器芯片的短缺,迫使英特尔集中精力在最佳良率上,并把最好的14纳米工艺应用于最畅销的PC和服务器芯片。

英特尔需要让客户习惯这种Tick-Tick-Tick-Tick-Tick模式,它将改变工厂增减设施来满足需求的方式。

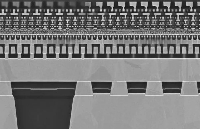

Koduri希望大家了解的是,英特尔现在已经掌控10纳米工艺,而且正在前瞻7纳米甚至更先进的5纳米。这是当前路径的样子:

如图,英特尔每个制程节点有两个不同版本,一个针对计算优化,一个针对I/O优化,因为二者需要不同的晶体管属性。以偶数结尾的制程变数用于计算,以奇数结尾的用于I/O。在最初的10纳米制程后面,有两个优化的计算节点,英特尔可能会对外称之为10纳米+和10纳米++。与此同时,后续的7纳米工艺,目前正在开发中。英特尔也正在对5纳米制程进行“寻路”研究。

制程工艺过剩

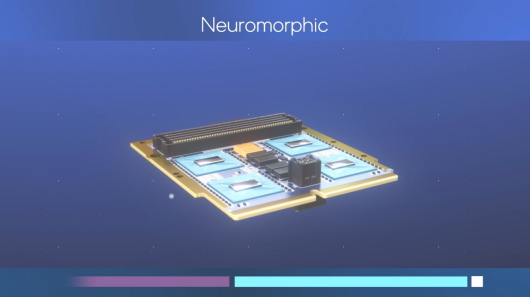

然而还有一个更大的问题需要解决,那就是数据中心的计算类型如同寒武纪大爆发一样增长。英特尔一直在构建不同计算类型的产品组合,除了至强和凌动服务器CPU、Arria和Stratix(来自收购的Altera)FPGA,及其Crest神经网络处理器(来自收购的Nervana)之外,英特尔非常清楚它还需要加入可用作加速器的独立GPU。英特尔需要可与Nvidia Tesla和AMD Radeon Instinct GPU加速器直接竞争的产品,这也是其首先雇用Koduri的原因之一。

目前尚不清楚英特尔将如何帮助客户选择用于任意特定工作负载的计算产品,因为在许多情况下会出现大量的重叠。

但是在我们深入了解这些让人眼花缭乱的芯片组合之前,且先退一步看看。英特尔一再表示,它追求的不再是价值仅450亿美元的客户端和服务器处理器市场,再加上一些闪存和部分超微互连,而是追求更广阔的3000亿美元的计算市场,将其产品嵌入数据中心、园区和边缘各式各样的装置中。要负担所有这些芯片的研究和工厂建设费用,英特尔将必须大规模生产。

Koduri提醒大家的第一件事是,并非所有的晶体管都适用于不同的场景,而且在这个摩尔定律放缓的世界,作为一个多元电子器件供应商,需要为不同类型的电路使用不同的制程工艺。即使可以使用单个制程技术大费周章地在芯片上建立单片系统,那也许并不算明智的做法。

“我们期望建立一个3000亿美元的潜在市场规模,并进入不同的市场领域,我们注意到需要建造的晶体管设计十分多样,”Koduri解释道。“例如,台式机CPU就对于性能和功率都有广泛的需求,新晶体管在这些场景中并不总是更适用。事实上,没有晶体管可以覆盖所有这些需求。另外,我们需要集成的晶体管越来越多样——我们有通信晶体管,I/O晶体管,FPGA晶体管,以及传统的CPU逻辑晶体管。“

因此,出于经济和技术因素,以及不同市场需要根据功率限制、性能特征、特性和成本集成不同原件,单个大芯片需要被拆分成多个小芯片(chiplet)。正如我们已经指出,不仅仅是英特尔,业界的一切都将向插槽内多芯片封装发展。

所以,这就是英特尔将要做的事情。尚不清楚具体什么时候、使用什么电路,但显然未来英特尔可编程解决方案事业部的“Falcon Mesa” FPGA将采用模块化插槽设计,并使用10纳米工艺至少来实现其核心逻辑。小芯片的模式不仅是将应用不同制程的组件部分组合,而是还能制造出比单个大芯片能适应更广泛的性能和功率范围的一系列部件。

另一个采用10纳米工艺的组件是英特尔112 Gb/s SerDes电路,它的制程可能在未来相当长一段时间内不会缩小。它支持脉幅调制,可在一个信号中承载更多比特。英特尔拥有112 Gb/s SerDes,意味着英特尔可以提供能与业界相媲美的Omni-Path 200及以太网连接,这对于英特尔和众多网络厂商竞争是很有必要的,其中一些对手同样销售英特尔处理器的竞品。

所有这些因素最终带来了Foveros 3D芯片封装技术,它将在不久的将来为英特尔计算引擎的构建奠定基础。Foveros是一种系统级封装集成,为嵌入式多芯片互连桥接(EMIB)多芯片封装技术增加了第二个维度,EMIB是英特尔一项研究多年的工作,并最终在连接小芯片的Stratix 10 FPGA、以及在单独封装的配置AMD GPU和高带宽内存(HBM)的Kaby Lake-G 酷睿芯片上得到应用。

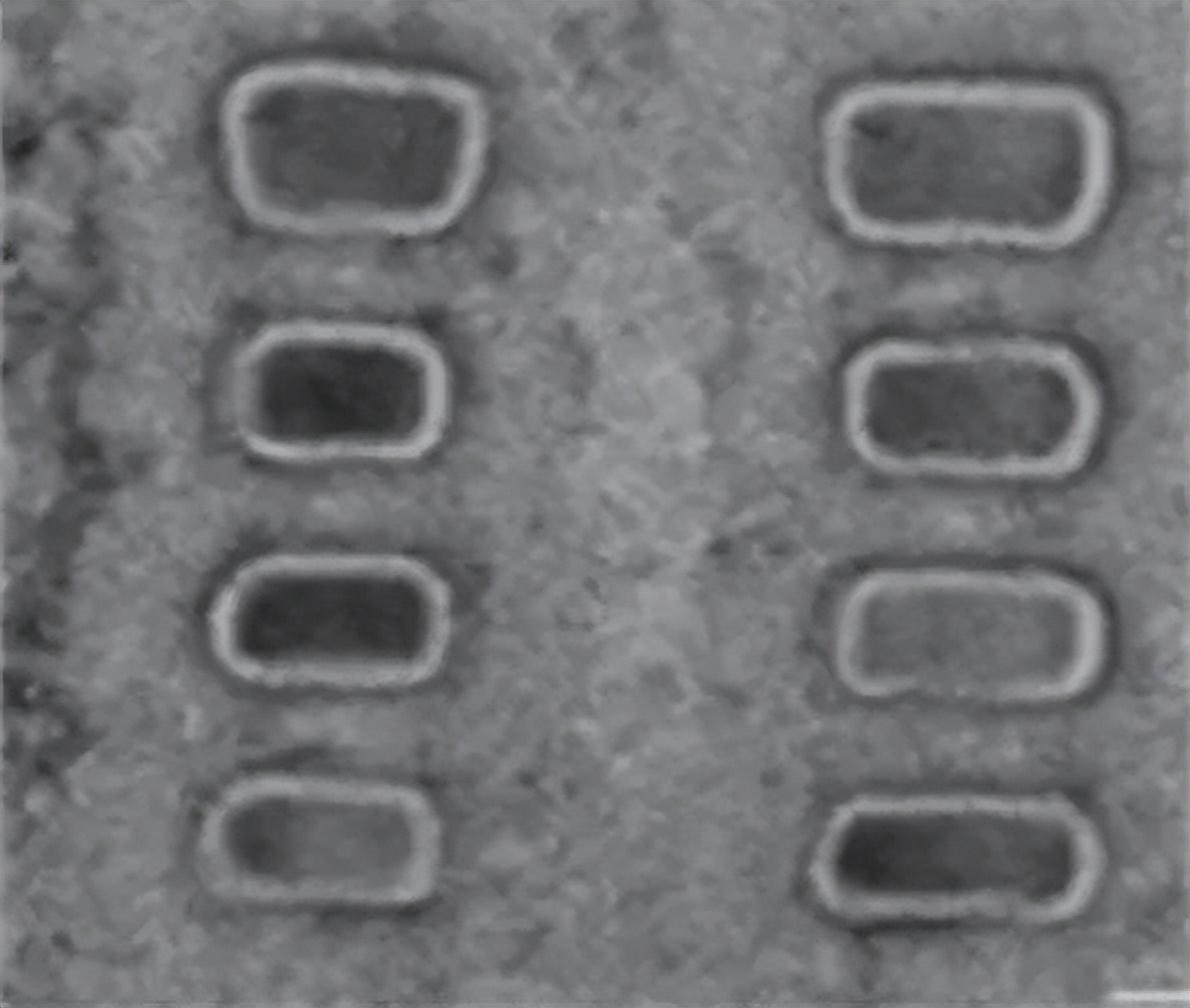

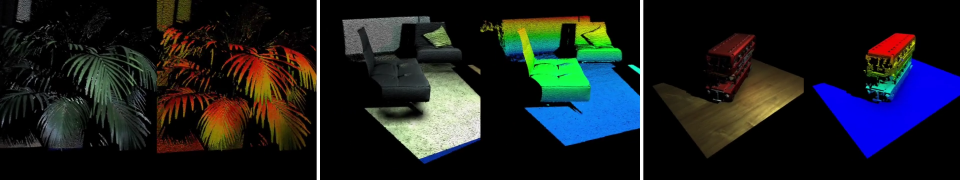

使用Foveros系统级封装多芯片模块,为计算复合体(可以包括内存及其它组件)提供服务的I/O电路、SRAM缓存和电源电路可以在基层芯片上构建,基层芯片覆盖于封装衬底上,衬底可以放置针脚与插槽配合,抑或直接焊接到主板上。有源中介层被放置在该封装衬底上,其上方的各种小芯片通过硅穿孔(TSV)可以互相连接。小芯片上的微凸块可以通过TSV向下深入中介层,从而连接到堆叠芯片的最底层,然后在中介层内可以到达邻近,或到达堆叠其上的其它芯片。除了一层底层芯片和另一层顶层芯片,可以有很多分层:

看看这些焊点凸起多么闪亮;当图形专家做演示时就会发生这种情况。

使用Foveros工艺的第一个产品在架构日上进行了演示,如下图:

这个设备定位是超便携应用,封装尺寸为12毫米×12毫米,远小于一枚美元硬币。具有I/O和其它片上系统组件的基层芯片使用1222工艺,该工艺是基础22纳米工艺的代号,非常久远,在完善后被应用于“Ivy Bridge”和“Haswell” 至强上。更大晶体管更适合电源和I/O电路。在其上方是使用10纳米工艺实现的计算复合体(1274,前缀P表示使用Foveros堆叠),在这个例子中,它包含了来自“Sunny Cove” 酷睿的一个核心和来自“Tremont” 凌动的四个核心,以一种ARM已经应用多年的方式混搭。最顶层是一大块叠层封装内存。英特尔没有说明这种芯片复合体在负载条件下功耗多少,但确实表示它在待机状态消耗为2毫瓦,大约是能取得的最低值。

英特尔并未明确表示在未来的酷睿和至强处理器中使用Foveros技术,但显然未来的“Falcon Mesa” FPGA,和2020年的Xe独立GPU中将用到它。我们认为未来的至强和凌动,以及各种CPU与GPU、FPGA、及Nervana神经网络处理器等混搭芯片上都会用到Foveros技术。

英特尔不再仅靠制程和架构来推动其计算业务,还将充分利用内存和互连芯片,将安全性嵌入到所有元素中,并与一个涵盖这些计算元素的更简单的集成软件集合在一起,也就是oneAPI。之后,我们还将深入探讨oneAPI以及各种计算引擎的路线图,以及它们对回归摩尔定律轨道的预期影响。

电子发烧友App

电子发烧友App

评论