前言——

在前段时间小编曾经发布了:固态硬盘知识进阶:专业名词篇。文内介绍了各类固态硬盘中可能会出现的比较晦涩和深入的名词,而很多朋友可能没听说过这些名词。如FTL、LBA、GC等。。。今天我们将剩下的一些名词再来说一下,给大家解读一下。

下面就来为大家解读这些名词。

目录:

一、预留空间(Over-provisioning,OP)

二、Trim

三、写入放大(Write amplification,WA)

四、坏块管理(Bad block management,BBM)

五、ECC - 校验和纠错

六、Interleaving - NAND 交叉存取技术

正文开场:

一、 预留空间(Over-provisioning,OP)

预留空间一般是指用户不可操作的容量,为实际物理闪存容量减去用户可用容量。这块区域一般被用来做优化,包括磨损均衡,GC和坏块映射。

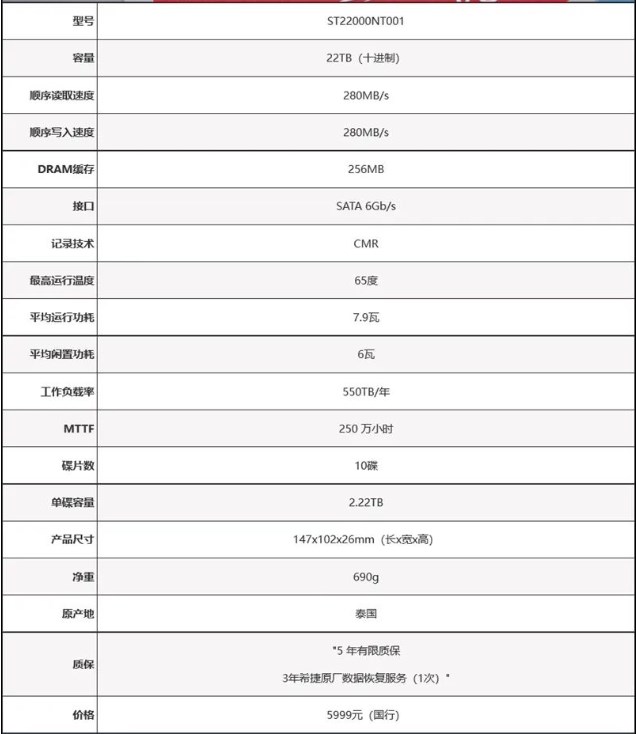

第一层为固定的7.37%,这个数字是如何得出的哪?我们知道机械硬盘和SSD的厂商容量是这样算的,1GB是1,000,000,000字节(10的9 次方),但是闪存的实际容量是每GB=1,073,741,824,(2的30次方) ,2者相差7.37%。所以说假设1块128GB的SSD,用户得到的容量是128,000,000,000字节,多出来的那个7.37%就被主控固件用做OP了。

第二层来自制造商的设置,通常为0%,7%和28%等,打个比方,对于128G颗粒的SandForce主控SSD,市场上会有120G和100G两种型号卖,这个取决于厂商的固件设置,这个容量不包括之前的第一层7.37%。

第三层是用户在日常使用中可以分配的预留空间,像Fusion-IO公司还给用户工具自己调节大小来满足不同的耐用度和性能,而用户也可以自己在分区的时候,不分到完全的SSD容量来达到同样的目的。

预留空间虽然让SSD的可用容量小了,但是带来了减少写入放大,提高耐久,提高性能的效果。

二、 Trim

TRIM是一个ATA指令,由操作系统发送给SSD主控制器,告诉它哪些数据占的地址是”无效“的。

要明白什么是Trim和为什么它很重要,需要先知道一点文件系统的知识。

当你在电脑里删除一个文件的时候,操作系统并不会真正的去删除它。操作系统只是把这个文件地址标记为“空”,可以被再次使用,这意味着这个文件占的地址已经是“无效”的了。这就会带来一个问题,硬盘并不知道操作系统把这个地址标记为”空“了,机械盘的话无所谓,因为可以直接在这个地址上重新覆盖写入,但是到了SSD上问题就来了。

NAND需要先擦除才能再次写入数据,要得到空闲的NAND空间,SSD必须复制所有的有效页到新的空闲块里,并擦除旧块(垃圾回收)。如果没有Trim,意味着SSD主控制器不知道这个页是”无效“的,除非再次被操作系统要求覆盖上去。

这里要强调下,Trim只是条指令,让操作系统告诉SSD主控制器这个页已经“无效”就算完了,并没有任何其它多余的操作,对Trim后的优化其实是垃圾回收在干活。Trim能够减少写入放大,因为主控制器不需要复制已经被操作系统定义为“无效”的页(没Trim的话,主控就因为不知道,而认为这个页“有效”)到“空白块”里,这同时代表复制的“有效”页变少了,垃圾回收的效率提高了,SSD性能下降的问题也减弱了。

所以说Trim的奥秘在于它能大量减少“有效”页的数量,大大提升垃圾回收的效率。

相对于企业级市场,在消费级的SSD里,Trim显得更为重要,企业级的SSD大部分都带有相当大的OP(备用空间)空间,能够提升一部分的垃圾回收效率。而消费级SSD一般OP都比较小,所以需要Trim来保证垃圾回收的效率。

Trim指令只有在操作系统进行删除、格式化等操作时候才会发送。Trim指令目前还不支持发送给RAID阵列中的SSD。(操作系统下进行的软件RAID可以支持)。

Trim的支持需要3个要素:

1.SSD主控制器和当前搭配的固件需要支持Trim命令接收。

2.当前操作系统需要支持Trim指令发送。(Win7/2008R2及后续版本)

3.当前使用的磁盘驱动程序必须支持Trim命令传输。

只有同时满足以上3个条件,才能做到系统Trim命令发送,驱动传输Trim命令,SSD固件接收到传输来的Trim命令。

Trim目前不支持以下几种情况:(可能还有更多)

1. Trim目前不支持RAID阵列中的SSD。(操作系统下进行软件RAID除外)

2. Trim目前不支持磁盘镜像文件内操作。(VM等虚拟机软件使用的虚拟磁盘文件)

3. Trim目前不支持加密的文件系统。(以防止暴露加密文件系统信息)

三、 写入放大(Write amplification,WA)

因为闪存必须先擦除才能写入(我们也叫“编程“),在执行这些操作的时候,移动(或覆盖)用户数据和元数据(metadata)不止一次。这些多次的操作,不但增加了写入数据量,减少了SSD的使用寿命,而且还吃光了闪存的带宽(间接地影响了随机写入性能)。

早在2008年,Intel公司和Silicon Systems公司(2009 年被西部数字收购)第一次提出了写入放大并在公开稿件里用到这个术语。他们当时的说法是,写入算法不可能低于1,但是这种说法在2009年被 SandForce打破,SandForce说他们的写入放大是0.55。

最简单的例子,比如我要写入一个4KB的数据,最坏的情况就是,一个块里已经没有干净空间了,但是有无效数据可以擦除,所以主控就把所有的数据读到缓存,擦除块,缓存里更新整个块的数据,再把新数据写回去,这个操作带来的写入放大就是: 我实际写4K的数据,造成了整个块(1024KB)的写入操作,那就是256倍放大。同时带来了原本只需要简单的写4KB的操作变成闪存读取 (1024KB),缓存改(4KB),闪存擦(1024KB),闪存写(1024KB),造成了延迟大大增加,速度慢是自然了。所以说写入放大是影响 SSD随机写入性能和寿命的关键因素。

用100%随机4KB来写入SSD,目前的大多数SSD主控,在最坏的情况下写入放大可以达到20以上。如果是100%持续的从低LBA写到高LBA的话,写入放大可以做到1,实际使用中写入放大会介于2者之间。用户还可以设置一定的预留空间来减少写入放大,假设你有个128G的SSD,你只分了64G 的区使用,那么最坏情况下的写入放大就能减少约3倍。

影响写入放大的因素

许多因素影响SSD的写入放大。下面我列出了主要因素,以及它们如何影响写放大。

1. 垃圾回收(GC) Garbage collection ---

虽然增加了写入放大(被动垃圾回收不影响,闲置垃圾回收影响),但是速度有提升。这个比较特殊的算法用来整理,移动,合并,擦除闪存块来提升效率。

2. 预留空间(OP) Over-provisioning ---

减少写入放大,好。(预留空间越大,写入放大越低)在SSD的闪存上划出一部分空间留给主控做优化,用户不能操作的空间。

3. TRIM ---

开启后可以减少写入放大,好。一个ATA指令,由操作系统发送给SSD主控,告诉主控哪些数据是无效的并且可以不用做垃圾回收操作。

4. 可用容量 ---

减少写入放大,好。(可用空间越大,写入放大越低)用户使用中没有用到的空间,需要有Trim支持,不然不会影响写入放大。 (某些主控制器算法只支持对OP区垃圾回收,这样就不会影响)

5. 安全擦除Secure Erase ---

减少写入放大,好。清除所有用户数据和相关元数据,让SSD重置到初始性能。

6. 持续写入Sequential write ---

减少写入放大,好。理论上来说,持续写入的写入放大为1,但是某些因素还是会影响这个数值。

7. 随机写入Random writes ---

提高写入放大,不好。随机写入会写入很多非连续的LBA,将会大大提升写入放大。

8. 磨损平衡(WL) Wear Leveling ---

直接提高写入放大,不好。确保闪存的每个块被写入的次数相等的一种机制。

四、 坏块管理(Bad block management,BBM)

不管磨损平衡算法如何聪明,在运作中都会碰到一个头痛的问题,那就是坏块,所以一个SSD必须要有坏块管理机制。何谓坏块?

一个NAND块里包含有不稳定的地址,不能保证读/写/擦的时候数据的准确性。坏块分出厂坏块和使用过程中出现的坏块,和机械盘的坏块表一样(P表和G表),SSD也有坏块表。

出厂坏块的话,在坏块上会有标记,所以很容易就能被识别,后期使用中出现的坏块就要靠主控制器的能力了,一般来说,越到NAND生命的后期(P/E数开始接近理论最大值),坏块就会开始大量出现了。

一般来说NAND出厂都包含坏块,不过厂商有个最小有效块值(NvB-minimum number of valid blocks),拿Intel的34nm MLC L63B来说,1个die上4,096个块里至少要有3,936个块是好的,从这上面可以知道,虽然出厂的NAND可能有坏块,但是厂商保证在正常生命周期里,好块数不会低于3936个块。而且每个die的第一个块地址(00h)在出厂时是必须保证好的(ECC后,这个块必须有效)。

NAND出厂前都会被执行擦除操作,厂商会在出货前会把坏块标记出来(厂商会在坏块的第一个页的SA区上打上标记。) 这样坏块管理软件就能靠监测SA区标记来制作坏块表。

SA区(页中4096~4319的区域,用户不可访问,主要用来存放ECC算法,坏块信息,文件系统资料等。)由于在使用中会产生坏块,所以SSD的每次编程/擦除/复制等操作后都要检查块的状态。对颗粒的ECC要求也要达到厂商的标准以上(主控强不强,看ECC能力也是一个参考)。坏块管理和平衡磨损算法是必须的。

五、 ECC - 校验和纠错

ECC的全称是Error Checking and Correction,是一种用于Nand的差错检测和修正算法。由于NAND Flash的工艺不能保证NAND在其生命周期中保持性能的可靠,因此,在NAND的生产中及使用过程中会产生坏块。

为了检测数据的可靠性,在应用 NAND Flash的系统中一般都会采用一定的坏区管理机制,而管理坏区的前提是能比较可靠的进行坏区检测。

如果操作时序和电路稳定性不存在问题的话,NAND Flash出错的时候一般不会造成整个Block或是Page不能读取或是全部出错,而是整个Page中只有一个或几个bit出错,这时候ECC就能发挥作用了。

不同颗粒有不同的基本ECC要求,不同主控制器支持的ECC能力也不同,理论上说主控越强ECC能力越强。

六、 Interleaving - NAND 交叉存取技术

Nand Flash的访问操作过程包括三项:

访问操作 = 命令输入操作+I/O操作+Array传输操作

第一项的操作时间所占比例很小,在性能估算中可以忽略。

所以,通常认为:访问时间 = I/O时间+ Array传输时间

在上一代NANDFlash中,第一项占的比例最大,是第二项的4-5倍。

每一个Plane对应一个Page大小的缓冲(dataregister)和一个Page大小的缓存(cacheregister)。数据写入的顺序是:I/O-> cache register -> data register ->Plane(数据读出的顺序刚好相反)。

缓冲(dataregister)与缓存(cacheregister)之间的数据传输速度很快,dataregister可以把I/O操作和Array操作分隔开,形成I/O操作和Array操作的“两级流水线”。

4个Plane对应4组缓冲与缓存,每一组可以分别操作。2个Plane交替操作,可以实现“乒乓操作”,达到2倍的Array访问带宽。4个Plane交替操作,可以实现“乒乒乓乓操作”,达到4倍的Array访问带宽。

交错操作可以成倍提升NAND的传输率,因为NAND颗粒封装时候可能有多Die,多Plane(每个plane都有4KB寄存器),Plane操作时候可以交叉操作(第一个plane接到指令后,在操作的同时第二个指令已经发送给了第二个plane,以此类推),达到接近双倍甚至4倍的传输能力。

结语:

这里小编介绍了一部分的专有名词解释,后面小编还会为大家介绍更多的专业名词,敬请期待哦~!

对于本文你有什么看法或建议呢?欢迎留言哦~!

电子发烧友App

电子发烧友App

评论