《通信原理》课程项目报告

题 目: 基于开发板的通信系统

组 号:

任课教师:

组 长:

组 员:

组 员:

组 员:

组 员:

联系方式:

二零一九年 2 月 23 日

一、实施方案

设计要求:

在给定的开发板DE10-Lite上,完成以下任务:

第一级:完成数模转换、二进制调制解调(不含2ASK)(60分)

第二级:完成多进制调制解调、或载波同步(80分)

第三级:同时完成多进制调制解调和载波同步(90分)

单项加分:载波是正弦波,或频率硬件可调,或系统可以实现其他功能(每个10分)

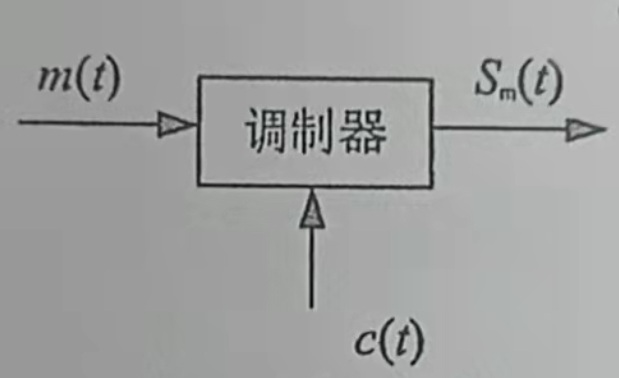

实现思想:

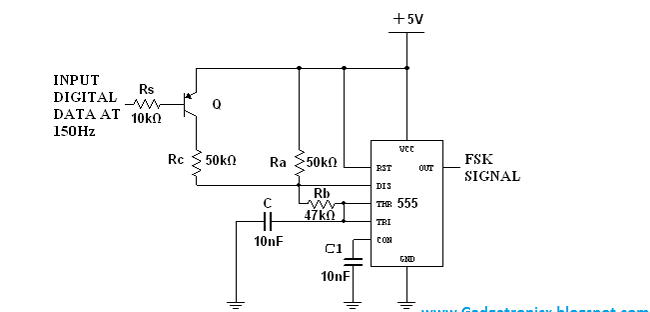

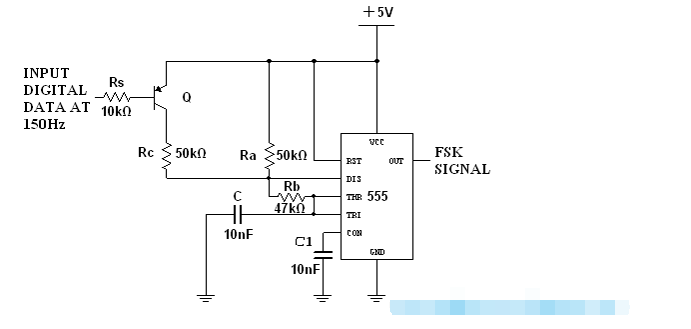

使用伪随机序列模拟基带信号进行FSK调制,通过DA输出调制波形;再接入AD口模拟信号接收端,对AD采样的信号进行解调,恢复出原始基带信号,并与原始信号进行比较。

在应用熟练软件之后,根据相同的思路做了多进制FSK,对多进制的效率有了更深的体会。

二、实施过程及结果分析

拿到板子之后,我们组内讨论得出:做FSK调制解调;一是便于观察、演示,二是解调手段多样,便于板子上实现。

不过初期组内熟悉quartus和verilog编程的并不多,而且对项目要求并不是很了解,所以前几周更多的是学习verilog以及熟悉软件。在做过通信原理实验的同学帮助下,算是知道了FSK是怎么一回事,紧接着便着手初步的调制。

在中期的时候我们总算明白了该怎么起手去做:利用FPGA板子做出数字的正弦波,再用基带信号去进行键控调制。

不过由于当时没有DA模块再加上对quartus的不熟悉,一切都只是简单的尝试,而且只能花费时间先去学仿真软件modelsim,以期望能仿真出一个正弦波。

网上也各自找了怎么实现数字正弦波,一般的做法是要写ROM模块,通过累加地址依次输出一个一个数据,数据的来源则是通过matlab实现。

最初感觉很复杂,各种各样的软件要联合起来,大家都不大愿意去做,时间也越来越少,只有沉下心去一点点实现。

中途modelsim软件又出现各种问题,库文件不全,无法仿真,在网上找了很久找到一个笨办法,每次仿真时都要手动重新选择自己生成的库文件:

https://wenku.baidu.com/view/67f7dbcb05a1b0717fd5360cba1aa81144318f00.html

在枯燥的重复操作中算是熟悉了基本的编程以及仿真方法,百度了很多资料,采用读取ROM的方法总算是生成了初步的正弦载波,踏出了第一步,仿真图如下:

其中使用到来自matlab生成的mif文件作为数据源,matlab代码如下:

clear;

%生成数据

depth = 64;

width = 8;

index = 0:2 * depth - 1;

value = 0.5*sin(2*pi*index/depth) + 0.5;

value = im2uint8(value);

%===============================开始写mif文件===============================

addr=0:2 * depth-1;

str_width=strcat('WIDTH=',num2str(width));

str_depth=strcat('DEPTH=',num2str(depth));

fid=fopen('data2.mif','w'); %打开或者新建mif,存放位置和文件名任意

%如果只写文件名,则在当前目录下建立此文件

fprintf(fid,str_width);

fprintf(fid,';\n');

fprintf(fid,str_depth);

fprintf(fid,';\n\n');

fprintf(fid,'ADDRESS_RADIX=HEX;\n'); %因为下面的数据输入我选的是16进制,

fprintf(fid,'DATA_RADIX=HEX;\n\n');

fprintf(fid,'CONTENT BEGIN\n');

fprintf(fid,'\t%X : %X;\n',[addr;value]); %开始写数据了

fprintf(fid,'END;\n');

fclose(fid);

就是用128个点的数据去拟合一个周期的正弦波,同时这里用了数字图像处理的一个函数im2uint8,将0~1的值直接转化为0~255的8位二进制值。

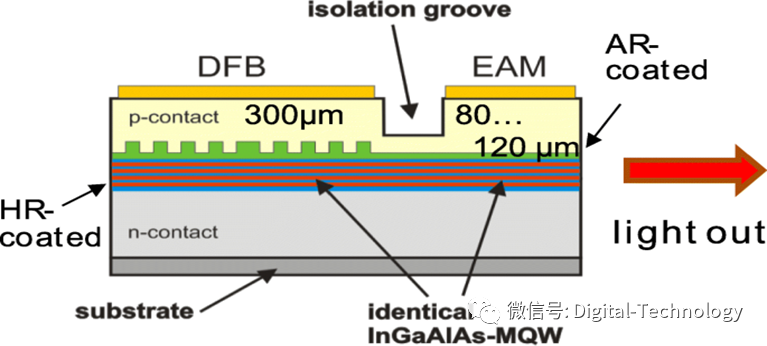

仿真结束后,实际电路我们打算用FPGA的锁相环PLL将时钟扩展到128M,再去驱动这个ROM模块,这样就能生成1MHz的正弦载波了。

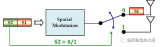

调用的过程中,我们也了解到FPGA一大方便之处:调用IP核。很多常用模块都可以直接通过调核来实现相应功能,像之前实现的正弦载波其实可以直接调用NCO生成。

依靠着强大的百度,我们学会了调用PLL,成功生成128M时钟驱动ROM实现了1MHz正弦波,并初次使用到了FPGA强大的“内置示波器signal tap”:

然后简单实现了一个伪随机序列,并编写了选通输出模块,两路载波分别为1M、2M,成功完成了2FSK的调制。

放假前夕,我们组拿到了ADDA子卡,可以通过DA输出、信道传输后进行AD采样来模拟接收了。

假期讨论中我们遇到了一个很严重的问题,DA发送没问题,AD接收有问题,我们按照ADDA子卡文档上进行操作但观察到的实际波形却是:

第三行是调制输出给DA口的,第二行是AD接收的,我们一度怀疑自己设置错误了,或者时钟没给正确。经过一系列排查,我们发现是频率的问题。这个“信道”就像是一个低通滤波器,频率越高衰减越严重。

因此我们不得不改变原来制定的1M、2M,将频率降低到能够演示的范围。最后直接用10M时钟驱动ROM模块得到78k、156k的两路载波,而随机序列则是10k,也能满足要求。

其调制实际波形通过示波器查看:

可以看到测量频率为78k,与设计相符,不过这个正弦波很明显可以看出一些不连续(台阶),放大后观察:

这是因为一个周期实际上只用了128个点去近似模拟,这也是我们精度不高的原因。之后做MFSK的时候,已经熟悉了各种操作,通过调用NCO数控振荡器生成的载波就很平滑,如下:

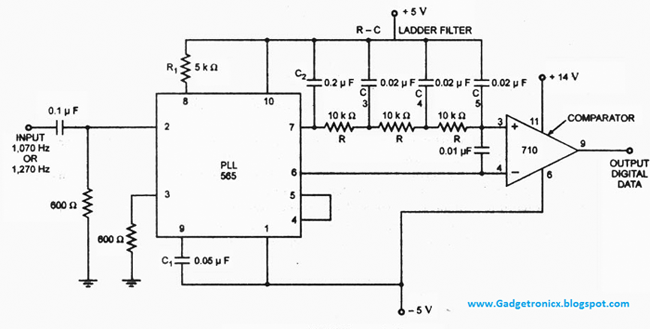

解调部分我们使用的是非相干解调,将AD接收的信号分两路,分别通过对应的带通滤波器,经过全波整流,再低通滤波即可提取出两路信号的包络,对两路信号进行抽样判决即可解调出原始基带信号,就是按照书中原理实现的。

这里又牵扯到一个问题,滤波器的实现,查了很多网上的资料,它们一般都是调用的FIR Compiler这个一代IP核,而quartus16给的已经是FIR II这个IP核,有一些不同。

我们借助一代的资料再加上自己的摸索最终实现了FIR滤波器,它的实现同样也要借助于matlab的数字滤波器设计,好在matlab集成了一个fdatool可以方便地给出我们需要的滤波器参数。

一般工程上实现滤波器不是我们学过的窗函数等方法,用的最多的是等纹波法,这些都可以直接借助fdatool,十分方便。

利用matlab得到的滤波器系数,设置好对应的采样频率、输出位数就成功地实现了FIR滤波器的调用:

最后得到的两路波形,由于2FSK的特性,判决门限就设置为0,两路信号比较就可以得到输出的二进制波形。

不过这里还有最后一个问题:实际应用往往需要得到二进制比特流,这就需要一个定时脉冲去抽样输出最终的二进制比特流信息。

我们组参考了《数字调制解调技术的MATLAB与FPGA实现AlteraVerilog版》一书,利用我们判决输出的二进制波形,实现了一个简单的“位同步定时”,能够比较好地抽样输出,完成2FSK的解调,最终效果如下:

第一行是模拟的基带信号,第三行是DA输出的调制波形,第二行是AD采样进来的信号(模拟接收端),第四、第五行分别是通过对应带通滤波器的信号,第六、第七行是上面两行提取包络(全波整流、低通)波形,第八行是六、七行相减,判决前的波形;以0为门限判决得到第九行的二进制波形,但这并不是数据流。

调用位定时模块,利用第九行的二进制波形得到了位定时脉冲(第十行),可以发现它的相位并不是固定的,在超前和滞后之间来回跳变,不过下降沿是比较稳定的,取下降沿抽样输出得到了最终的解调信号(最下面一行)!

做完这些后,整体流程就比较熟悉了,我们又做了一个简单的4进制FSK,原理基本相同,不再赘述,直接上signal tap波形:

唯一不同点就是用了四种频率的载波:第一行基带数据(四进制),第二行DA输出调制波形,第三行AD采样波形(可以明显发现频率越大衰减越大),下面的还是带通、提取包络的波形,原理完全一样。

最后解调出来的4进制信号与原始基带信号比较:

比较好地恢复了基带数据,完成了多进制调制解调。

三、项目总结

这次项目算是大学以来最大的挑战之一了。最开始目标不明、软件不会,一点点自学软件以及verilog语言,之后能熟练地使用软件完全都是时间堆起来的,quartus、modelsim、matlab等软件联合使用,最终完成了这次的项目。

做这次项目还理解到了FPGA开发的流程和它“模块化”设计的理念,可以进行很好的分工、分模块设计,最后在顶层文件里调用小模块搭建起整个系统,这是不同于以往项目的。

在使用ADDA子卡之前我们全是使用的modelsim来进行仿真验证,而使用ADDA模块后由于仿真无法实现,我们换成了signal tap直接在板子上验证结果,也使得我们对这个“内嵌示波器”有了充足的了解。

项目中也体会到一点:书本上通俗易懂的原理在实际工程中往往不是那么好实现的。我们使用的是非相干解调,也有“不会载波同步”的原因在里面,书中直接给出的同步载波却是整个项目的最大难题,比较遗憾的是这个没有实现,只参考书后完成了“位同步定时脉冲模块”。

最后做的4进制调制解调也让我们更深刻地理解了通信系统的“取舍难题”,我们做的MFSK,传输效率确实高了不少,但其耗费的资源(滤波器、尤其是带宽资源)增加的不是一点半点。尤其是高速通信的当今,带宽资源更是稀缺,也难怪MFSK实际中基本没有应用,而基于PSK发展起来的QDPSK、QAM等技术得到了广泛的应用,确实有着其优势所在。

四、小组分工

参考文献:

[1] 杜勇. 《数字调制解调技术的MATLAB与FPGA实现AlteraVerilog版》. 电子工业出版社,2015.3

[2] 李颖洁等. 《现代通信原理——信息传输的基本原理》.清华大学出版社,2007.5

电子发烧友App

电子发烧友App

评论