电子发烧友网报道(文/吴子鹏)日前,在华为硬、软件工具誓师大会上,华为轮值董事长徐直军表示,华为芯片设计EDA工具团队联合国内EDA企业,共同打造了14nm以上工艺所需EDA工具,基本实现了14nm

2023-03-25 00:18:46 7392

7392 目前,苹果、高通、联发科等世界知名厂商已与台积电能达成紧密合作,预示台积电将继续增加 5nm产能至该节点以满足客户需求,这标志着其在3nm制程领域已经超越竞争对手三星及英特尔。

2024-03-19 14:09:03 56

56 本帖最后由 jf_50240986 于 2024-3-8 22:51 编辑

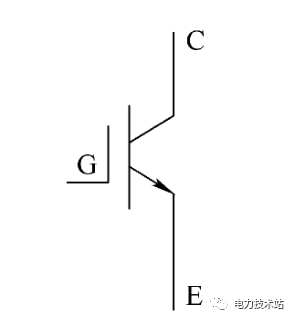

串接NPN型晶体管的情况。晶体管基极要求注入电流,产生电流的电压必须高于(Vo+Vbe),约为(Vo+1)。若基极

2024-03-06 20:49:11

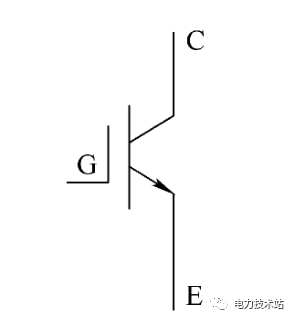

达林顿晶体管(Darlington Transistor)也称为达林顿对(Darlington Pair),是由两个或更多个双极性晶体管(或其他类似的集成电路或分立元件)组成的复合结构。通过这种结构,第一个双极性晶体管放大的电流可以进一步被放大,从而提供比其中任意一个双极性晶体管高得多的电流增益。

2024-02-27 15:50:53 503

503

双极性晶体管是利用两种离子导电,空穴和自由电子,但是对于一个实际存在的系统,其整体上是呈现电中性的,当其中的电子或者空穴移动形成电流时,与之对应的空穴或者电子为什么不会一起随着移动?

这个问题困扰

2024-02-21 21:39:24

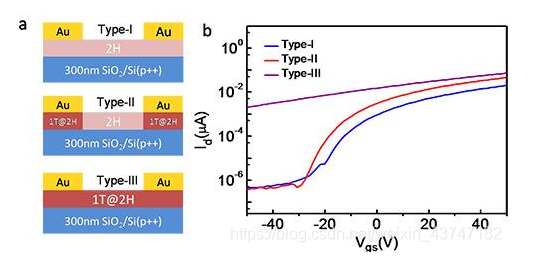

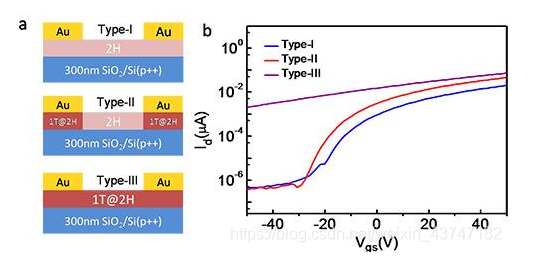

近日,西安电子科技大学郝跃院士团队刘艳教授和罗拯东副教授在超陡垂直晶体管器件研究方面取得重要进展,相

2024-02-20 18:22:20 793

793

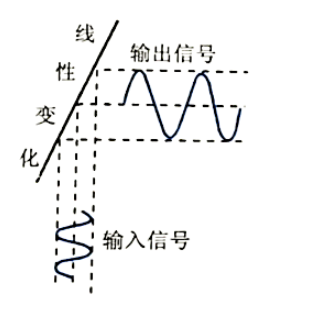

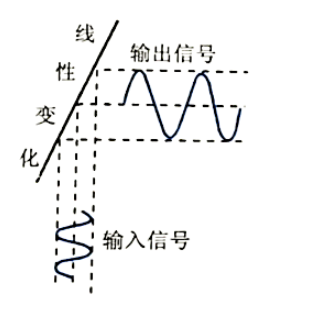

加载合适的偏置电流,必须牢固地掌握晶体管的特性曲线,正确地读取偏置电流的大小,要能在尽可能广的范围内加载偏置电流。

2024-02-05 15:10:21 108

108

三相异步电动机的转向由电源相序、电机的外部连接方式、启动方法以及电机的机械结构等多个因素共同决定。

2024-02-03 14:50:40 555

555 台中科学园区已初步规划A14和A10生产线,将视市场需求决定是否新增2nm制程工艺。

2024-01-31 14:09:34 241

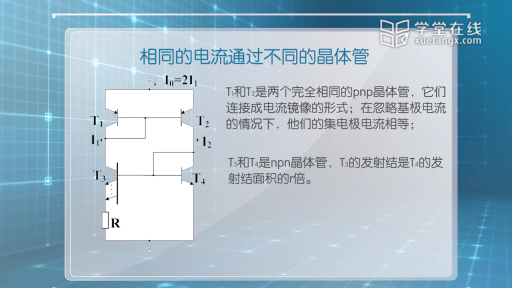

241 晶体管并联时,当需要非常大的电流时,可以将几个晶体管并联使用。因为存在VBE扩散现象,有必要在每一个晶体管的发射极上串联一个小电阻。电阻R用以保证流过每个晶体管的电流近似相同。电阻值R的选择依据

2024-01-26 23:07:21

面晶体管不导通时,上面晶体管能导通吗?下面发射结反偏,集电集或基本没有电流,上面晶体管是如何导通的?或者是输入信号的地、在什么地方?与NPN和PNP结构的地差在哪里,一般NPN PNP是双电源供电?正负双电源?

2024-01-25 22:28:59

据消息人士透露,台积电已经决定将其1nm制程厂选址在嘉义科学园区。为了满足这一先进制程技术的需求,台积电已向相关管理局提出了100公顷的用地需求。

2024-01-23 15:15:27 894

894 台积电在上月早些时候的IEDM 2023大会中宣布,计划推出包含高达1万亿个晶体管的芯片封装方案,此举与英特尔去年公布的规划相呼应。为达成这一目标,该公司正专注于N2和N2P的2nm级生产节点及A14和A10的1.4nm级制造工艺,预估将于2030年投入使用。

2024-01-23 10:35:06 1427

1427 放大,似于多路比较器的输出,NPN型晶体管多发射极分别接到比较器的输出端,集电极共用一路上拉电阻连接至电源,如果多路比较器有一路导通,则该多发射极晶体管集电极输出导通拉低,电平为低电平。

不知是否是我理解的这样?

2024-01-21 13:47:56

常用的半导体元件还有利用一个PN结构成的具有负阻特性的器件一单结晶体管,请问这个单结晶体管是什么?能够实现负阻特性?

2024-01-21 13:25:27

晶体管在基极和集电极之间并联电容有什么作用?是为了米勒电容吗、?但是米勒电容对三极管的开通有害的时候,为什么还要并联电容?电容不是越并越大,加大了等效米勒电容?

2024-01-19 22:39:57

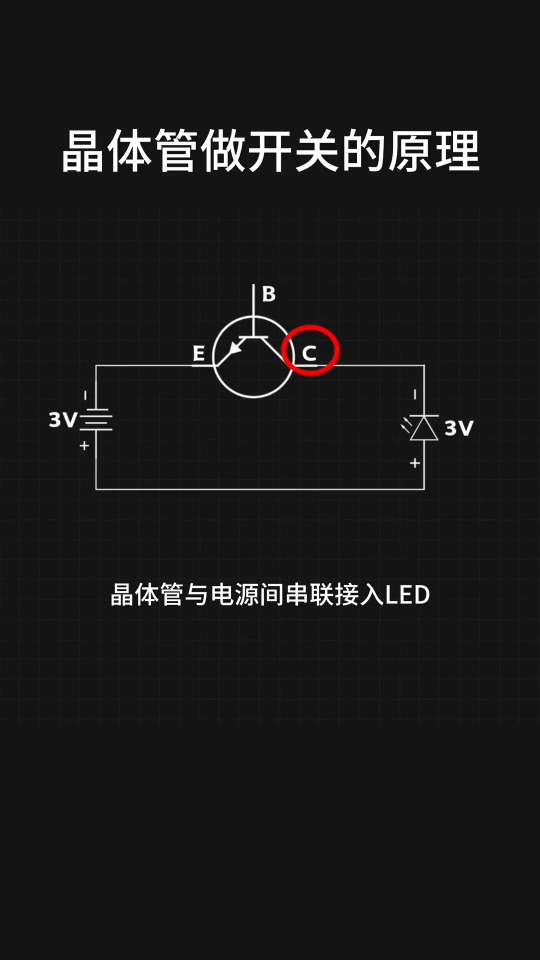

晶体管也就是俗称三极管,其本质是一个电流放大器,通过基射极电流控制集射极电流。

1、当基射极电流很小可以忽略不计时,此时晶体管基本没有对基射极电流的放大作用,此时可以认为晶体管处在关断状态

2、当基

2024-01-18 16:34:45

举例而言,一个结型场效应管,采用自偏置结构,即栅极和源极短接在一起源极也有一个电阻,在电源和漏极接一个负载,此时场效应管可以看做是一个互导放大器,压控电流源,请问此时这种电路的输入输出电阻应该怎么求

2024-01-15 18:06:15

对于一个含有晶体管,场效应管,运放的电路,该如何求解他的输入电阻和输出电阻,举例而言,在含有晶体管的电路射极跟随器中,求解输出电阻时,为什么要考虑基极的电阻和偏置电路的电阻,此时不应该在基极是二极管

2024-01-10 17:17:56

绝缘栅双极型晶体管(Insulated Gate Bipolar Transistor,简称IGBT绝缘栅双极型晶体管(Insulated Gate Bipolar Transistor,简称

2024-01-03 15:14:22 268

268

CFET结构“初露端倪”,让业界看到了晶体管结构新的发展前景。然而,业内专家预估,CFET结构需要7~10年才能投入商用。

2024-01-02 17:34:33 593

593

。它们主要包括晶体管(三极管)、存储单元、二极管、电阻、连线、引脚等。

随着电子产品越来越“小而精,微薄”,半导体芯片和器件尺寸也日益微小,越来越微细,因此对于分析微纳芯片结构的精度要求也越来越高,在芯片

2024-01-02 17:08:51

为达成此目标,公司正加紧推进N2和N2P级别的2nm制造节点研究,并同步发展A14和A10级别的1.4nm加工工艺,预计到2030年可以实现。此外,台积电预计封装技术,如CoWoS、InFO、SoIC等会不断优化升级,使他们有望在2030年前后打造出超万亿晶体管的大规模封装解决方案。

2023-12-28 15:20:10 355

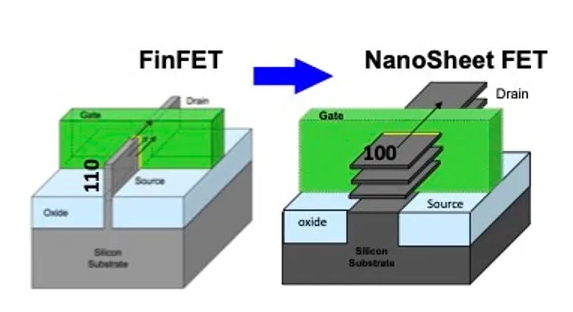

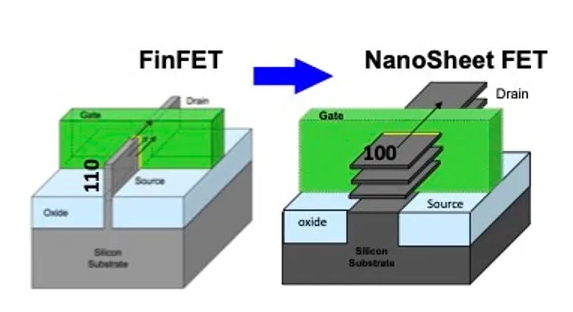

355 在经历了近十年和五个主要节点以及一系列半节点之后,半导体制造业将开始从 FinFET过渡到3nm技术节点上的全栅堆叠纳米片晶体管架构。 相对于FinFET,纳米片晶体管通过在相同的电路占位面积中增加

2023-12-26 15:15:11 167

167

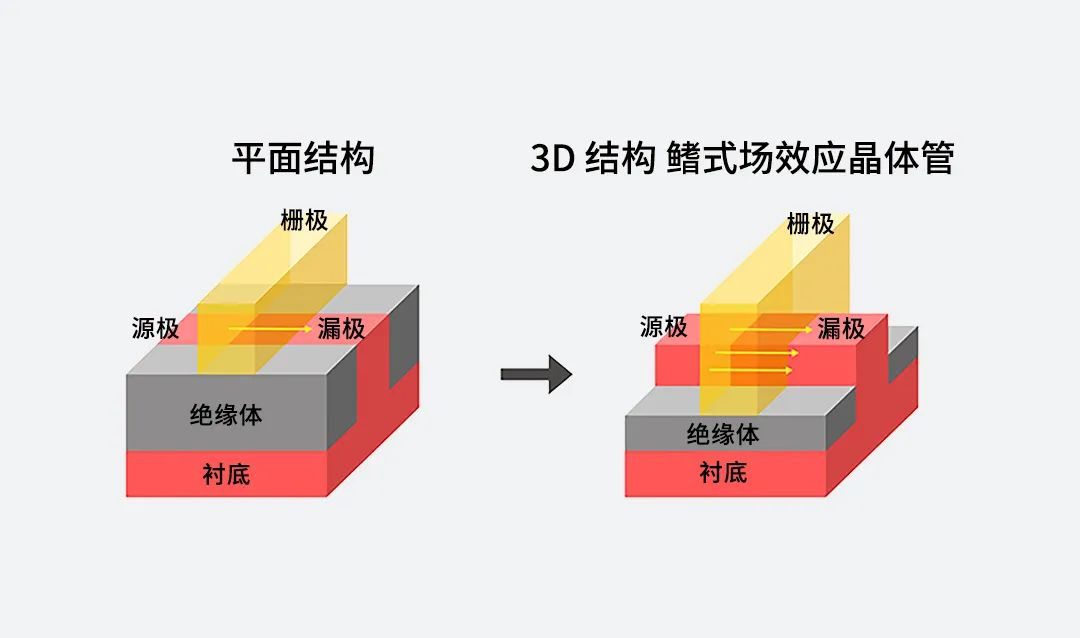

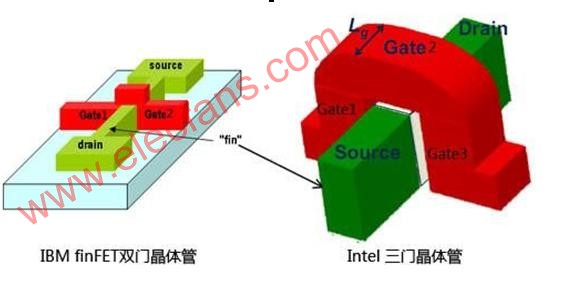

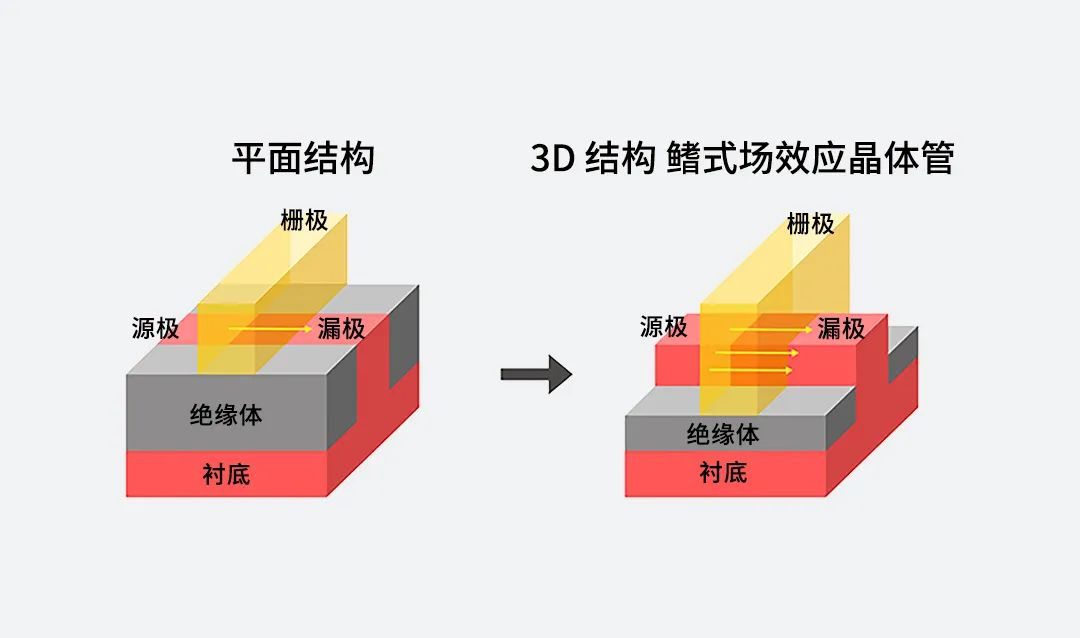

上次我的文章解释了所谓的7nm不是真的7nm,是在实际线宽无法大幅缩小的前提下,通过改变晶体管结构的方式缩小晶体管实际尺寸来达到等效线宽的效果那么新的问题来了:从平面晶体管结构(Planar)到立体

2023-12-19 16:29:01 239

239

级制程将按计划于2025 年开始量产。 根据 SemiAnalysis 的 Dylan Patel 给出的幻灯片,台积电的 1.4nm 制程节点正式名称为 A14。目前台积电尚未透露 A14 的量产

2023-12-19 09:31:06 318

318 年开始量产。 根据 SemiAnalysis 的 Dylan Patel 给出的幻灯片,台积电的 1.4nm 制程节点正式名称为 A14。IT之家注意到,目前台积电尚未透露 A14 的量产时间和具体

2023-12-18 15:13:18 191

191 此外,对于台积电的1.4nm制程技术,媒体预计其名称为A14。从技术角度来看,A14节点可能不会运用垂直堆叠互补场效应晶体管(CFET)技术。

2023-12-15 10:23:12 264

264 全面展开。同时,台积电重申,2nm 级制程将按计划于 2025 年开始量产。 据悉,台积电的 1.4nm 制程节点正式名称为 A14。目前台积电尚未透露 A14 的量产时间和具体参数,但考虑到

2023-12-14 11:16:00 733

733 晶体管的问世,是20世纪的一项重大发明,是微电子革命的先声。晶体管出现后,人们就能用一个小巧的、消耗功率低的电子器件,来代替体积大、功率消耗大的电子管了。晶体管的发明又为后来集成电路的降生吹响了号角。

2023-12-13 16:42:31 427

427

晶体管和电子管区别 晶体管和电子管是两种用于电子设备中放大和控制电流的重要元件。尽管它们在实现相同功能方面存在共同点,但它们在结构、工作原理和性能方面存在显着差异。在本文中,我们将详细介绍晶体管

2023-12-08 10:31:58 4940

4940 一键解锁!晶体管结构工艺发展历程

2023-12-07 09:48:17 243

243

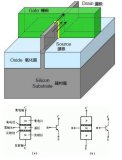

从平面晶体管结构(Planar)到立体的FinFET结构,我们比较容易理解晶体管尺寸缩小的原理。

2023-12-02 14:04:45 267

267

来至网友的提问:如何选择分立晶体管?

2023-11-24 08:16:54

我在进行AD8138ARM的热仿真,datasheet中只有结到环境的热阻JA的数据,我需要结到外壳的热阻Jc的数据,还有AD8138ARM放大器集成的晶体管数目是多少?

2023-11-21 06:54:43

双方的目标是,确立设计开发线宽为1.4m1纳米的半导体所必需的基础技术。这个节点需要不同于传统的晶体管结构,leti在该领域的膜形成等关键技术上占据优势。

2023-11-17 14:13:43 412

412 Tick-Tock,是Intel的芯片技术发展的战略模式,在半导体工艺和核心架构这两条道路上交替提升。半导体工艺领域也有类似的形式存在,在14nm/16nm节点之前,半导体工艺在相当长的历史时期里有着“整代”和“半代”的差别。

2023-11-16 11:52:25 963

963

前两代M1和M2系列芯片均采用5nm制程工艺,而M3系列芯片的发布,标志着苹果Mac电脑正式进入3nm时代。 3nm利用先进的EUV(极紫外光刻)技术,可制造极小的晶体管,一根头发的横截面就能容纳两百万个晶体管。苹果用这些晶体管来优化新款芯片的每个组件。

2023-11-07 12:39:13 310

310

N2,也就是2nm,将采用GAAFET全环绕栅极晶体管技术,预计2025年实现量产。 2nm芯片是指采用了2nm制程工艺所制造出来的芯片,制程工艺的节点尺寸表示芯片上元件的最小尺寸。这意味着芯片上的晶体管和其他电子元件的尺寸可以达到2纳米级别。 2nm芯片手机

2023-10-19 17:06:18 799

799 2nm芯片是什么意思 2nm芯片指的是采用了2nm制程工艺所制造出来的芯片,制程工艺的节点尺寸表示芯片上元件的最小尺寸。这意味着芯片上的晶体管和其他电子元件的尺寸可以达到2纳米级别。 更小的节点尺寸

2023-10-19 16:59:16 1958

1958 专业图书47-《新概念模拟电路》t-I晶体管

2023-09-28 08:04:05

电子发烧友网站提供《PZTA14-Q NPN达林顿晶体管产品手册.pdf》资料免费下载

2023-09-27 10:22:44 0

0 频特性是由它的物理结构和工作原理决定的。晶体管的结构包括三个区域:发射区、基区和集电区。当外加电压时,发射区的电子会进入基区,并增加基区电荷的密度。因此,基区的电荷密度会决定集电区的电流。晶体管的工作原理有两种

2023-09-20 16:43:22 631

631 的大部分时间里,用于制造芯片的工艺节点的名称是由晶体管栅极长度的最小特征尺寸(以纳米为单位)或最小线宽来指定的。350nm工艺节点就是一个例子。

2023-09-19 15:48:43 4475

4475

,单位为MHz。

倍频:表示主频与外频的比值。

制程:表示芯片上晶体管之间的连接导线的线宽,单位为纳米,数字越小水平越高。

缓存大小:包括一级缓存、二级缓存、三级缓存等,单位为MB。

架构:表示CPU

2023-09-05 16:42:49

华为发布首款5nm 5G SoC,集成153亿晶体管 在当今的数字时代,5G成为了一种越来越重要的通信技术,它能够大幅提升传输速度和低延时,以实现更高的数据传输质量。而华为公司最近发布了自家

2023-09-01 16:47:35 7012

7012 符号表示传统的电流流动。该晶体管中的电流方向是从发射极端到集电极端子。一旦基极端子与发射极端子相比被拖至低电平,该晶体管将导通。PNP晶体管的符号如下所示。

NPN晶体管

NPN也是BJT(双极结型

2023-08-02 12:26:53

该2通道混音器电路基于2n3904晶体管,该晶体管形成2个前置放大器。2通道混音器电路的第一个前置放大器具有高增益,可用于麦克风输入,第二个前置放大器可用于控制音频电平的输入。

这种双通道

2023-08-01 17:19:21

在半导体行业的最初几十年里,新的工艺节点只需缩小晶体管的物理尺寸并将更多晶体管塞到芯片上即可实现性能、功耗和面积增益,这称为经典缩放。集成电路工作得更好,因为电信号在每个晶体管之间传播的距离更短。

2023-07-16 15:47:43 413

413 “晶体管”现在可以分为多种类型,每种类型具有不同的功能和结构,例如FET、MOS FET、CMOS等也是广义上的晶体管。当然,它仍然是有源的,主要用于电压/信号放大和开关控制。在本文中,工程师将解释这种双极晶体管是什么,以及它的原理、机制和特点。

2023-07-07 10:14:49 2343

2343 MAT14是一款四通道单芯片NPN型晶体管,具有出色的参数匹配性能,适合精密放大器和非线性电路应用。MAT14的性能特征包括:在很宽的集电极电流范围内提供高增益(最小300)、低噪声(在100 Hz

2023-06-20 18:14:26

该路线图概述了标准 FinFET 晶体管将持续到 3nm,然后过渡到新的全栅 (GAA) 纳米片设计,该设计将在 2024 年进入大批量生产。Imec绘制了 2nm和A7(0.7nm)Forksheet设计的路线图,随后分别是A5和A2的CFET 和原子通道等突破性设计。

2023-06-14 09:31:34 911

911

的基础上,实现了国内14nm 晶圆芯片零的突破,并在梁孟松等专家的带领下,向着更加先进的芯片制程发起冲锋。 然而,最近在中芯国际的公司官网上,有关于14nm芯片制程的工艺介绍,已经全部下架,这让很多人心存疑惑,作为自家最为先进的

2023-06-06 15:34:21 17913

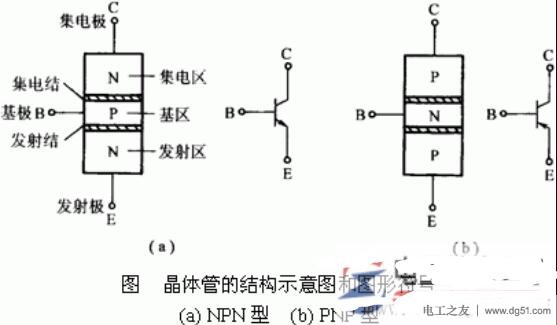

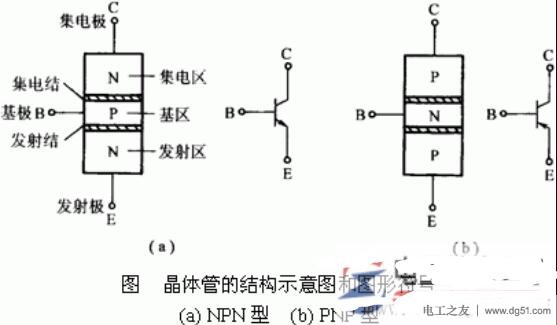

17913 今天为大家介绍晶体管由两个PN结构成,分为NPN型和PNP型两类,根据使用材料的不同,将晶体管分为NPN型锗管和NPN型硅管,PNP型锗管和PNP型硅管。

2023-06-03 09:29:11 1254

1254

我正在寻找摩托罗拉收音机 VHF 射频末级中使用的这些旧射频晶体管的数据表,有人可以帮我吗?

2023-05-30 07:40:02

结构上,数字晶体管有的在基极上串联一只电阻R1,有的在基极与发射极之间并联了一只电阻R2,大多数同时连接了R1和R2。随着电阻R1、R2的组合搭配的变化,数字晶体管的型号远比普通晶体管丰富多彩。

2023-05-29 16:46:57 288

288 双极型晶体管(Bipolar Junction Transistor,简称BJT)是一种半导体器件,它是一种基于电子和空穴的双极性导电性质的三极管。与场效应晶体管相比,双极型晶体管的控制电流较大,但具有高电流放大系数和高频特性等优点。

2023-05-17 15:23:13 4370

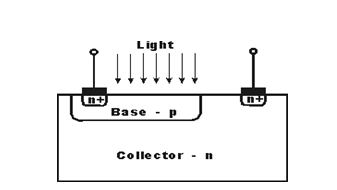

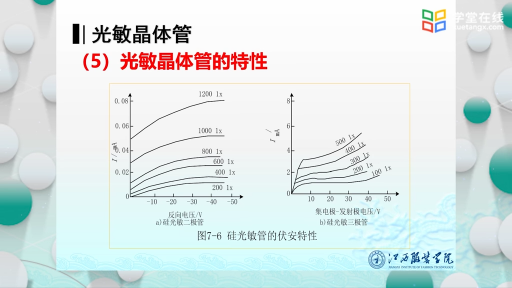

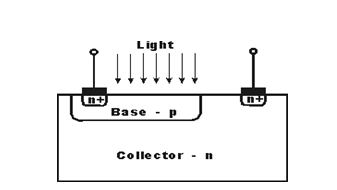

4370 光电晶体管是基极端子暴露的晶体管,来自撞击光的光子不会向基极发送电流,而是激活晶体管。这是因为光电晶体管由双极半导体制成,并集中在通过它的能量上。

2023-05-16 15:59:06 286

286

场效应晶体管是电压控制元件,因此和普通双极型晶体管相比,场效应晶体管具有输入阻抗高、噪声低、动态范围大、功耗小、易于集成等特点,这就决定了场效应晶体管与其它电子元件有异曲同工之妙。

2023-05-16 15:20:04 1366

1366

%。西安二厂预计将生产13.5万片,比之前的14.5万片减少了约7%。业界观察人士认为,三星选择砍掉部分NAND产能,因为当前内存市场形势惨淡。

【台积电28nm设备订单全部取消!】

4月消息,由于

2023-05-10 10:54:09

808nm 激光二极管 TO56封装 500mW

XL-808TO56-ZSP-500 、XL-TO18-785-120、XL-9402TO5-ZS-1W、XL-505TO56-ZSP-100

2023-05-09 11:23:07

单结晶体管随着电容的充电放电是如何形成自激振荡脉冲的?

2023-04-26 15:07:51

差分放大电路输入共模信号时

为什么说RE对每个晶体管的共模信号有2RE的负反馈效果

这里说的每个晶体管的共模信号是指什么信号 是指输入信号 还是指ie1 ie2 uoc ?

另外为什么是负的反馈

2023-04-25 16:15:31

双极结晶体管电路输入振幅变大为什么会导致失真呢?是什么原因呢?

2023-04-21 16:13:13

1 前言 大家好,我是硬件花园! 华为轮值董事长徐直军,在前些日子举行“突破乌江天险,实现战略突围”的软硬件开发工具誓师大会上表示,华为芯片设计EDA工具团队联合国内EDA企业,共同打造了14nm

2023-04-20 03:00:57 5418

5418 我正在寻找零件号“PCAL6408ABSHP”中有关工艺节点和晶体管数量的信息。NXP 网站上是否有一个位置可以找到 NXP 部件号的此类信息?

2023-04-19 09:27:44

西门子S7-200电源怎么看是继电器输出还是晶体管输出呢?

2023-04-18 10:08:03

西门子CPUSR30可以增加晶体管扩展模块控制步进电机吗?

2023-04-17 14:13:13

台积电的16nm有多个版本,包括16nm FinFET、16nm FinFET Plus技术(16FF +)和16nm FinFET Compact技术(16FFC)。

2023-04-14 10:58:15 636

636 采用晶体管互补对称输出时,两管基极之间有电容相连,为什么?c2有什么用??

2023-03-31 14:02:55

请问BJT工艺的线性稳压源为什么多是PNP型晶体管呢?

2023-03-31 11:56:49

有没有负触发导通正的晶体管呢?哪位大神知道请赐教。谢谢啦!

2023-03-31 11:47:46

我在设计 PCB 时犯了一个错误,我的一些晶体管在原理图上将集电极和发射极调换了。“正常”方式是有 1:基极,2:发射极,3:集电极,但我需要一个晶体管,1:基极,2:集电极,3:发射极。引脚号与此图像相关:你知道有这种封装的晶体管吗?我知道我可以将它倒置并旋转,但我想知道我是否可以正确使用一个。

2023-03-28 06:37:56

快讯:2023年全面验证华为14nm以上EDA工具 美国芯片法案限制细则公布 我们来看看近期的一些行业热点新闻: 华为14nm以上EDA工具国产化 华为轮值董事长徐直军透露了几个关键信息点:华为芯片

2023-03-27 16:27:18 4778

4778 工艺技术节点进入亚3 nm以后,垂直鳍片沟道架构的新器件开发仍备受关注,人们正在考虑制造基于垂直鳍式结构开发垂直围栅器件(VGAA)或垂直传输场效应晶体管(VTFET),以满足“后摩尔时代”芯片的更高集成度、高性能和低功耗发展要求,世界著名集成电路制造龙头公司IBM和三星已进行相关研发。

2023-03-27 11:25:40 1373

1373

电子发烧友App

电子发烧友App

评论