Cadence 设计系统公司日前宣布,汽车零部件生产商Denso公司在改用了Cadence定制/模拟与数字流程之后,在低功耗混合信号IC设计方面实现了质量与效率的大幅提升。将Cadence Encounter RTL-to-GDSII流程应用于设计的数字部分之后,Denso表示比之前采用的流程减小了10%的面积,功耗降低了20% 。在设计的模拟部分,根据多次测试的数据结果,Denso使用Cadence Virtuoso定制/模拟流程(6.1版)实现了30%的效率提升,并预计在实际设计上也有相同的改进。对于Denso来说,在生产效率与成品质量方面所获得的提升效果是显著的。

“在竞争激烈的汽车电子市场,可靠性是必要的前提,”Denso电子设备商业部经理Yoichi Oishi最近在CDNLive!日本技术会议期间演讲时说,“我们需要改进我们的设计工具,才能在不牺牲质量的前提下实现更高的芯片开发效率。采用了 Cadence Encounter和Virtuoso流程后,我们在芯片质量和产品上市时间方面都实现了我们的目标。”

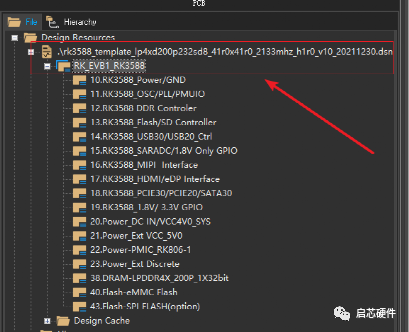

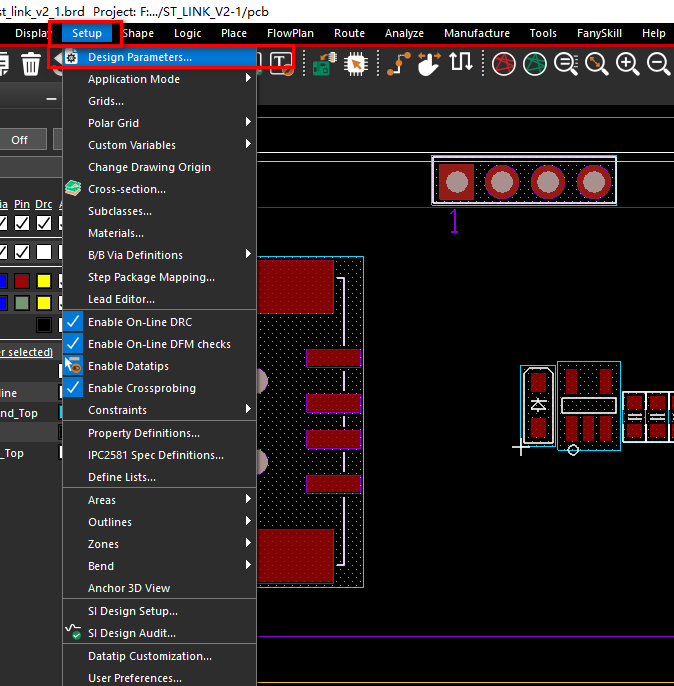

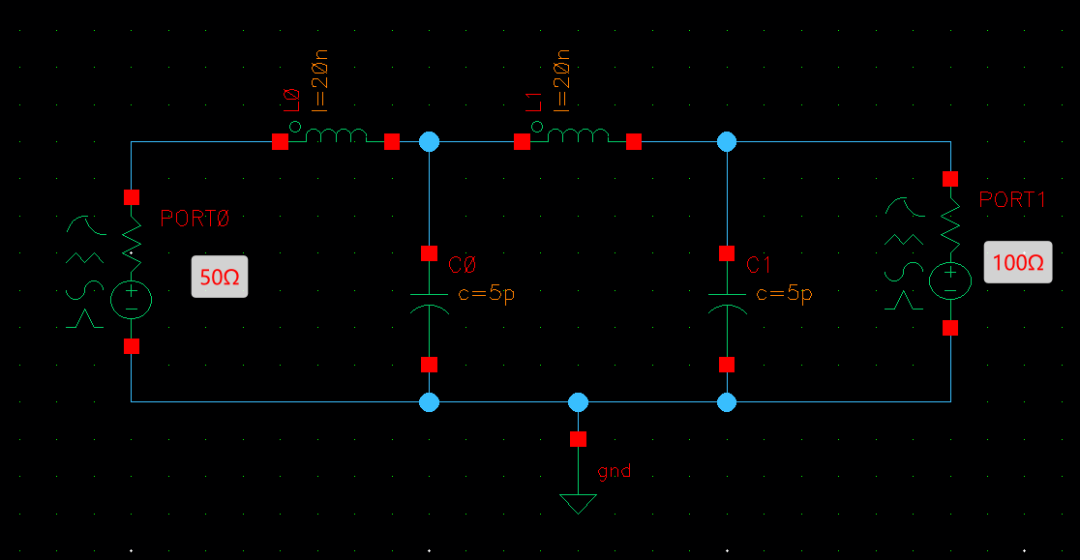

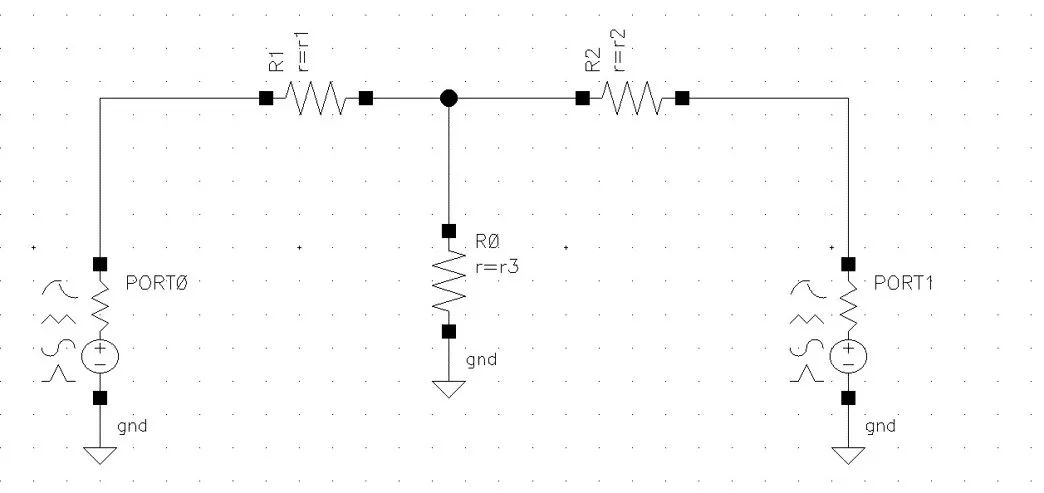

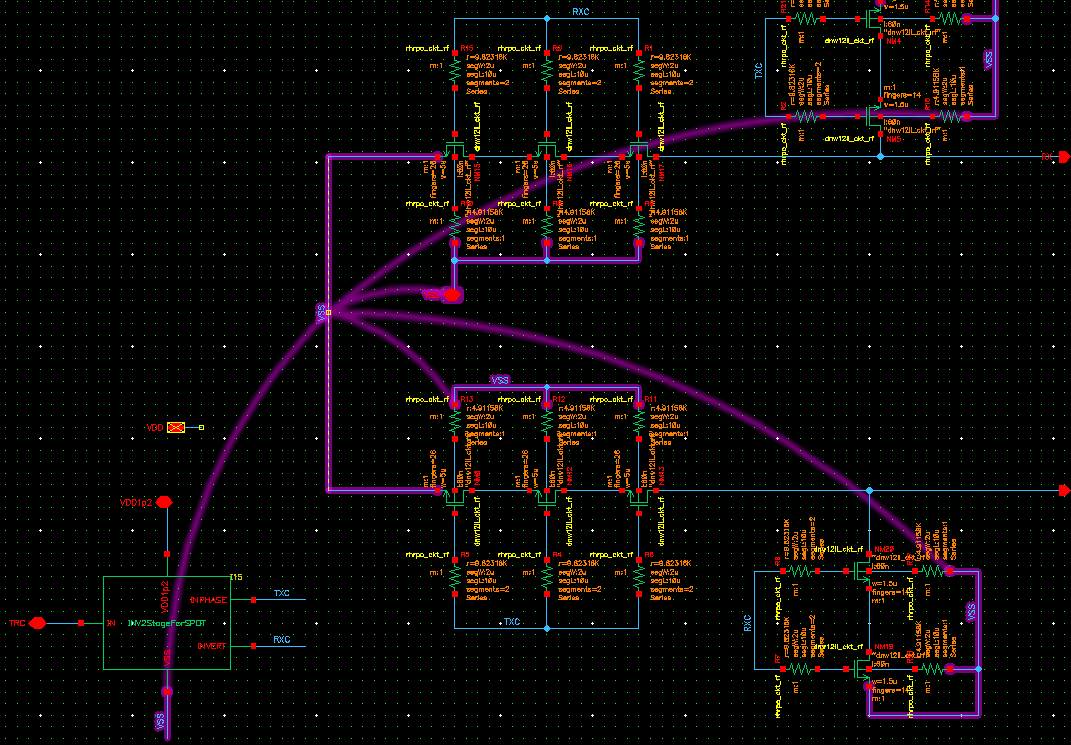

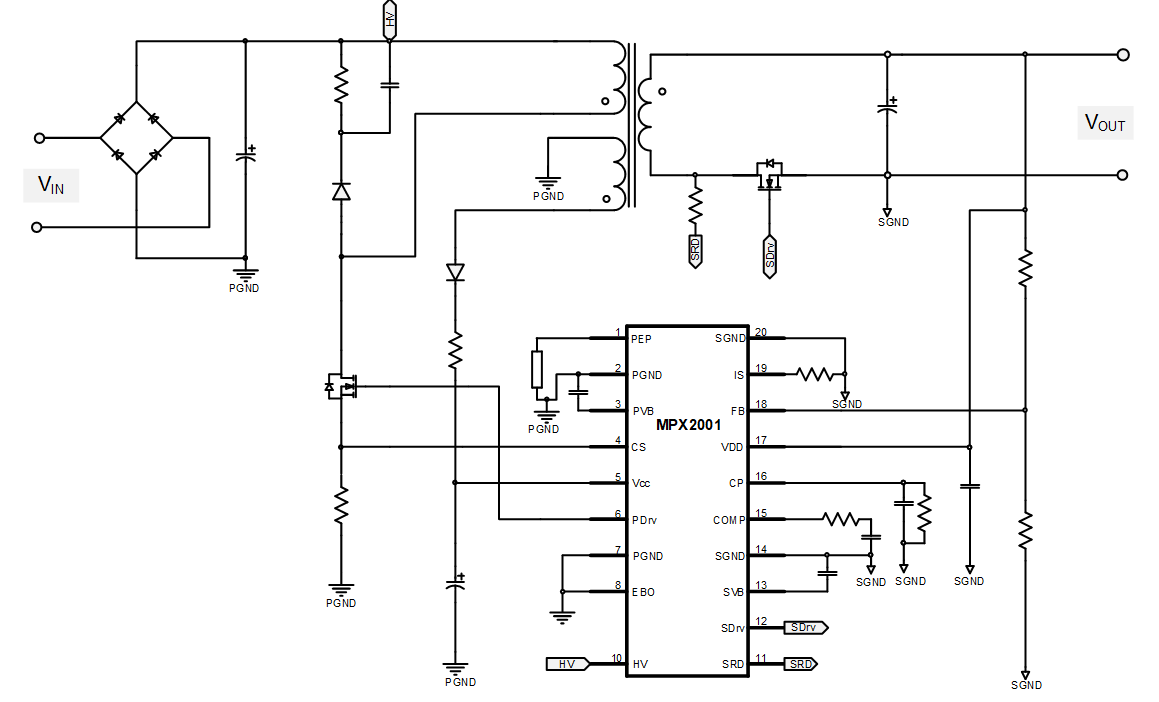

为实现高级节点设计数字部分的功耗、性能与面积的改良,Denso使用Encounter RTL-to-GDSII流程,其中包含Encounter RTL Compiler用于全局综合,以及用于设计实现的Encounter Digital Implementation System。在模拟部分,Denso在完整的定制/模拟流程中采用Virtuoso Schematic Editor、 Virtuoso Layout Suite 以及 Virtuoso Analog Design Environment,在规格驱动的多测试环境中,以灵敏度分析和电路参数优化,在整个定制布局中实现强大而中心明确的设计。

对于in-design与寄生提取签收,Denso使用了Cadence QRC Extraction,它与Virtuoso和Encounter流程紧密结合,实现更快的收敛以及迅速产品上市。从另一家供应商的技术更换为QRC Extraction之后,Denso能够消除文件界面,直接从Virtuoso的环境管理数据,实现了效率的提升与更快的产品上市时间。

“Cadence为诸如Denso这样的客户提供了完整的混合信号与低功耗设计方案 - 可以帮助他们改进关键指标,如功耗、性能与面积,”Cadence解决方案营销部主管Qi Wang说,“无论是应对高级工艺节点还是主流工艺尺寸,设计团队都可以用Cadence的流程实现具有竞争力的商业和市场目标。”

电子发烧友App

电子发烧友App

评论