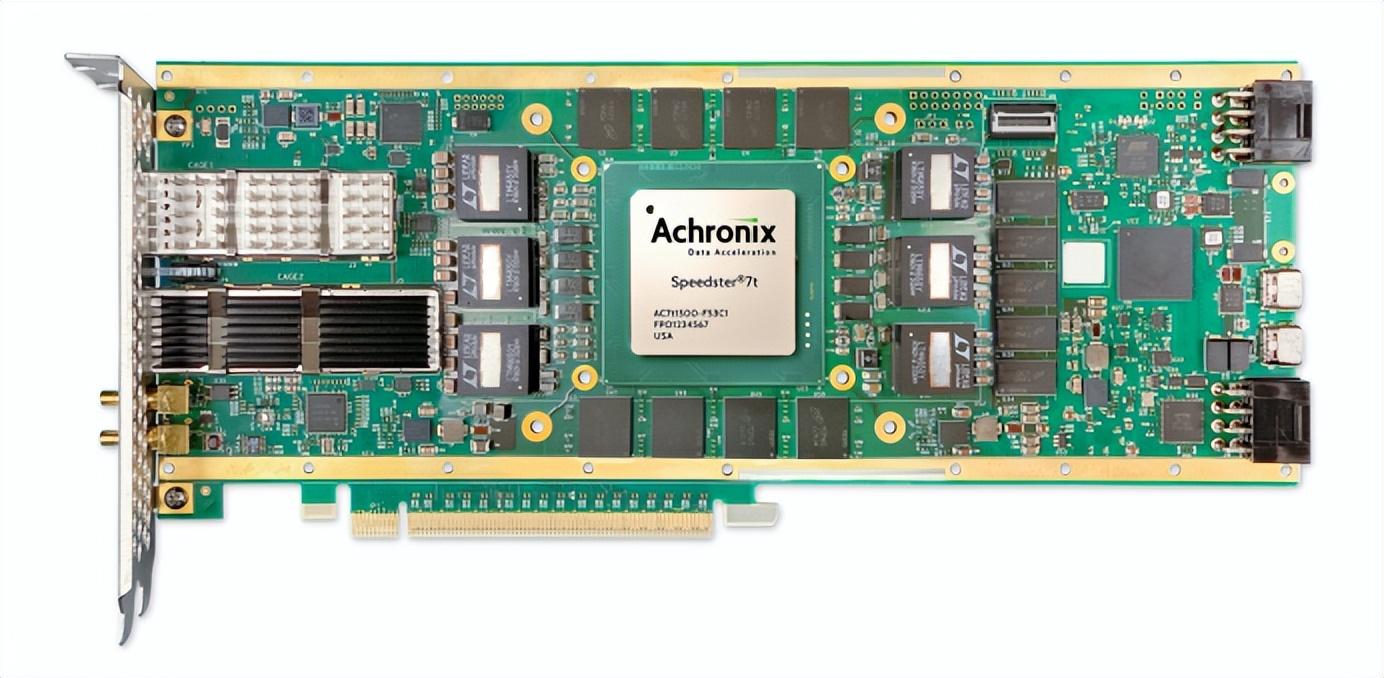

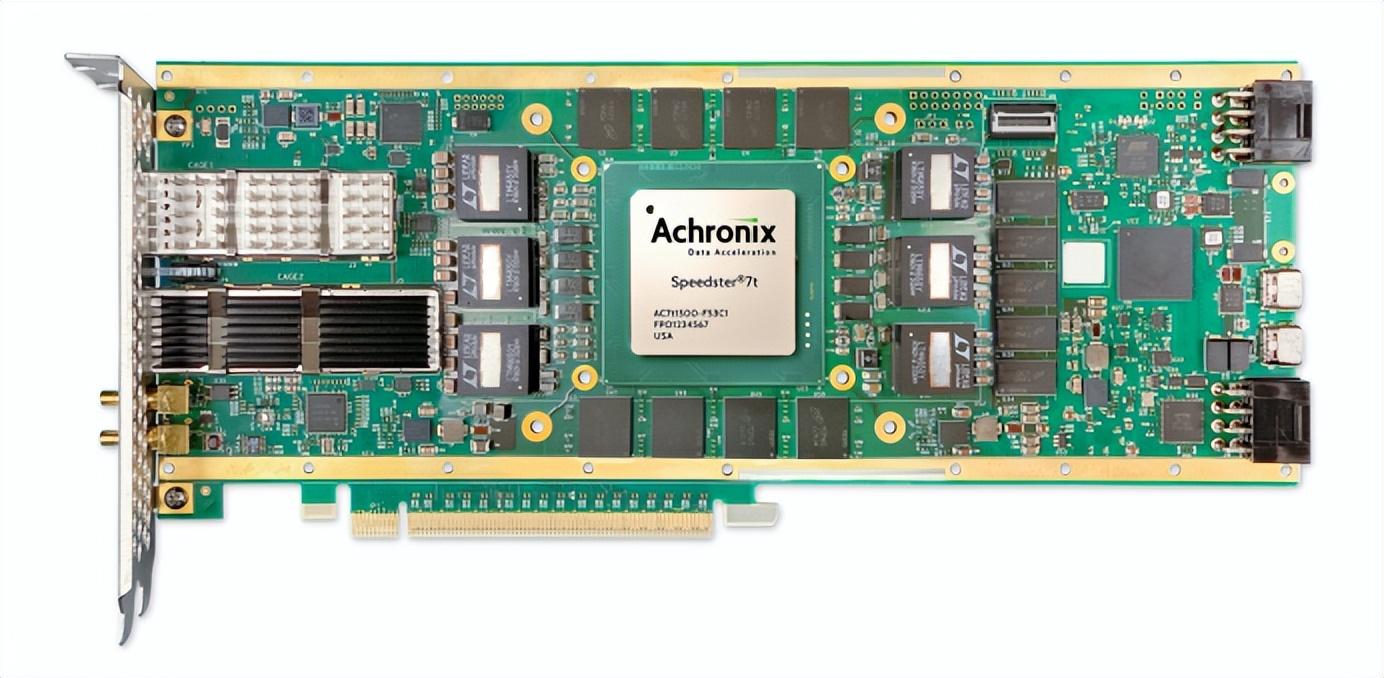

Achronix的Speedster7t支持PCIe Gen5和112G Serdes,而AMD的高端系列Virtex Ultrascale+也仅仅支持到PCIe Gen4,也只在最高端的FPGA中支持到58Gb的GTM,大多数Virtex Ultrascale+仅仅支持32.75Gb的GTY。

2024-03-18 10:55:34 34

34

TINYFPGA AX2

2024-03-14 22:18:36

全球领先的高性能现场可编程门阵列(FPGA)和嵌入式FPGA(eFPGA)半导体知识产权(IP)提供商Achronix Semiconductor公司宣布,该公司将参加由私募股权和风

2024-03-01 10:38:44 585

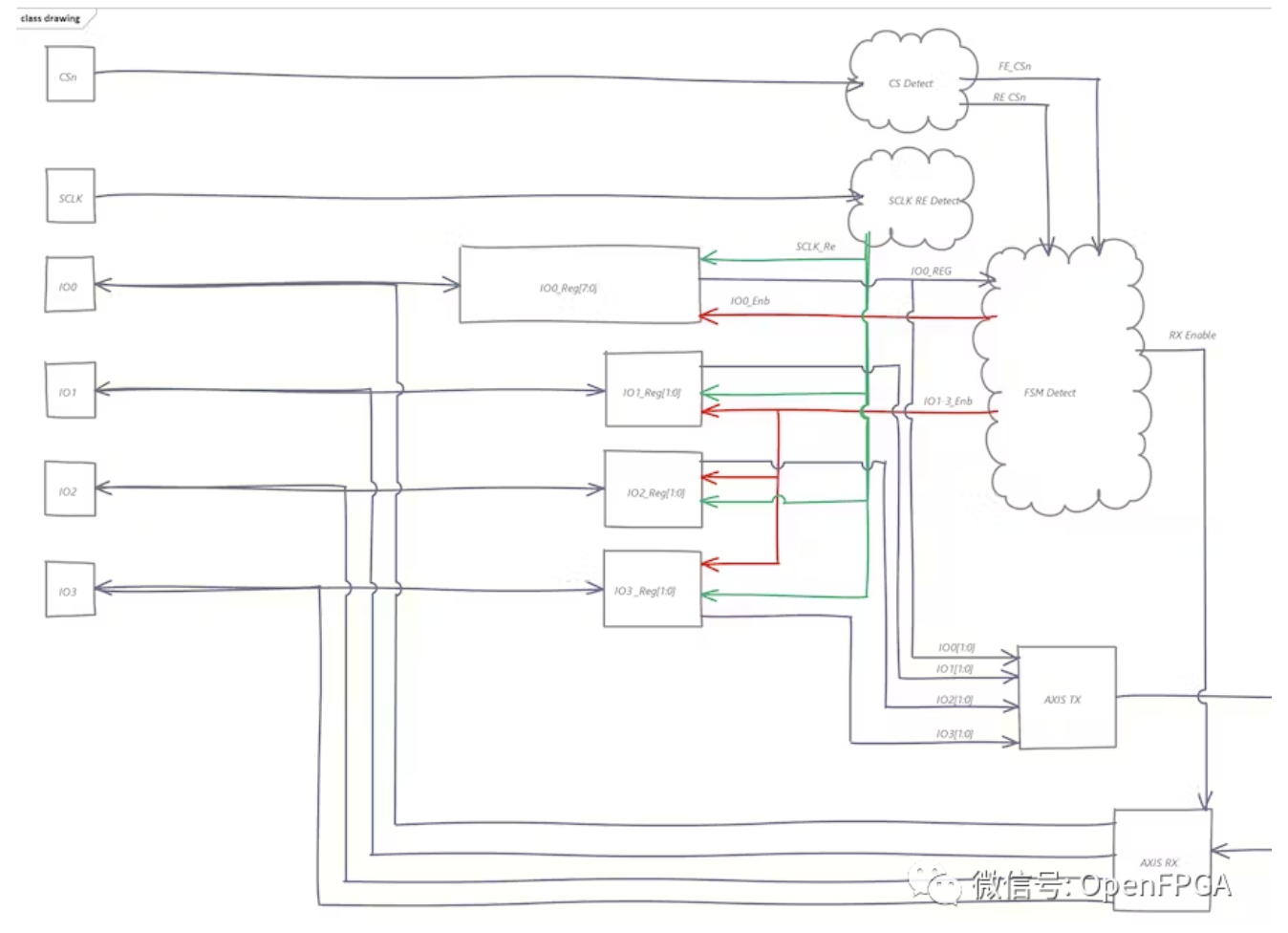

585 端口例化 问题:如图上图所示,计算出图像数据需要的时钟为147M而IP核设置的为70M时钟,计算出数据速率也与IP核配置的不一样,为什么?产品实际的图像显示好像还好。所以实际的视频1数据输出所算出的速率与时钟频率与lvds_rx输入的关系速率与时钟频率是?

2024-02-26 09:35:47

目前项目需要实现正交解码功能,但是GPT12用于正交解码的引脚都没有连接,所以只能是另辟蹊径。目前看TC377的用户手册中的TIM模块是可以(28.13.1.3 )External capture

2024-02-04 06:03:31

#2024,为FPGA生态加油,为FPGA社区点赞#...使用IP核时如何进行modelsim仿真

2024-02-02 20:22:37

长期以来,Achronix为不同行业的数据密集型和高带宽应用提供了创新性的FPGA产品和技术,并帮助客户不断打破性能极限。

2023-12-26 18:14:38 591

591

最近在使用贵公司的AD9826芯片,用FPGA进行驱动,目前AD端输入模拟直流电压,未来要接光电装换的输入装置。现在用FPGA驱动时,在2-SHA模式下,电平转换侧的值时钟为FF,驱动AD的方法

2023-12-18 06:28:12

目前,我在设计中想使用ZYNQ 7015系列的FPGA,利用JESD204 IP核接收A/D转换器AD9683转换完成后的数据。但是JESD204 IP核的端口很多,我不知道应该如何将AD9683

2023-12-15 07:14:52

本文介绍一个FPGA常用模块:SRIO(Serial RapidIO)。SRIO协议是一种高速串行通信协议,在我参与的项目中主要是用于FPGA和DSP之间的高速通信。有关SRIO协议的详细介绍网上有很多,本文主要简单介绍一下SRIO IP核的使用和本工程的源代码结构。

2023-12-12 09:19:08 855

855

我在使用AD9625芯片时,使用4lane 1Gsps时能正常工作。但是用8lane 2.4Gsps时,FPGA内部的IP核会提示无法锁定,问下各位大神遇到过类似的问题吗?有什么解决措施吗?

2023-12-12 08:16:05

星逻智能CEO王海滨表示:“无人机的未来,关键在自动化;而无人机能否实现自动化,关键在续航和操控。与其花费巨额资金优化电池性能,不如另辟蹊径在充电硬件和调度软件上做文章。”星逻智能的三大主力产品就是地面自动化、飞采自动化和数据自动化。

2023-12-08 09:58:12 180

180

我们需要 XILINX FPGA 给 AD9240 提供 8MHz CLK,AD9240 给 FPGA 提供采样数据和溢出标志,但 FPGA 提供的 CLK 最高 3.3V,请问如何输入给 AD9240 呢?

2023-12-08 06:54:46

Xilinx公司的FPGA中有着很多的有用且对整个工程很有益处的IP核,比如数学类的IP核,数字信号处理使用的IP核,以及存储类的IP核,本篇文章主要介绍BRAM IP核的使用。 BRAM是FPGA

2023-12-05 15:05:02 317

317 IP5316 2.4A 充电、2.4 A 放电、集成 DCP 功能移动电源 SOC

简介:

IP5316 是一款集成升压转换器、锂电池充电管理、电池电量指示的多功能电源管理 SOC,为移动电源提供

2023-12-05 09:28:42

的AD9162-FMX-EBZ板子,看到的现象是SYSREF信号一直为高,CGS测试信号不完全拉高,每次重新配置时拉高的lane通道数还不一样。其界面设置如下图所示。FPGA的使用是条用的xilinx的JESD204 IP核。

FPGA抓到的SYNC信号与SYSREF信号如下图所示:

2023-12-05 08:23:30

请问AD9625的寄存器需要如何设置才能打开时间戳的功能?

按照数据手册我将寄存器0x072设置为0x8B,将0x08A设置为0x22.数据经过Xilinx FPGA的JESD204B IP核,但

2023-12-05 07:33:36

的情况时,总会遇到一些以前未曾接触过的新内容,这些新内容会让我们感到陌生和恐惧,不知道该如何下手。

那么今天以xilinx vivado 为例分享学习FPGA 新IP核的正确打开方式。

一、常规

2023-11-17 11:09:22

为你的FPGA设计加加速,NIC、Router、Switch任意实现

优秀的IC/FPGA开源项目(二)-NetFPGA

《优秀的IC/FPGA开源项目》是新开的系列,旨在介绍单一项目,会比《优秀

2023-11-01 16:27:44

开发和验证 FPGA IP 不仅仅是编写 HDL,而是需要更多的思考。让我们来看看如何做吧!

2023-10-17 09:57:19 529

529

开发和验证 FPGA IP 不仅仅是编写 HDL,而是需要更多的思考。让我们来看看如何做吧!

2023-10-16 18:24:42 373

373

本文开源一个FPGA高速串行通信项目:Aurora 8b10b光通信。7 Series FPGAs Transceivers Wizard IP是Xilinx官方7系列FPGA的高速串行收发器,本工程主要是围绕该IP核采用Vivado提供的例程创建。

2023-10-01 09:48:00 2599

2599

请教一下,我在HLS里面要将以下程序生成IP核,C Synthesis已经做好了,但是在export RTL的时候一直在运行

int sum_single(int A int B

2023-09-28 06:03:53

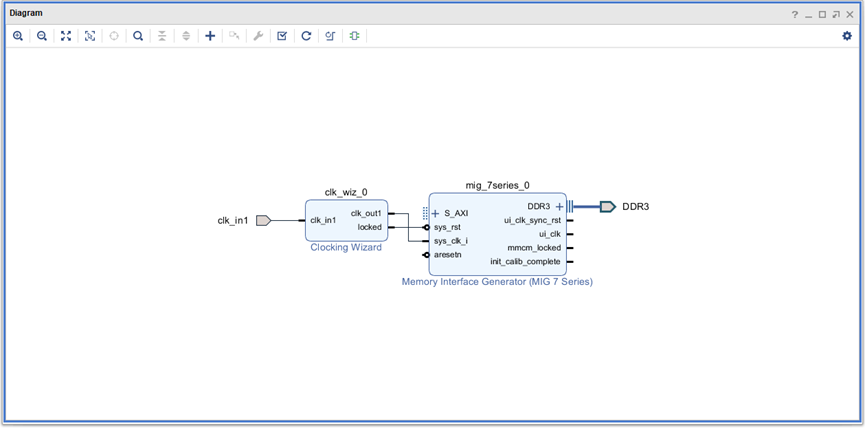

以下主题概述了Altera的外部内存接口解决方案。

Altera提供最快、最高效、延迟最低的内存接口IP核。Altera的外部存储器接口IP设计用于方便地与当今更高速的存储器设备接口。

Altera

2023-09-26 07:38:12

最近出现的 FPGA设计工具和 IP有效减少了计算占用的资源,大大简化了浮点数据通路的实现。而且,与数字信号处理器不同

2023-09-25 14:42:14 374

374

电子发烧友网站提供《UltraScale FPGA收发器向导v1.7 LogiCORE IP产品指南.pdf》资料免费下载

2023-09-15 10:04:16 0

0 电子发烧友网站提供《基于超大规模架构的FPGA存储器IP.pdf》资料免费下载

2023-09-13 17:31:54 0

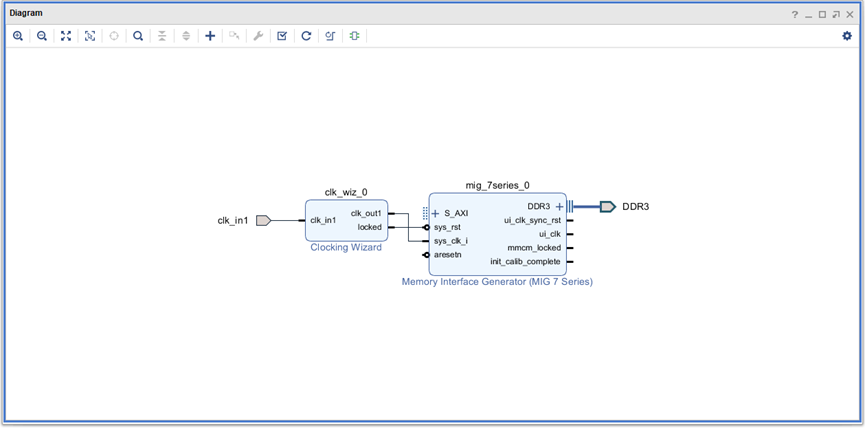

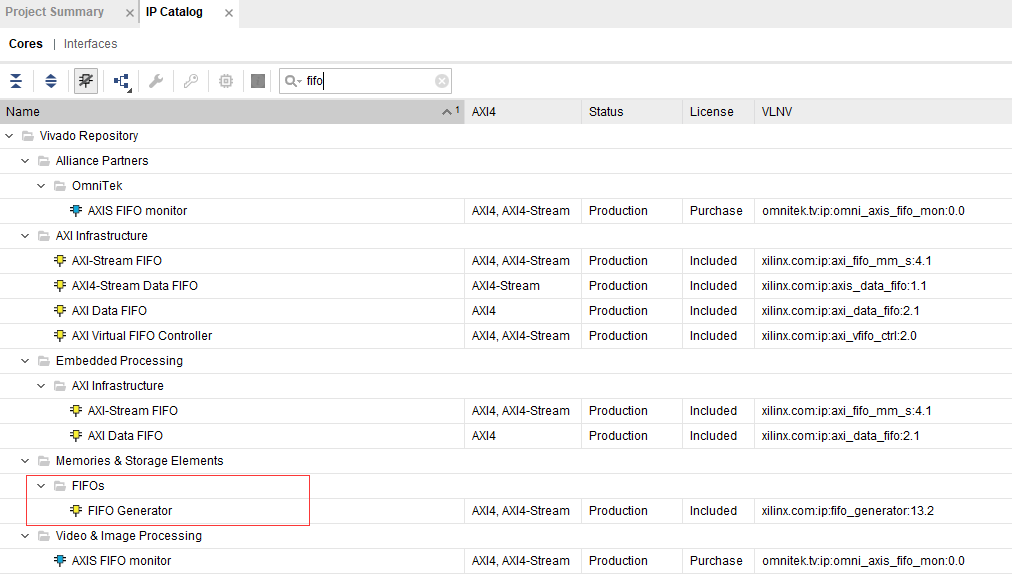

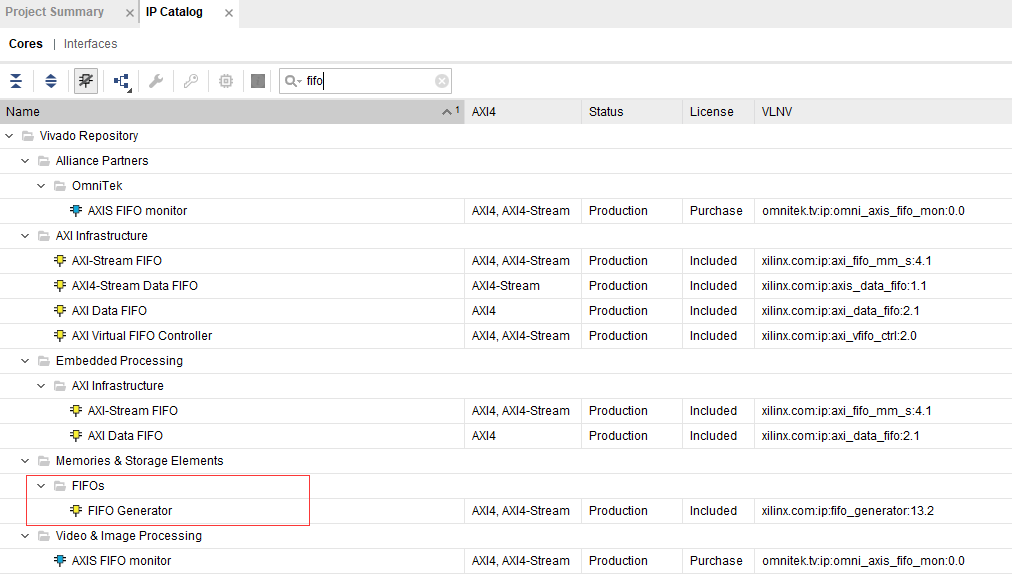

0 上文XILINX FPGA IP之FIFO对XILINX FIFO Generator IP的特性和内部处理流程进行了简要的说明,本文通过实际例子对该IP的使用进行进一步的说明。本例子例化一个读数据位宽是写数据位宽两倍的FIFO,然后使用读时钟频率:写时钟频率=2:3,进行简单的FIFO跨时钟域操作。

2023-09-07 18:31:35 758

758

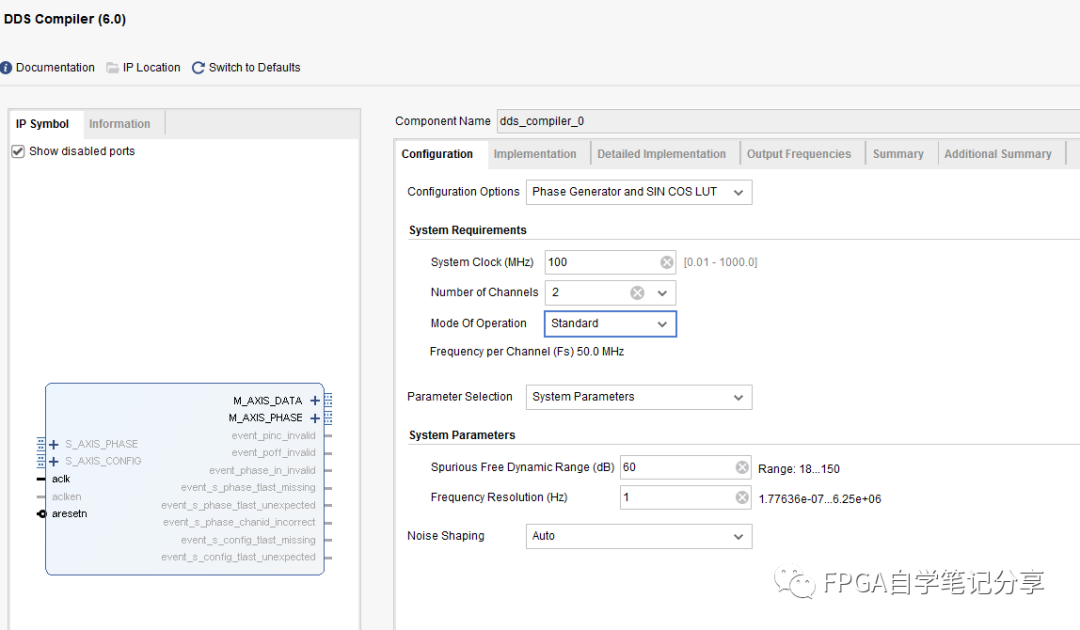

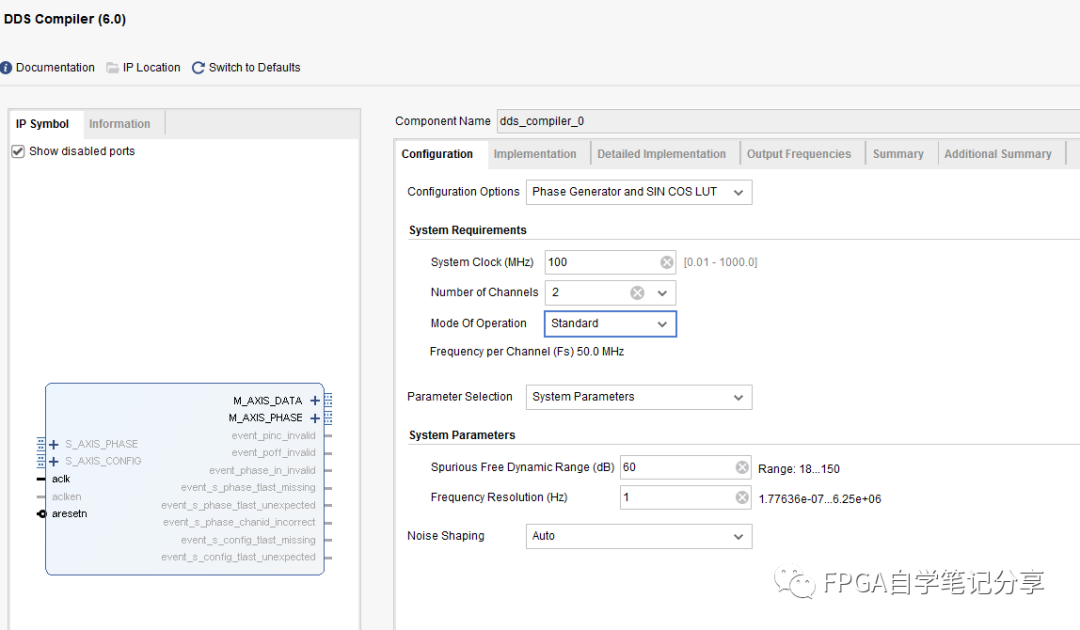

之前的文章对dds ip 的结构、精度、参数、接口进行了详细的说明,本文通过例化仿真对该IP的实际使用进行演示。本文例化固定模式和可配置模式两种模式分别例化ip并仿真,说明该IP的应用。

2023-09-07 18:31:06 769

769

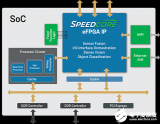

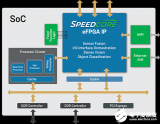

寻求最高集成度的设计人员可以选择去开发一款包含Speedcore eFPGA IP的单芯片ASIC。然而,在某些应用中,单芯片集成无法实现某些产品灵活性,而这在使用基于chiplet的方案中就有更多灵活性。

2023-09-06 15:12:11 234

234

Xilinx的官方PCIE 2.0 IP核或0 IP核,用来实现PCIE 硬核IP的例化;

使用DMA控制器,实现PCIE DMA操作,并将接口转换成方便易用的FIFO接口和RAM接口

2023-09-05 14:39:57

本文介绍一个FPGA 开源项目:Micro Blaze最小系统。MicroBlaze是Xilinx提供的一个软核IP,该软核是由FPGA片内逻辑资源组成,其功能相当于一个CPU。利用Micro Blaze,设计师可以轻松实现一些FPGA难以实现的复杂算法。

2023-09-01 16:16:21 797

797

外部存储器接口( EMIF )通信常用于FPGA和DSP之间的数据传输,即将FPGA作为DSP的外部SRAM、或者协同处理器等。Xilinx提供了AXI-EMC IP核,将其挂载到AXI总线用于

2023-08-31 11:25:41 2348

2348

FPGA开发中使用频率非常高的两个IP就是FIFO和BRAM,上一篇文章中已经详细介绍了Vivado FIFO IP,今天我们来聊一聊BRAM IP。

2023-08-29 16:41:49 2602

2602

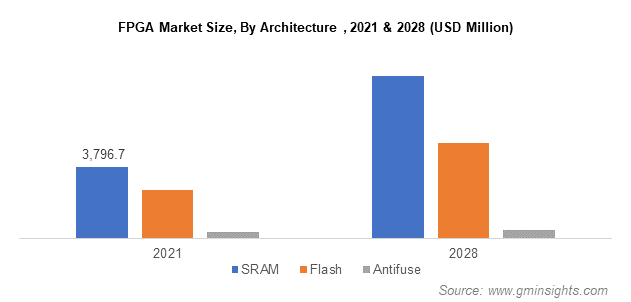

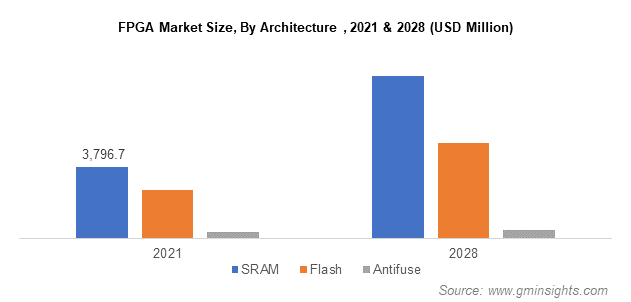

FPGA作为一种逻辑芯片,硬件架构独特,具有并行性、低延时性和灵活性等特性,应用领域广泛。FPGA市场主要玩家是英特尔、AMD、莱迪思、Microchip、Achronix等;国内厂商包括复旦

2023-08-25 16:48:48 952

952

,一旦写入不能再修改或删除,断电不丢失。我们知道FPGA只有RAM,因此事实上在 FPGA 中通过 IP 核生成的 ROM 或 RAM掉电内容都会丢失。用 IP 核生成的 ROM 模块只是提前添加

2023-08-22 15:06:38 1644

1644

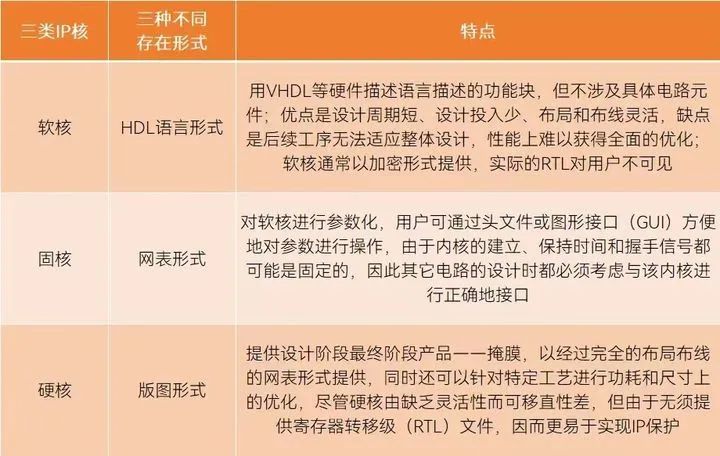

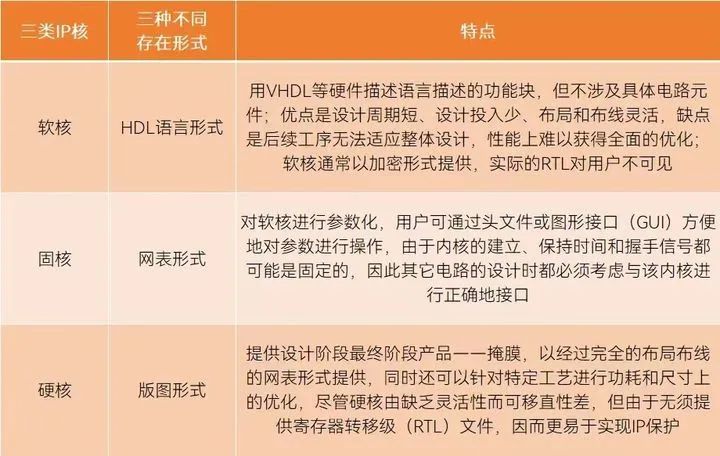

IP(Intellectual Property)是知识产权的意思,半导体行业的IP是“用于ASIC或FPGA中的预先设计好的电路功能模块”。一些常用的复杂的功能模块(如FIFO、RAM、FIR

2023-08-22 15:04:43 1523

1523

所搭的IP软核的通讯协议与总线支持的通讯协议(ICB)不同怎么转换?

2023-08-17 07:05:35

VIVADO 的官方IP核最少分频出4MHz多,而32.768KHz太小了,难道只能自己写分频器吗?

谢谢。

2023-08-12 07:03:06

软核与fpga如何共用一块flash?

目前fpga开发板上只有一个flash,用nuclei 向软核中下载程序掉电就不跑了,请问怎么解决?

2023-08-12 06:05:26

CAN IP 可以应用于汽车控制单元和工业网络等汽车和工业领域,并且 CAN IP 提供多个可配置选项来增加 IP 的灵活性,用户可以使用此 IP 简化设计,快速建立起基于 FPGA 的 CAN 通信系统。

2023-08-09 07:18:34

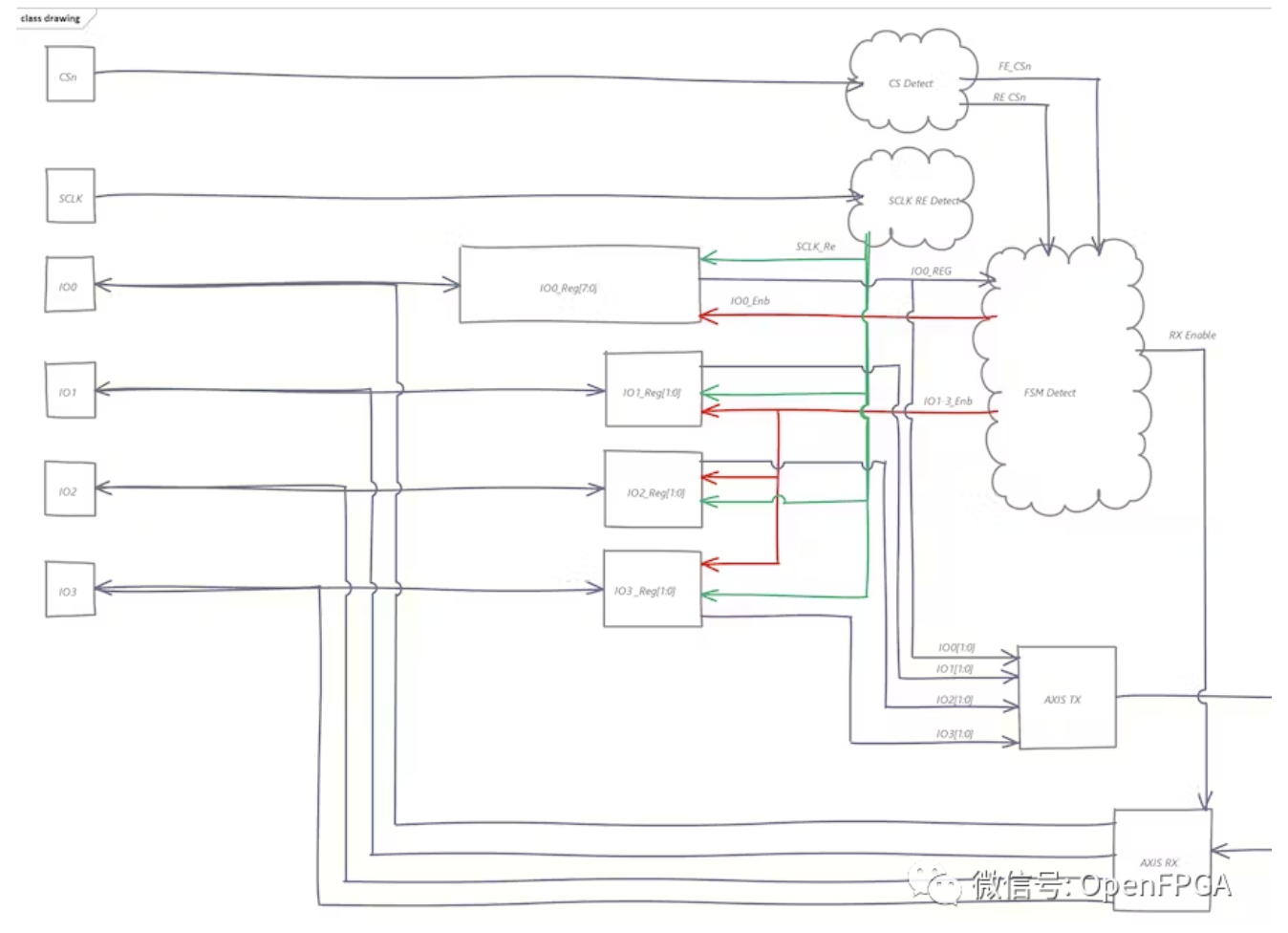

的协议版本。安路的 SPI IP 核具有极高的灵活性,用户可通过配置 SPIIP 核的主/从类型,时钟极性,时钟相位,数据宽度,数据传输顺序,从设备数量以及部分接收阈值等,使 SPI IP 核兼容市场上常见的 SPI 接口。

2023-08-09 06:19:48

FPGA开发过程中,利用各种IP核,可以快速完成功能开发,不需要花费大量时间重复造轮子。

2023-08-07 15:43:19 440

440

以提供可适用于多种工艺的eFPGA IP解决方案的领先提供商,Achronix还给用户提供统一的开发工具,既支持其高端FPGA芯片的开发设计,也支持eFPGA IP的开发设计。Achronix近日再次以其

2023-08-02 17:25:05 538

538

SEM IP是一种比较特殊的IP。它的基本工作就是不停地后台扫描检测FPGA配置RAM中的数据

2023-07-10 16:40:23 420

420 笔者在校的科研任务,需要用FPGA搭建OFDM通信系统,而OFDM的核心即是IFFT和FFT运算,因此本文通过Xilinx FFT IP核的使用总结给大家开个头,详细内容可查看官方文档PG109。

2023-07-10 10:43:18 630

630

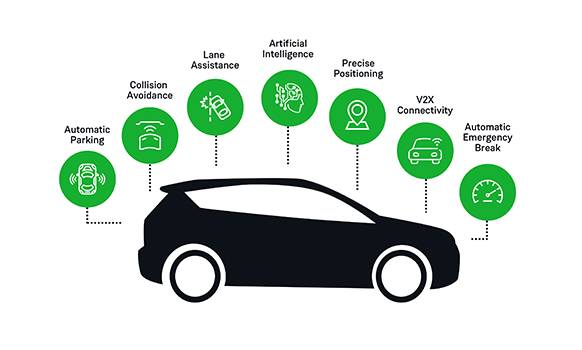

了解eFPGA IP的基础知识,它的优点,以及为什么它将成为未来先进驾驶辅助系统(ADAS)技术的关键要素。

2023-07-10 10:26:38 237

237

FPGA IP核(Intellectual Property core)是指在可编程逻辑器件(Field-Programmable Gate Array,FPGA)中使用的可复用的设计模块或功能片段。它们是预先编写好的硬件设计代码,可以在FPGA芯片上实现特定的功能。

2023-07-03 17:13:28 4086

4086 随着晶体管尺寸不断向原子尺度靠近,摩尔定律正在放缓,面对工艺技术持续微缩所增加的成本及复杂性,市场亟需另辟蹊径以实现低成本前提下的芯片高性能,以TSV(Through Silicon Via,硅通孔)技术为代表的先进封装成为芯片集成的重要途径。

2023-06-30 16:39:34 512

512

随着对高速数据处理的需求呈指数级增长,Achronix始终走在创新的前沿,提供尖端解决方案,以满足网络行业不断演进的需求。通过集成400 GbE速度和PCIe Gen 5.0功能,Achronix

2023-06-29 16:30:13 319

319

1.安装 IP 核

(1)打开工程,点击菜单栏中【tools】 下的【IP Compiler】。

IP Compiler

(2)在弹出的 IP Compiler 界面中,选择【File】下

2023-06-26 10:41:47

一.Xilinx FFT IP介绍

1.总体特性

•FFT IP核支持复数的正逆傅里叶变换,可以实时配置变换的长度

•变换的长度N=2 ^m^ ,m=3-16,即支持的点数范围为8-65536

2023-06-19 18:34:22

说,上货。

ROM使用教程

ROM的英文全称为Read-Only Memory,即只读存储器。可以从任意地址上读取数据,但是不能写入。那么我们ROM中的数据,就需要我们提前存放进去,在IP核中

2023-06-15 16:57:22

上文XILINX FPGA IP之Clocking Wizard详解说到时钟IP的支持动态重配的,本节介绍通过DRP进行MMCM PLL的重新配置。

2023-06-12 18:24:03 5513

5513

锁相环基本上是每一个fpga工程必不可少的模块,之前文档xilinx 7 系列FPGA时钟资源对xilinx fpga的底层时钟资源做过说明,但是对于fpga的应用来说,使用Clocking Wizard IP时十分方便的。

2023-06-12 17:42:03 2883

2883

用vivado2019.2建立工程,工程中调用cordic IP核进行atan求解,功能仿真时正常且满足要求;综合时正常;实现时报错提示多重驱动。

如果经cordic计算后的输出值不用于后续的操作

2023-06-06 17:17:37

S32G2 聚四氟乙烯

S32G2是ip核还是外设?

如果是ip核,是否可以集成到其他SoC中?

谢谢

2023-06-02 08:04:53

的集成电路芯核总称,是经过反复验证过的、具有特定功能的宏模块,与芯片制造工艺无关,可以移植到不同的半导体工艺中。到了SOC阶段,IP核设计已成为ASIC电路设计公司和FPGA提供商的重要任务,也是其实

2023-05-30 20:53:24

FPGA硬核与软核处理器有什么区别和联系?

2023-05-30 20:36:48

RecurrentGPT 则另辟蹊径,是利用大语言模型进行交互式长文本生成的首个成功实践。它利用 ChatGPT 等大语言模型理解自然语言指令的能力,通过自然语言模拟了循环神经网络(RNNs)的循环计算机制。

2023-05-29 14:34:43 571

571

的移动通信组织3GPP(第三代合作伙伴计划,3rdGenerationPartnershipProject)。一、不走寻常路的ITU-RITU-R另辟蹊径,提出了一种

2023-05-29 06:00:00 672

672

A76,为工业控制、汽车、通信等泛工业领域提供CPU IP核;高性能核则基于第三代“香山”(昆明湖)性能提升,对标ARM N2,为数据中心和算力设施等领域提供高性能CPU IP核。

2023-05-28 08:41:37

本文是本系列的第三篇,本文主要介绍FPGA常用运算模块-乘加器,xilinx提供了相关的IP以便于用户进行开发使用。

2023-05-22 16:17:12 888

888

现今的FPGA设计规模越来越庞大,功能越来越复杂,因此FPGA设计的每个部分都从头开始着手是不切实际的。

2023-05-22 14:35:00 1327

1327

Memory Access) IP核开发文档为产品资料“6-开发参考资料\Xilinx官方参考文档\”目录下的《pg020_axi_vdma.pdf》。VDMA IP核寄存器列表如下,其中S2MM_xx将视频

2023-05-03 22:38:12

作者:Pascal Ravillion,Achronix产品营销高级经理 了解 eFPGA IP 的基础知识,它的优点,以及为什么它将成为未来先进驾驶辅助系统( ADAS )技术的关键要素。 提高

2023-04-26 15:20:24 1302

1302

在vivado生成ip核后缺少一大片文件,之前是可以用的,中途卸载过Modelsim,用vivado打开过ISE工程,因为工程中很多IP核不能用所以在重新生成过程中发现了这个问题,还请大神告知是怎么回事?

2023-04-24 23:42:21

日益增长的数据加速需求对硬件平台提出了越来越高的要求,FPGA作为一种可编程可定制化的高性能硬件发挥着越来越重要的作用。近年来,高端FPGA 芯片 采用了越来越多的Hard IP去提升FPGA外围

2023-04-18 11:30:06 299

299 难以在全球化的先进制程中分一杯羹,手机、HPC等需要先进制程的芯片供应受到严重阻碍,亟需另辟蹊径。而先进封装/Chiplet等技术,能够一定程度弥补先进制程的缺失,用面积和堆叠换取算力和性能。

2023-04-15 09:48:56 1949

1949 。设计原理FPGA内部没有FIFO的电路,实现原理为利用FPGA内部的SRAM和可编程逻辑实现。ISE软件中提供了FIFO的ip core,设计者不需要自己设计可编程逻辑和SRAM组成FIFO。设计者

2023-04-11 20:50:21

不多说,上货。IP CORE 之 RAM 设计- ISE 操作工具本篇实现基于叁芯智能科技的SANXIN -B02 FPGA开发板,如有入手开发板,可以登录官方淘宝店购买,还有配套的学习视频

2023-04-10 16:43:04

不多说,上货。IP CORE 之 ROM 设计- ISE 操作工具本篇实现基于叁芯智能科技的SANXIN -B02 FPGA开发板,如有入手开发板,可以登录官方淘宝店购买,还有配套的学习视频

2023-04-07 20:09:59

将此信号输出到外部扩展针即可。架构设计和信号说明此模块命名为pll_test。本设计共有两个模块构成:一个反相器和一个PLL模块(my_pll)。pll_my设计实现本模块为FPGA内部ip 模块

2023-04-06 16:04:21

Opencores是一个开源的数字电路设计社区,它提供了免费的开源IP(知识产权)核心,让工程师和爱好者们可以使用这些IP核心来构建自己的数字电路设计。Opencores的IP核心包括处理器、总线接口、视频、音频和其他数字电路组件

2023-04-03 10:39:53 1194

1194

电子发烧友App

电子发烧友App

评论