电器设备在关断或没有运行主要功能时,其耗电量被称为待机功耗。一个设备一整年下来的耗电量可达约8600Wh,若待机功耗能减小1W,就相当于1美元/年的能源成本。尽管待机功耗看似微不足道,但如果考虑到家庭里所有电子设备的累积效应,这个数目就很可观了。美国家庭在这方面的能源成本每年就高达30亿美元左右,占美国住宅总用电量的近7%。

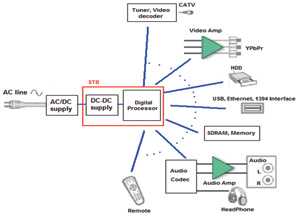

例如,从图1所示的典型机顶盒(STB),我们可以看到整个系统里有许多子电路。其中,AC/DC适配器采用AC电力线输入,然后输出一个DC电压,为红色框里的STB供电。STB还包含了一个DC/DC 功率部件,可把AC/DC电源输出的DC电压转换为众多更低的电压,供数字处理器和不同外设的连接所用。

图1 机顶盒(STB)的典型模块示意图

机顶盒系统

机顶盒系统包含有大量不同的子电路,其中每一个都可在待机模式下被关断,以降低总功耗。为了通过“能源之星”的认证,AC/DC适配器必须满足最低满载效率要求,而且空载功耗小于500mW。

STB要通过“能源之星”认证,必须确保睡眠模式下的功耗小于1W。

所有目标就是通过以下措施提高有功模式下的效率,降低待机功耗的。

1 关注架构级的改进,判断系统何时处于低功耗状态,采取措施提高效率。

2 提高元器件性能以优化最低功耗。

下面我们将从AC/DC部分开始分析,接下来是DC/DC和数字处理器部分。表1是一个采用普通输入,输出电压为32V,总输出功率为20W的典型反激式设计的损耗计算。该表表明,我们必须把关注焦点放在降低损耗上。

变压器损耗

从表1可看出,人们很容易忽略掉变压器损耗,而把注意力集中在缓冲电路、二极管以及MOSFET的损耗上。虽然所有这些损耗都非常重要,但缓冲电路损耗是由变压器的初级和次级绕组之间的松耦合(loose coupling)引起的,要降低缓冲电路损耗,实际上应该从变压器设计着手。通过优化绕组层的排列,可在初级和次级端之间形成更紧密的耦合,而且有效减少缓冲电路的能量泄漏,从而使互耦合 (mutual coupling)得以改进。

磁性元件是总电源损耗的主要原因,对于频率很低的满负载模式和PFM模式,采用损耗较低的材料,加之正确的绕组排列,可以同时降低磁芯损耗和AC损耗,最终提高电源效率。

在任何AC/DC反激式适配器设计中,由于加载的VIN很大,为了降低开关损耗,设计人员不得不采用较低的工作频率,这就给变压器带来了高压使用的问题。因此初级线圈需要很大的匝数,以使磁通量密度保持在其饱和点以下的某个合理水平。在空载条件下,另一个造成大量功耗的额外损耗是变压器的磁化电流。除了流入初级端的电流之外,不论连接负载与否,还有一个磁化电流或励磁电流(Imag)流入初级端,造成轻载或空载条件下的铜损耗。

图2 变压器泄漏和绕组模式

MOSFET损耗及封装

一般而言,性能更高的转换器设计可以推动MOSFET硅芯片及封装技术,实现尺寸更小、效率更高的产品。

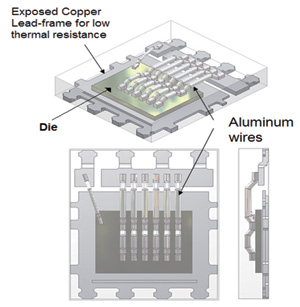

图3 Power 33&56封装

低导通阻抗Rds(on)是实现满载条件下MOSFET传导损耗最小化的一个关键因素。由于封装键合引线与管脚的阻抗占据总阻抗的相当大部分,尤其是在Power56与Power33这样的新MOSFET设计中尤其明显,故需要特别关注使封装阻抗最小化。

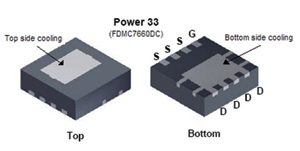

相比其他类型的封装,采用Power 56/33这样带裸露铜引线框架技术和铝圆线互连的增强型封装,可以在占位面积更小的封装内获得出色的热性能和最佳的电气性能。比如,硅晶技术和封装技术两方面的进步(如双面冷却Power33封装),催生了出色的热性能,在电流高达20A的情况下,导通阻抗极低,仅仅为不到2mΩ,而尺寸仅3.3mm×3.3mm。

图4 先进的双面冷却power33封装

还有一点非常重要,就是不仅要考虑在满载条件下以更低的Rds(on)来获得更高的效率,还需考虑轻载条件下Rds(on)×QG(TOT)或品质因数(FOM)。

轻载条件下,Rds(on)没有那么重要,大部分损耗是由栅极驱动损耗造成,其为栅极电压平方的函数。

优化MOSFET的栅极电压也十分重要,因为若栅极电压增加,MOSFET的导通阻抗就会下降。不过,当栅极电压增加时,所需的栅极电荷Qg也随之增加。栅极驱动功率P=Qg·V·F,这里,Qg为栅极电荷,V为栅极电压,F是频率。

输出二极管损耗

2A/500mV标准肖特基二极管的传导损耗大约为1W。若正向电压降(VF)减小200mV为300mV,损耗可降至600mW,即功耗减小约400mW。对于电流较大的低压应用来说,用Rds(on)为10mΩ的同步MOSFET来代替肖特基二极管也是一种可选方案。

工作频率控制

另外还有一些能够减小控制器开关频率的技术,可用来降低待机模式下的功率半导体开关损耗。

其中一种技术是通过降低电源的频率来减小开关损耗,从而提高低功率工作模式下的效率。

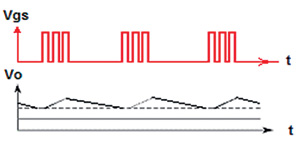

图5 脉冲频率调制

开关模式电源有两种工作模式:脉宽调制(PWM)模式和脉冲频率调制(PFM)模式。在PWM模式下,开关频率是固定的。通过改变电源的占空比来控制输出电压。

在PFM模式下,通过随线路和负载条件的变化而改变开关频率来控制输出电压。这时,开关频率与输出功率成比例。在输出功率很低时,开关频率降低,开关损耗减小,效率提高。PFM控制器的静态电流消耗只限于其基准电压和误差比较器的偏置所需的电流。不过,PWM控制器始终带有一个有源振荡器,即使在空载时,它也会持续从输入源汲取电流。

许多PWM电源控制器都关断大部分或部分PWM功能性,以求降低极轻载或空载条件下的损耗。在这种方案中,突发模式前后还有几个相关的延时周期,会带来可听噪声问题。

图6 迟滞控制

当电源重新开启,并从轻载向满载变化时,这种延时还会造成输出电压下降,迫使电源设计人员不得不使用额外的并联输出电容,从而增加系统的成本和尺寸。

先进突发模式可把轻载条件下的开关损耗降至最小,缺点是会增加DC输出纹波,延长控制周期。

启动电阻损耗

高压半导体IC工艺的进步让电源IC可以直接从AC整流高电压启动,不再像以往那样需要启动电阻来把高电压降压到低电压,从而避免了这部分功耗。

图7中,高压内部电流源(Ics)为内部偏置电路供电,为Cvcc电容充电。而且,当Vcc达到阈值时,内部电流源被禁用,PWM的偏置电流来自于调节辅助绕组(Auxwndg)。本系统中,低静态电流是关键的设计考虑因素。

图7 通过Rbias或利用HV IC实现Vcc偏置

DC/DC功率部件

前面我们讨论了运用于DC/DC的 PWM、PFM和突发模式,本节将着重讨论设计和元件优化。

对于MOSFET,除了通常的传导损耗和开关损耗之外,还有一些可能被忽略的其他损耗。下面我们将讨论其中部分损耗,以及提高满载和轻载效率的方法。

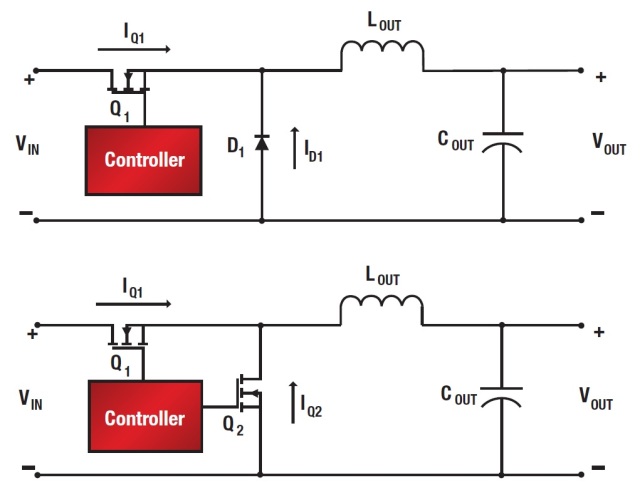

高边和低边同步MOSFET不同的电气特性要求

当同步降压转换器的占空比在50%左右时,高边和低边MOSFET可以使用相同器件;但占空比较小时,必须根据不同的条件来分别选择每个MOSFET。

图8 Power 56的示意图与封装

占空比很小时,高边MOSFET需要非常快速地导通和关断,因此应该选择具有极小栅极电荷的MOSFET。

对于低边MOSFET,由于在开关周期内,它的传导时间要长得多,故支持的RMS电流大得多,这时I2R损耗占主要部分,导通阻抗Rds(on)成为更重要的因子。通过为高边MOSFET选择小栅极电荷(Q1)器件,为低边MOSFET选择低导通阻抗(Q2)器件,而不是高低边MOSFET采用相同的器件,可以获得更高的效率。

直通损耗

当MOSFET的漏源电压迅速上升时,感应产生的dv/dt会导致MOSFET导通。对于12V或更高的输入电压,这可能是一个问题。而且随着MOSFET的漏源电压急剧增加,dv/dt感应电压尖峰可能经由Cgd栅漏电容(米勒电容)出现在相应的栅极信号上。

如果dv/dt感应电压尖峰超过了给定阈值电压,MOSFET就会在本应该关断的时候暂时导通,对总体效率造成不良影响。必须确保所选的控制器使用了“固定死区时间”或“自适应栅极驱动”技术,或者二者兼备。

死区时间损耗

当一个同步整流器关断时,存在一个死区时间,以确保高边MOSFET等待低边MOSFET关断,从而避免交越传导。在死区时间内,低边MOSFET的内部体二极管由于反向恢复速度很慢,故需要一定的时间才能关断,这就在该时间内产生额外的功耗。

利用集成有肖特基二极管、几乎没有反向恢复时间的MOSFET来代替常规体二极管,有助于降低死区时间内的体二极管损耗。

图9 通过提高频率,减少寄生效应来减小系统尺寸

寄生损耗

任何电路都会因元件封装和电路布局而存在寄生电感。由于输出功率等于输入功率减去寄生功耗,故更高的频率有助于减小器件的尺寸,把寄生电容和寄生电感效应降至最小。增加开关频率可减少元件数目,提高集成度,增强对寄生效应的控制,从而减小总体电源系统的尺寸。

多个负载开关

在子电路进入待机模式时,负载开关可以利用使能管脚或通过I2C控制来关断其电源。减小待机电流的一种解决方案是关断系统中未使用的子电路或功能模块。系统中的电路可划分为许多子电路或功率岛区,其中每一个都整合有一个负载开关。

在待机模式下,维持供电只是为了子电路保持稍后恢复工作状态所必需的信息,图10中的子电路#1就是这种情况。所有其他子电路则关断以节电。

利用这种方法,尽管待机电流仍然大于关断所有子电路的方法,但有可能实现一个可快速恢复的待机状态。

这种方法可能带来一个工程技术挑战,即如何实现各模块启动/关断的正确时序。通过打开或切断与不同功能模块连接的负载开关,可以使系统进入待机模式。一旦GPIO或I2C发出命令,低功耗DSP就退出待机模式,解码接收到的信号,通过负载开关启动整个系统。

图10 负载开关关断子电路

数字处理器

处理器芯片的关键在于使用低功耗技术,在待机期间减小内部工作电压,把板上振荡器频率降至低速,并优化电路,降低功耗。对于任何处于有功或待机模式下的逻辑模块,半导体行业都提供有一些相应的解决方案,可帮助降低这些损耗。

时钟门控是一项可用于降低系统有功功耗的技术。它只在有未决任务时启动特定逻辑模块的时钟。若没有未决任务,特定逻辑模块的时钟可被关断,故只减小该模块的有功功率。

还有一种更好的时钟门控解决方案,即切断未在使用的那些逻辑模块的供电。由于有功功率同时与电源电压和频率有关(V2),我们可以动态控制电源电压,或根据计算任务的强度调节处理器的时钟频率,以此来控制有功功率。若性能要求不高,系统可以降低器件的频率和供电电压。

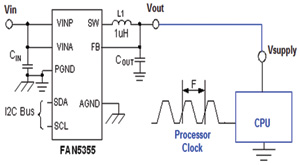

图11 通过I2C控制实现Vout的动态电压调节

结语

关于提高满载条件下的效率,必须改变传统的思考方式,转而着眼于通过降低功耗来提高满载与轻载条件下的效率。

系统工程师必须重点关注架构级和元件级优化的改进,以实现最高效的设计和最低的功耗。特别需要注意的是低磁化电流变压器设计,通过降低轻载下铜损耗来提高效率。

此外,还需要通过顶层系统回顾,以找出给定系统中的所有损耗,然后利用带PFM或突发模式的控制器来降低轻载功耗。最后,划分功率岛区,根据需要利用负载开关来启动/关断子电路,也可以降低待机功耗。

电子发烧友App

电子发烧友App

评论