一、 引 言

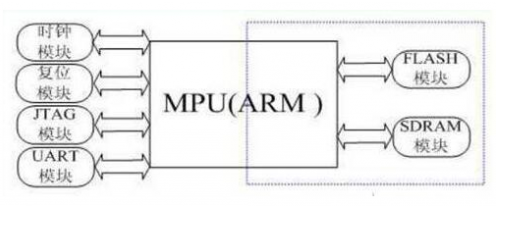

随着近两年各种智能手机、平板电脑、车载电子等各种消 费品的蓬勃发展,ARM体系结构的处理器,作为这些消费品的处理核心,也得到了长足的进步,甚至击败了Intel,在移动嵌入式领域独占鳌头。本文将首先介绍ARM体系结构的发展历程,然后将着重梳理其最先进的Cortex系列处理器的体系结构,以及这些结构对于各种软件平台如JAVA、.NET的支持等。

二、 ARM体系结构的历史即其新进展

2.1 ARM体系结构市场前景

来自英国的ARM(Acorn RISC Machine)公司虽然以ARM处理器著称,但是它独特的商业模式却决定了ARM公司本身并不生产处理器,这点与从研发到生产到出货垂直整合的Intel公司有很大不同,ARM公司采取的是授权与提成的商业模式(Intellectual Property Core 简写IP-Core):公司自己研发处理器体系架构,然后将这套架构的知识产权有偿授权给处理器制造厂商如高通、三星等半导体厂商,这些厂商造出的每一块使用ARM体系结构的芯片只需向ARM公司交付低廉的提成即可。由于这种创新的商业模式和低廉的成本,加上ARM体系的低功耗特点,让ARM体系在对价格敏感和续航能力敏感的32位嵌入式电子消费品市场如虎添翼,基本占据了32位嵌入式消费平100%的市场份额。发展到如今,ARM芯片甚至在对运算速度要求更高的的上网本、平板电脑也大有跟Intel的ATOM处理器一较高低的实力。近来红得发紫的苹果iPad就是采用的ARM深度定制的一款处理器架构,其它还有很多运行着Android系统的平板产品、智能手机产品等也都采用ARM体系结构的处理核心。由此可见ARM体系结构在移动电子消费品市场无与伦比的优势。

2.2 ARM体系发展历史

1985——诞生了第一颗ARM芯片,ARM1 Sample版。

1986——ARM2,具有32位数据总线,26位地址总线,16个32位寄存器的处理器实现产能量产。

20世纪80年代晚期——苹果电脑开始与Acorn合作开发新版的ARM核心。

1991——与苹果的合作造就了ARM6,并进入了苹果的Apple Newton PDA和Acorn Risc-PC成为了它们的处理器。在该年正式成立了ARM公司,作为Acorn的一家子公司。

1991——至今ARM的产品已经横贯应用程序处理器,嵌入式处理器,专家系统等各种计算领域,成为了移动电子消费品市场、复杂工业控制应用的首选处理器体系架构。

2.3 ARM产品系列简介

2.3.1 经典ARM 处理器

这一系列包括的处理器架构有:

l ARM11 系列 —— 基于ARMv6 体系结构的高性能处理器

l ARM9 系列 —— 基于ARMv5 体系结构的常用处理器

l ARM7 系列 —— 面向普通应用的经典处理器

该系列适用于那些希望在新应用中追求稳定的产品。这些处理器提供了许多的特性、卓越的功效和范围广泛的操作能力,适用于成本敏感型解决方案。这些处理器每年都有数十亿的发货量,因此可确保设计者获得最广泛的体系和资源,从而最大限度地减少集成过程中出现的问题并缩短上市时间。

2.3.2 ARM Cortex 嵌入式处理器

这一系列的处理器架构有:

l Cortex-R 系列 —— 面向实时应用的卓越性能

l Cortex-M 系列 —— 面向具有确定性的微控制器应用的成本敏感型解决方案

Cortex-M 系列处理器主要是针对微控制器领域开发的,在该领域中,既需进行快速且具有高确定性的中断管理,又需将门数和可能功耗控制在最低;而Cortex-R 系列处理器的开发则面向深层嵌入式实时应用,对低功耗、良好的中断行为、卓越性能以及与现有平台的高兼容性这些需求进行了平衡考虑。

2.3.3 ARM Cortex 应用程序处理器

这一系列包括的处理器架构只有

l Cortex-A 系列- 开放式操作系统的高性能处理器

Cortex-A在高级工艺节点中可实现高达2GHZ+的主频,也正是由于如此卓越的性能,该处理器架构可用于下一代Internet设备,而且该系列提供单核和多核多种种类,并且提供NEON多媒体处理模块的四种选择和高级浮点执行单元和处理单元。

2.3.4 ARM 专家处理器

这一系列包括的处理器架构只有

l SecurCore - 面向高安全性应用的处理器

l FPGA 内核- 面向FPGA 的处理器

该系列的处理器主要是为了满足一些特定市场的苛刻需求。SecurCore可以用于手机SIM卡和其他识别应用,集成了多种既可以为用户提供卓越性能,又可以检测和避免安全攻击的技术。

2.4 ARM指令集

谈到ARM的指令系统,必须先明确一点的就是,ARM体系结构不同于x86,它是RISC(Reduced Instruction Set Computer)体系结构。所以,在ARM指令体系中,各指令相对来说更加规整、对称、简单。而且指令小于100条,基本寻址方式只有2~3中,而且指令字长都比较一直,并都在单个时钟周期内完成,以便于流水操作。在ARM7中采用的是3级流水线:取值、译码、执行。而ARM9和ARM10则是五级流水线和六级流水线。ARM的访存采用的都是LOAD-STORE结构,这样可以把每条指令的执行时间都平均化,有助于高效的流水线的实现,采用这种结构也就同时意味着指令都要在寄存器间进行操作,所以ARM体系中有大量的寄存器(不少于32个)。

2.4.1 ARM指令与Thumb指令

ARM指令集可以是32位长的ARM指令,也可以是16位长的Thumb指令,这主要是为了兼容数据总线为16位的应用系统。所有的Thumb指令都有对应的ARM指令,Thumb只是ARM的一个真子集,而且Thumb指令舍弃了ARM指令集的一些特性,如大多数Thumb指令都是无条件执行的,而几乎所有的ARM指令都是有条件执行的,又如大多数的Thumb指令由于长度有限,目的寄存器是源寄存器中的一个,这跟x86的汇编指令集相似。

Thumb指令的优点在于它可以在保留32位代码优势的同时,大大节省系统的存储空间,因为在Thumb指令集中的操作数仍然是32位的,指令地址也是32位的,只是指令编码变成了16位,而ARM指令则为32位,所以,相比之下,实现同样的功能,Thumb指令的条数要比ARM略多。图2.1是“Add Rd,#Constant”在Thumb状态和ARM状态下的指 令比较:

由上图我们可以清楚地看到Thumb指令的精简之处,所以Thumb的存储空间仅仅是ARM存储空间的60%~70%,但是Thumb的指令条数比ARM指令条数多30%~50%,如果使用32位的存储器,由于指令条数较少等原因,ARM指令会比Thumb指令快40%左右,而使用16位存储器时,Thumb指令则会快40%~50%。同时与ARM比较Thumb指令的功耗会降低约30%。但是Thumb指令也有其局限性。第一、偏移范围,在Thumb指令中条件转移偏移只有8位,也就是说只能在256Byte的范围内有条件地转移,在无条件转移中可以有16位的偏移,而这些在ARM指令中都是32位,大大提高了灵活性。同时,在Thumb指令中不支持乘法和累加,没有协处理器指令没有信号量指令也没有CPSR指令。

在面临二者的取舍的时候,同其它无数的案例一样,发挥各自的长处是最完美的解法。如果系统对性能要求较高,应采用32位的存储器和ARM指令集,而对功耗和成本要求较高,则应使用Thumb指令集。但是如果两者结合使用,让它们充分发挥各自的优点,则会取得更好的效果。

ARM指令的基本格式如下:

《opcode》 {《cond》} {S} 《Rd》 ,《Rn》{,《operand2》}

其中《》号内的项是必须的,{}号内的项是可选的,opcode为指令助记符;cond是该动作的执行条件;S表示影响CPSR寄存器(程序状态寄存器)的值,如果不加则表示不影响 CPSR的值;Rd表示运算结果的目标寄存器;Rn表示第1个操作数的寄存器;operand2表示第2个操作数,可选。

同时,ARM芯片还支持协处理器,在ARM指令集中有对协处理器的数据操作、数据读取、数据写入和CPU与协处理器的寄存器传送的相应指令。

ARM指令集详细介绍见附录A。

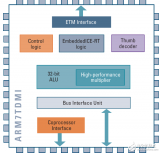

2.5 ARM体系结构对运行平台的支持 ——Jazelle技术

运行Java虚拟机(JVM)解释Java字节码这种方式对大多数嵌入式应用来说占用空间过多,运行速度过慢。而系统发展的趋势及市场的需求决定了Java应用需要有更强的图形处理能力以及一个强大的Java虚拟机。于是催生出了Jazelle技术,从硬件上对Java虚拟机提供支持。 Jazelle DBX(Direct Bytecode eXecution)是一种硬件架构扩展技术,为ARM处理器引入了第三套指令集—Java字节码。新指令集建立了一种新的状态,处理器在此状态下处理Java字节码取指令、译码和维护Java操作数栈等任务。允许它们在某些架构的硬件上加速执行Java字节码,就如其他执行模式般,它能在现存的ARM与Thumb模式之间互相切换。为了降低芯片尺寸并提高性能,Jazelle DBX没有设计成传统形式的微引擎,而是融入流水线中的一个有限状态机。如图2.2所示

Jazelle DBX技术增加了一条新的“Branch-to-Java”指令来进入Java状态。此指令支持条件执行,先检查条件标志,如果条件满足,处理器进入Java状态,跳转到指定目标地址,开始执行Java字节码。在Java状态下,PC寄存器仍是32位寻址Java字节代码。字节码的取指、译码分别在两个流水段完成(对应ARM/Thumb状态下为一个译码流水级)。32位的取指令操作一次性可以取4个Java字节码,性能优势十分明显,对于一个高度优化的商业Java虚拟机,运行评测程序或复杂的MIDP2.0应用,Jazelle DBX技术通常可带来约2~4倍的性能提升。Jazelle DBX技术允许所有的Java指令是“可重新开始”的。这样在执行Java指令过程中,即刻响应中断,从而减少中断延迟,确保实时性能。

在ARM处理器的Java状态下,有若干个ARM寄存器可以功能复用(包括栈指针、栈顶四项(top4 elements of stack)、局部变量0等)。正是这些硬件复用设计,才使得只用了很少的额外逻辑(约一万两千门)就实现了一个Java机。把所有Jazelle DBX扩展所需的状态用ARM寄存器保存,也保证了和现有操作系统、中断处理程序和异常处理代码的兼容性。把栈顶四项保存在ARM寄存器中也能提高Java性能。大量的程序分析显示,大多数程序的栈深度是很小的,所以这项策略可以尽量减少内存访问,硬件也可自动处理栈溢出或下溢。

和Java协处理器或其它专用Java处理器设计不同的是,Jazelle DBX和主处理器共用缓存,这一方面能够降低功耗,而且还可以提高性能。另一个重要的设计考虑是确保Jazelle DBX技术不会影响实时中断性能,仍保持与操作系统中已有ARM异常处理代码的兼容。图2.3是在加入了Jazelle的ARM处理器中运行Java应用的垂直架构架图。

电子发烧友App

电子发烧友App

评论