看见430的JTAG口有保护熔丝,烧断后就不能使用JTAG模块了。那怎么烧断的?

2019-03-13 06:35:19

6748加密板解锁JTAG后,程序烧写步骤可以按不加密的C6748程序烧写进行吗?现在还处在调试阶段,用不到加密功能。第一次用DSP,由于无知,买了了加密板。谁知道这么麻烦。还望前辈指点一下。

2020-05-14 12:01:20

调试,提示Incorrect clock value。按照网上的方法,已经试过下面的方法了:1.JTAG测了,对地和对电源,没有短路;2.FPGA底部焊盘焊接3.烧写器使用的是USB Blaster,用其他烧写器也试过,不通各位大神,给支支招

2015-10-14 16:00:22

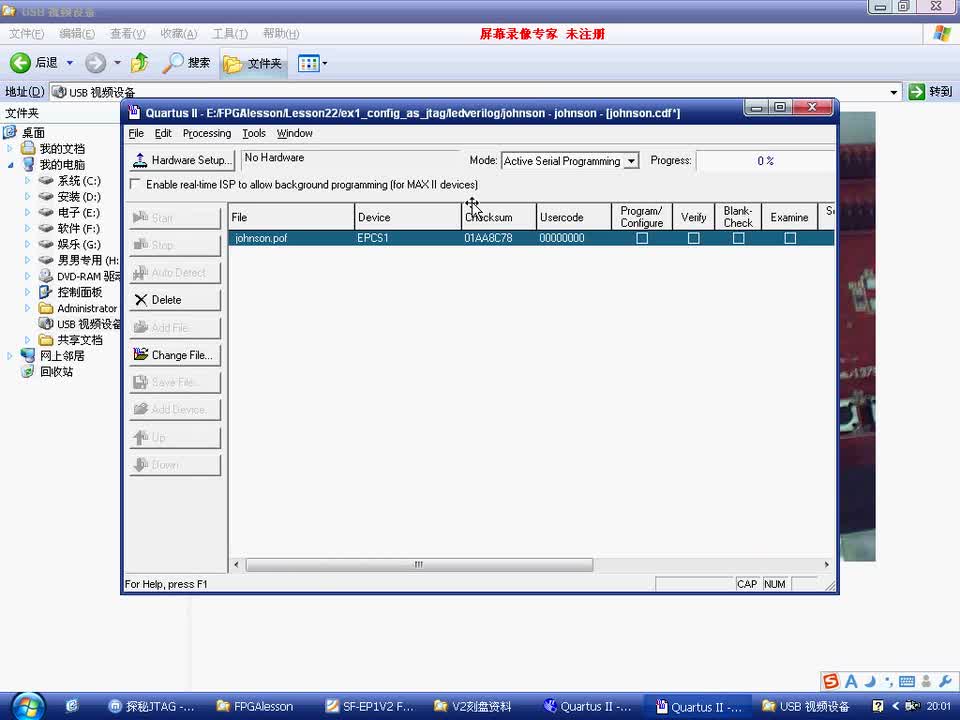

电路板从焊接厂拿回来,将FPGA通过ASP方式下载到主板上。第一次烧写成功后FPGA功能正常,但是后来第二次烧写后FPGA功能不正常,且FPGA控制的版本号显示不正常。但是quartus显示100%下载正常。

2016-09-13 13:28:48

好像FPGA烧写sof文件可以调试。那用什么调试呢?JTAG吗?我原来以为FPGA,CPLD只能烧写,不能调试呢。我以为只可以仿真。请问高手,是这样的吗?谢谢!

2023-05-04 14:48:02

我用的TPS54618给xilinx公司XC5VLX110提供IO3.3的电压,电路图是由webench生成的,发现的问题如下:PCB上电后,测量所有的电压都正常,给FPGA烧写程序成功,断电后发现

2019-03-19 07:34:20

S29GL512N,容量为512 Mb。系统总体框图如图3所示。上位机软件包括Flash烧写工具和串口工具。烧写配置文件时,Flash烧写工具通过JTAG下载线向控制FPGA传输JTAG指令及配置码流,同时串口工具

2019-06-10 05:00:08

今天下载时,下载一直失败,经测量后发现JTAG的TDI引脚与地短路了,请问这能说明是FPGA芯片内部的JTAG接口坏了吗?还是有肯能是别的问题?有谁遇见过没?

2013-04-05 22:49:11

FPGA配置不成功的原因分析近期项目的板卡焊接回来,开始进行硬件调试。在调试FPGA最小电路能否正常工作的时候,出现了这样一个问题:用JTAG烧写器往FPGA中烧写配置文件的时候,文件可以正常烧写

2014-08-21 15:44:32

我设计的是FPGA的板子,用JTAG烧写。直接烧FPGA是没有问题的,但是烧ROM就会出错,IDCODE=ff检验不通过。网上有人说是JTAG的电平不够。求问是不是布线的时候JTAG口距离FPGA一定要近一些,线短一些才行?

2013-07-26 15:29:20

自己用jtag时或多或少都会出现故障,最多的估计就是无法识别。。而且灯也不亮了,这时候就得重新烧写固件了,和大家分享一下,祝大家学习工作顺利由于jtag-v8.bin好像上传不了,需要的可以联系我JLINK V8固件烧录指导.doc (899.5 KB )jlink-v8.bin (64 KB )

2020-06-17 04:35:36

AS口,可以正常烧写程序,但上电程序没运行,conf_done位低电平,接了10上拉电阻也没用,估计没正常复位,到底什么原因了,焊了两块板也是一样的问题现在情况是:JTAG能烧写,程序运行不正常

2012-08-03 11:04:19

本帖最后由 致良知丶 于 2020-11-25 14:41 编辑

各位大佬,我自己做的一个板子用的是ep4ce15m8i7芯片,在使用JTAG烧写的时候提示Error (209014

2020-11-25 08:44:31

jtag接口或者SWD接口的单片机如何通过网口烧写程序?

2023-11-08 06:55:00

各位专家,求指点,我们有一个比较成熟的28027的板子了,已经生产一段时间了,一直很正常,但是这一批的板子有一半不能烧写。经过检查,芯片确认没有问题。jtag接口没有问题,3.3V的电源没有问题,麻烦指点一下,有什么地方出现问题会影响到烧写?

2020-05-08 06:10:35

各位工程师好!我编写了一个基于SYS/BIOS的程序,JTAG调试没有问题。使用C6748_NandWrite.out烧写NAND Flash显示成功,但是重启开发板后程序没有成功运行,拨码开关

2019-07-31 14:13:16

由于程序有BUG导致用JTAG烧写程序后,再无法烧写,DEBUG模式也无法进入?怎么办?

KEIL信息如下:

VTarget = 3.228V

Info: TotalIRLen = 4

2024-01-12 06:07:07

TI对于烧写芯片一般是这样建议的:◆小于1000:用JTAG烧写或者通过串口烧写。M3,C2000没有类似于MSP430 GANG430这种工具。可能会有一些大型的烧写器,这里可以问问System

2020-06-16 12:42:23

最近在在调试CycloneV的板子,JTAG连接不上,程序无法烧写,AS模式在quartus ii 下可以完成程序下载,可是烧写之后,没有任何预期现象,完全不受控,原理图设计完全按照手册来的,电压,时钟,一切正常,希望各位大神给一些建议,谢谢了!原理图截图在附件中

2019-03-11 00:55:10

最近在做一个FPGA和DSP联合控制的一个项目,我主要负责DSP部分的调试,但是,焊接上DSP和它的最小系统之后,创建工程,发现生成的.out能正常的下载到DSP内,但是改为Flash烧写后,就是

2013-09-27 16:23:06

之前在论坛里发布了烧写的问题,专家给予的建议我一一试过但是问题没有解决:

在烧写完成时仍然报此警告:

warning: this program contains initialized RAM

2018-05-14 04:11:09

F280I第一次上电时,目标板连接正常,但在执行烧写程序是一直处于卡死状态,程序没有烧写成功,但JTAG各口电压及DSP各电源正常,这时断开连接再次上电,烧写程序界面一直处于UNCLOK状态,此后一直处于此状态,求解

2020-06-17 15:50:25

第一次经验卡位在晶振:因为在线的JTAG调试有电源与CLK,所以online是正常的,烧写flash之后,却不能成功,没有运行的迹象,because晶振虚焊或者接触不良,JTAG可以帮助起振

2015-08-19 21:57:27

hi,你好:

我最近使用TMS320C6418,现在硬件和软件都已经完成了,想把程序烧写到flash里面。

我研究了用仿真器通过JTAG烧写,弄了几天了,没什么进展,请你们帮忙提供个烧写的方法,

最好能有个烧写的步骤,不胜感激。

谢谢

2018-06-24 05:57:26

本帖最后由 lee_st 于 2017-10-31 08:43 编辑

Xilinx_FPGA下载烧写教程(超详细)

2017-10-21 21:00:16

Xilinx_FPGA下载烧写教程(超详细)

2017-09-30 08:57:48

Xilinx_FPGA下载烧写教程(超详细)Step by step 学习下载配置 Xilinx 之 FPGA配合 Mars-EDA 的 Spartan2 核心板,用图文方式向大家详细讲述如何下载配置 Xilinx的 FPGA。

2017-10-31 12:16:03

本帖最后由 gk320830 于 2015-3-7 09:40 编辑

简介:《电子电气工程师必知必会》从实际工作需要出发,对一名现代电子电气工程师在日常工作中最为关键的知识点进行了总结,从简

2013-10-18 18:56:32

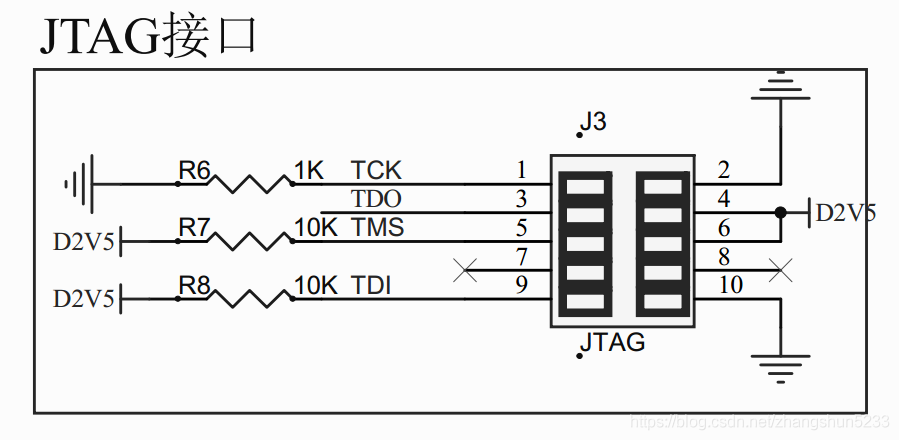

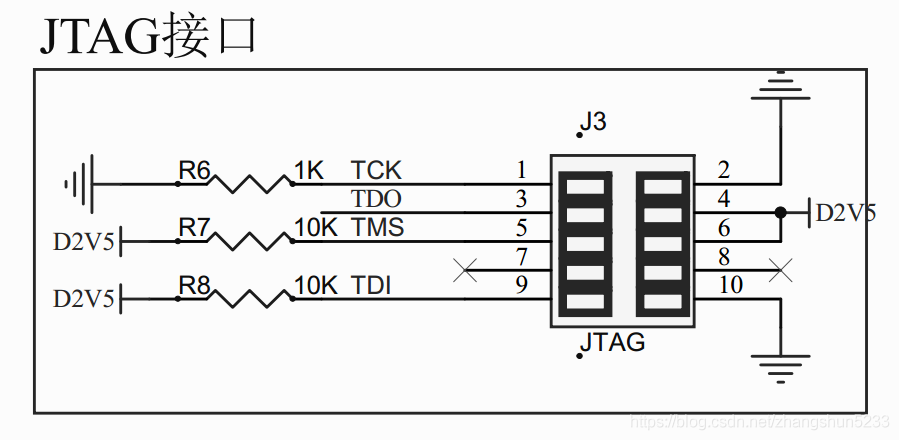

自己画了一个FPGA的板子,FPGA型号为EP4CE22F17Flash型号为M25P64(16引脚)。用Jtag口烧写jic文件总是烧录83%出现错误,哪位大神能指点一下。Jtag原理图如下所示

2018-10-17 11:18:40

各位工程师好!我们参考appro的dm368解决方案量产了一批板子,需要进行烧写。我们使用sd卡进行烧写的时候,发现“nand erase”操作出现大量 “Timeout!FAILED! ”错误

2019-08-26 07:47:44

-> Connect” 到这一步时报错 如下:Opening project file [H:\weidongshan\kaifabanziliao\如何烧写S3C2440裸板程序

2019-04-01 07:45:29

各位专家:

请教一下。我们的硬件平台是参考dvsdk设计的,现在我们打算将ipnc4.1的软件移植上去。我对u-boot进行了修改(主要是将调试串口修改为了串口0)。用串口烧写

2018-05-31 06:29:56

1.JTAG的烧写(开发板为例子)、2.swd的烧写方法

2021-08-05 07:07:05

在用oflash烧写程序时选择了JTAG类型和cpu类型后提示couldn't open giveio.sys我是按照教程将giveio.sys放在C:\Windows\system32\drivers目录下的,是不是因为是win7 64位所以要把giveio.sys放在其他位置呢?求解答,谢谢!

2013-11-30 18:36:20

JTAG烧写就可以对比出来。疑问待解决:1、为何之前项目使用缓存地址0x200 0000可以正常TFTP烧写,而现在只能使用0x8000的缓存地址;2、看项目的uimag也差不多4M字节大小,而项目

2020-03-09 16:13:50

本帖最后由 mr.pengyongche 于 2013-4-30 02:56 编辑

一个windows上的通过JTAG烧写BF531 Flash的程

2013-02-22 16:48:17

1. 现有一块xc7vx690tffg芯片。2. 之前写的fpga程序都是通过在vivado上JTAG线的方式,将mcs文件烧写到flash中,现听说部分加载fpga程序,可以直接更改上位机程序里的bin文件方式就可部分加载fpga程序,更为方便快捷,还请问部分加载技术该如何实现。

2021-03-01 10:45:28

将两片CPLD的jtag口级联 是否可以实现一个jtag烧写两片芯片

2017-03-31 17:31:54

在ARM+FPGA的架构中,想通过串口烧写FPGA程序,硬件如何实现,各位大神请帮帮忙。

2018-05-15 22:33:16

复位按键,就实现了下载成功,但也只成功过这一次

另外通过debug,在烧写FPGA程序时候,观察一下信号,inspect_pc一直处于0和2,然后nuclei studio下载后指令变化

2023-08-11 13:21:18

小弟自己画了块板子,单片机用的是STM32F103RBT6,用JTAG烧写程序的时候出现了下面的错误提示:Could not power up debug port: Control/Status

2019-08-16 02:15:52

文章目录STM32hardware setupDegub protoptype (JTAG / SWD)仿真器烧写DebugCustom

2021-08-10 06:29:46

使用的开发板是MCU200T,原本使用bitstream烧录FPGA,然后用nuclei studio烧写c应用代码一切正常。

但是后面使用.mcs烧录FPGA后,nuclei studio烧写程序

2023-08-16 08:16:52

目录一、工程配置二、使用USART前必知的两个函数的作用2.1 HAL_UART_Transmit_IT(UART_HandleTypeDef *huart, uint8_t *pData

2022-02-28 11:22:09

只要Jtag烧写口。我看文档里面提到可以使用ccs烧写uboot,只不过详见:DM814x_PSP_Flashing_Tools_Guide这个文档。但是我下载的时候发现,ti的wiki在1月15号被封了,我在网上也没有找到这个文档, 有人知道吗?

2021-04-22 17:29:50

在保证烧写环境良好的情况下(烧写器设备没有任何问题),FPGA供电正常外,烧写失败除了与TCK,TMS,TDO和TDI端口外,还与FPGA的别的引脚有关系吗,比喻说FPGA的时钟,希望知道的能耐心的讲解下,谢谢

2016-06-05 18:51:47

最近在参考韦东山老师的视频做u-boot移植,遇到一个奇怪的问题,困扰很久,不知道怎么解决。是这样的,我用jtag/jlink烧写开发板提供的u-boot到norflash中没有问题,但当我用

2013-06-19 15:27:14

线先通过传输这些指令给CPU执行(擦除ROM、读入数据、烧写ROM、和校验ROM),这样完成对单片机的ROM的烧写。此外,现在普遍使用的JTAG仿真器也是这样,单片机的CPU能执行JTAG的特殊指令

2017-05-05 15:09:50

JTAG/SWD/ISP/SWIM详解单片机的四种烧写方式单片机是一种可编程控制器,搭好硬件电路后,可以利用程序实现很多非常复杂的逻辑功能,与纯硬件电路相比,简化了硬件外围的设计、方便了逻辑

2021-07-01 06:40:47

需求:在无法使用esp32s3的uart的情况下(对串口打印信息无硬性要求),希望通过usb otg/jtag interface物理接口来烧写固件结合datasheet和实际操作,我认为是这样

2023-03-13 09:55:42

所示。上位机软件包括Flash烧写工具和串口工具。烧写配置文件时,Flash烧写工具通过JTAG下载线向控制FPGA传输JTAG指令及配置码流,同时串口工具通过串口向控制FPGA发送配置文件地址,完成

2019-06-06 05:00:38

如何对JTAG进行烧写?swd的烧写方法是什么? 怎样去设计一种SWD的电路呢?

2021-10-21 08:55:51

如何控制FPGA烧写时io口的电平呢?

2023-04-23 14:47:00

嗨专家,我正在使用Spartan3AN(XC3S50AN)FPGA板和平台线USB II。你能告诉我如何通过JTAG监控PC中FPGA I / O的状态吗?谢谢,V。Prakash以上来自于谷歌翻译

2019-06-18 09:05:14

如何通过jtag来烧写da14580的OTP image并且修改l蓝牙设备地址?1、接线连接线VP 6.8V、GND、TMS、TCK。2、烧写HEX2、烧写OTP Header image 以及修改

2022-02-09 06:30:39

嵌入式工程师必知必会

2016-11-22 10:56:48

嵌入式工程师必知必会

2016-04-02 14:40:32

搞开关电源必知知识——X电容和Y电容设计方法

2019-04-05 21:44:09

有没有哪位DX总结过ARM的JTAG、SWD和其它调试与烧写接口的标准电路,我在官方网站上都没有看到,或者是推荐的电路其实如果有这样的电路可以使初学的工程师可以更快的上手,不用花过多的时间在硬件调试上

2022-08-29 14:13:46

烧写JIC的过程实际分为两步第一步,使用JTAG模式烧写一个FLASH Loader固件到FPGA中;第二步,使用该FLASH Loader固件将JTAG传输的FPGA的配置文件写入到EPCS

2020-02-06 20:48:52

麻烦各位帮我看看,程序烧写不进去可能是什么原因,用SWD能下载进去,用JTAG下载去写不进去?

2016-07-10 18:41:46

世界第 3 的滴滴裁员,求职必知独角兽公司排行榜

2020-06-18 07:30:48

电力行业电气工程及其自动化专业 “应聘” 时必知

2012-05-28 22:41:34

电子工程师必知必会

2013-07-04 08:50:15

电子电气工程师必知必会

2015-03-06 17:29:57

`电子电气工程师必知必会_第2版`

2016-06-26 08:26:25

、电路的可靠性设计、仿真、焊接,以及电路和软件的故障处理等等,文字生动幽默。此外,本书还以较大的篇幅,介绍了作者作为研发部门的管理者,在人际沟通、管理等方面的心得体会。图灵 电子电气工程师必知必会 238

2019-09-11 11:40:22

` 本帖最后由 zgzzlt 于 2012-8-16 13:32 编辑

电子电气工程师必知必会 第2版 【美】Darren Ashby 著 尹华杰 译 《电子电气工程师必知必会》从实

2012-08-09 09:33:52

JTAG/SWD/ISP/SWIM详解单片机的四种烧写方式单片机是一种可编程控制器,搭好硬件电路后,可以利用程序实现很多非常复杂的逻辑功能,与纯硬件电路相比,简化了硬件外围的设计、方便了逻辑

2022-01-27 06:57:58

用的LPC1788,使用jtag,但是莫名其妙突然识别成了ARM9.(用的swd模式)但是芯片正常跑动,并没有什么问题。很奇怪的。现在都不能正常烧写、调试的了。

2020-04-26 22:11:42

请问两片2812JTAG级联后用ccs3.3怎么烧写程序?

2018-11-19 14:52:50

器件手册里提到的SEU校验功能,用的是jam文件写入crc故障到crc存储寄存器再读回的方法,但是按照手册上的说法,FPGA下电后数据就清除了,会对之后的烧写造成影响吗?有大神验证过这个功能吗?有没有

2018-06-27 16:11:26

仅留一个Jtag座子即可。 2、AS模式 这个模式很简单,没什么好讲的,记得把模式选择弄好就是了,需要再次提醒的是AS模式中配置芯片可以通过Jtag口将JIC文件直接烧入。 3、AP模式AP模式是我写

2015-01-28 10:27:03

模块在接收到上位机软件发送的指令后,相应的解释如表1所列。表1 JTAG指令解释2 Flash控制器和FPGA器件配置模块设计2.1 Flash控制器设计烧写Flash存储器和利用Flash存储器配置

2019-05-30 05:00:05

本内容向大家提供了JTAG功能及系统设计 JTAG也是一种国际标准测试协议(IEEE 1149.1兼容),主要用于芯片内部测试。现在多数的高级器件都支持JTAG协议,如DSP、FPGA器件等。标准的JTAG接口是

2011-03-30 10:04:32 0

0 Xilinx的JTAG电缆可以通过FPGA“直接”烧写SPI/BPI。很多对xilinx开发环境不熟悉的用户,如果第一次接触这种烧写模式可能会有疑惑,FPGA是如何做到JTAG和Flash之间

2017-02-08 02:40:11 6513

6513

同志们,根据ALTERA官方FAE(现场应用工程师)的强烈建议,请注意不要随意带电插拔你的JTAG下载接口,否则会损坏FPGA芯片的JTAG口信号管脚。

2019-07-31 17:35:00 0

0 本文档的主要内容详细介绍的是FPGA JTAG工具设计的教程说明。

2020-12-31 17:30:55 18

18 赛灵思公司的FPGA芯片具有IEEE 1149.1/1532协议所规定的JTAG接口,只要FPGA上电,不论模式选择管脚M[1:0] 的电平,都可用采用该配置模式。JTAG模式不需要额外的掉电

2020-12-31 17:30:55 13

13 对FPGA进行上板调试时,使用最多的是SignalTap,但SignalTap主要用来抓取信号时序,当需要发送信号到FPGA时,Jtag Master可以发挥很好的作用,可以通过Jtag Master对FPGA进行读写测试

2022-02-16 16:21:36 1900

1900

通过JTAG接口为FPGA下载程序时遇到了速度很慢甚至ISE上配置TCK时钟最小的为250kHz时,依然无法保证下载成功。

2023-06-25 16:06:58 1130

1130

正在加载...

电子发烧友App

电子发烧友App

评论