Altera将在8月16号至10月30号中国区的9个城市举办免费的2012 DSP技术研讨会。通过以下主题学习面向Altera FPGA的专用数字信号处理(DSP)设计方法。了解DSP Builder中基于模型的设计流程以及

2012-08-15 11:48:19 842

842 Altera公司今天在2013年安博会上宣布动视元采用Altera基于FPGA的最新视频分析成功推出首个基于FPGA的智能交通视频分析解决方案,较之传统工控机或DSP的解决方案,基于FPGA的视频分析可极大提高侦测率和节省成本...

2013-10-29 18:13:44 1140

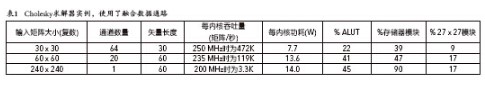

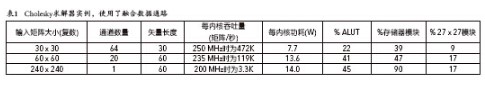

1140 卷积是一种线性运算,其本质是滑动平均思想,广泛应用于图像滤波。而随着人工智能及深度学习的发展,卷积也在神经网络中发挥重要的作用,如卷积神经网络。本参考设计主要介绍如何基于INTEL 硬浮点的DSP

2018-07-23 09:09:45 7321

7321

及浮点性能,从而使用户不仅能整合多个 DSP 以缩小板级空间并降低成本,同时还能减少整体的功耗要求。,充分满足移动网络领域对通道密度及高质量媒体服务日益增长的需求。 2) DSP 部分支持2个

2015-09-17 14:38:59

基于TI DSP TMS320C6678、Altera FPGA的CPCI处理卡1、板卡概述 本板卡由我公司自主研发,基于CPCI架构,符合CPCI2.0标准,采用两片TI DSP

2015-09-11 16:55:46

DSP模块、高性能浮点DSP功能的FPGA,也是目前发售的唯一具有硬核PCI Express (PCIe ) Gen3 x8 IP模块和28-Gbps收发器的FPGA。 Altera公司产品和企业

2012-05-14 12:38:53

DSP算法应用及设计

2013-08-14 16:50:36

DSP算法的验证与模拟一个实际的DSP处理系统必然要使用各种算法,要求DSP系统设计者在选择某种算法前就精通各种算法的细节是不现实的。DSP处理系统所选用的算法无非是各种通用算法的组合和改进。革命性

2011-07-16 14:28:11

DSP自动加载过程及程序烧写的简化设计

2021-04-02 07:26:05

专业浮点DSP,其它场合采用定点DSP就足够了。在实际应用中,采用块浮点方法能有效提高定点DSP的处理精度。5. 成本要求。在军事和航天用途中,为了高性能、高可靠性和留有发展余地,往往尽量采用高性能

2011-07-16 14:27:02

和低成本是其主要的特点。而TMS320C3X/C4X/C67X属于浮点DSP芯片,运算精度高,用C语言编程方便,开发周期短,但同时其价格和功耗也相对较高。 DSP应用系统的运算量是确定选用处理能力为

2016-12-16 19:28:54

DSP重要的不是会编程,而是算法的研究(Matlab/Simulnk仿真就不必多说了),光会编程是没有用处的,也只是个程序员而已,还不如你现在的工作。学FPGA我是从夏宇闻老师编写的《verilog

2012-03-01 13:55:18

项目的需要时这样的:每秒输入dsp 25帧130像素的图像,需要对图像进行增强、线性滤波、直方图处理、图像分割等简单的操作,另外还需要进行一些浮点运算想问问各位大神,主频为300MHZ,运算速度为

2019-01-15 11:25:55

驱动程序,用于与DBM10芯片进行通信。SoC还具有跨平台工具链,该工具链支持所有常用的人工智能(AI)和机器学习(ML)框架,以简化算法部署。工程师可以开发,训练和测试算法;接下来,他们可以将其保存为标准

2021-03-03 10:46:14

最近出现的 FPGA设计工具和 IP有效减少了计算占用的资源,大大简化了浮点数据通路的实现。而且,与数字信号处理器不同, FPGA能够支持浮点和定点混合工作的 DSP数据通路,实现的性能超过

2019-08-13 06:42:48

FPGA设计之浮点DSP算法实现,DSP算法是很多工程师在设计过程中都会遇到的问题,本文将从FPGA设计的角度来讲解浮点DSP算法的实现。FPGA设计之浮点DSP算法实现是赛灵思工程师最新力作,资料不可多得,大家珍惜啊1FPGA设计之浮点DSP算法实现[hide][/hide]

2012-03-01 15:23:56

你好! 按规格书上说,现在的M4内带有DSP。 我在程序的初始化的时候,利用ROM_FPULazyStackingEnable();使能了浮点运算,那么如果我在做些浮点或是整形的运算,或是一些算法的时候,M4 自己会用DSP做运算,还是需要人为干预?还是有库可用? 谢谢。

2018-08-16 07:49:39

解sRIO在复杂系统拓扑中的作用是什么?MSGQ模块包括哪些部分?MSGQ模块是如何简化复杂的DSP设计的?

2021-08-06 07:31:43

TI科学家谈浮点DSP未来发展 自十多年前浮点数字信号处理器(DSP)诞生以来,便为实时信号处理提供了算术上更为先进的备选方案。不过,定点器件至今仍是业界的主流--当然低成本是主要原因。定点DSP每

2009-11-03 15:18:49

ccs软件可以在定点dsp平台开发浮点运算吗

2012-10-07 21:54:47

函数执行时间测试 42.3 FIR滤波函数执行时间测试 42.4 复数FFT函数执行时间测试(单精度浮点) 42.5 复数FFT函数执行时间测试(基2算法Q31) 42.6 复数FFT函数执行时间测试(基2

2015-07-17 11:26:02

第7章DSP定点数和浮点数(重要) 本期教程主要跟大家讲解一下定点数和浮点数的基础知识,了解这些基础知识对于后面学习ARM官方的DSP库大有裨益。特别是初学的一定要理解这些基础知识。 7.1 定点数和浮点数概念 7.2 IEEE浮点数 7.3 定点数运算 7.4 总结

2015-06-03 11:47:44

今天测试一下EdgeBoard的浮点运算能力(在Linux下),测试的程序比较容易,运行基2 FFT算法,折合成 百万次浮点运算/每秒 的运算速度来衡量。 运行程序,结果如下: 下面是各类处理器

2021-04-29 12:12:20

恢复积分校正环节,以便消除系统的稳态误差,保证伺服电机位置控制的精度。3 实验结果DSP+ARM双核控制器硬件电路经过测试可用,并在控制器上实现了相关控制算法,验证了算法的可行性,系统响应速度快,稳态

2021-11-23 07:00:00

日前,Altera发布新系列Cyclone IV FPGA ,延续其收发器技术的领先优势。当前移动视频、语音和数据访问以及高质量3D图像对低成本带宽需求与日俱增,与此同时,终端产品市场,如智能电话等

2019-07-31 06:59:45

,因此第(3)步和第(2)步基本是同一步骤了。而采用Host Instrinsics则可以将第一步也简化,直接调用对应DSP的c函数,在PC上则生成PC的代码,在DSP上则生成DSP的代码。TI提供的c_intrinsics_host_port在PC上模拟C6000的DSP浮点指令,可以自由下载。测试程序的结果均为pass。

2016-12-26 15:07:00

在定点DSP系统中可否实现浮点运算?当然可以,因为DSP都可以用C,只要是可以使用c语言的场合都可以实现浮点运算。

2009-04-07 09:06:17

一.简介上篇博主已经给大家分享了Qualcomm 平台DSP算法集成的架构和算法原理及其实现的功能,今天我们进一步分享Qualcomm 通用平台系列的算法集成的实际案例。图1 DSP简介二.算法集成

2018-09-25 15:41:21

一.Hexagon DSP简介DSP( 数字信号处理器 ):DSP 即数字信号处理器,是手机芯片里一个专门负责处理数字信号运算的微处理器。主要应用在实时快速地实现各种数字信号处理算法。图1

2018-09-25 15:44:10

简化DSP48E1片操作

2021-01-27 07:13:57

)。因此,在尝试PIC32MZ(有点贵的启动器套件加上用于启动器套件扩展板的适配器板)之前,我想优化代码,其中许多操作可以在DSP单元中进行,并且我查看了微芯片DSP和浮点库,但是DSP功能ons被声明

2019-09-16 10:15:23

在定点DSP系统中可否实现浮点运算?

2019-09-25 05:55:21

在定点DSP系统中可否实现浮点运算?

2019-09-26 05:55:42

开发平台:DM8127+ipnc-rdk3.5

现在想建立dsp处理算法,但是ipnc中的demo没有dsp相关的例程,请问如何建立dsp算法link?

2018-05-28 13:45:50

、改进、替换和维护成本来衡量),您会发现Altera FPGA 是分立MCU/DSP/ASSP 产品灵活的竞争方案。引言工业自动化和过程控制生产商一直面临持续的全球竞争和经济压力,商业模式和利润不断受到

2013-11-13 11:17:35

最近在安装DSP Builder11.0+Matlab2011a+Quratus II 11.0安装完成后没有找到Altera DSP Builder Blockset;求大神指教。

2015-06-04 16:01:12

中都能正确的实现,为什么在CCS3.3硬件仿真过程中实现不了?本人用的DSP5509,是定点DSP,但是函数中用到了浮点数,不知道是不是这个原因。但如果是这个原因,为什么在下面的测试函数里可以得到正确

2013-10-03 13:13:47

为什么很多嵌入式算法 都将浮点数转化为无符号整形,再进行运算,有些DSP自带浮点运算库的,但还是这样转换,本人初到,接触了一部分历程,有TI提供的,有大牛自己写的,感觉对IQmath不熟悉,但知道

2017-04-26 20:07:55

最新做高精度的控制算法,需要做比较高阶的数字滤波器,用的是2812,计算浮点数乘法非常的慢,关键是只能计算32位的浮点数乘法,造成数字滤波器的特性都和原来的设计有偏差。大家推荐一款可计算64位浮点数(double)的DSP吧。

2015-12-15 21:04:41

近来,Altera公司推出业界首款浮点FPGA,它集成了硬核IEEE754兼容浮点运算功能,提高了DSP性能、设计人员的效能和逻辑效率。据悉,硬核浮点DSP模块集成在

2019-07-03 07:56:05

你好,

我想在dsp里做一个音频降噪处理的算法,刚查看了一下adau1452的性能是极好的,我想进一步了解一下这款芯片。

请问adau1452支持浮点运算吗?你们提供的例程有没有关于降噪的?我自己写的算法代码是c语言的就可以了吧?

或者说只做降噪处理的(算法有点复杂)有没有什么更好的dsp推荐?

谢谢

2023-11-29 07:58:31

你好,我想在dsp里做一个音频降噪处理的算法,刚查看了一下adau1452的性能是最好的,我想进一步了解一下这款芯片。请问adau1452支持浮点运算吗?你们提供的例程有没有关于降噪的?我自己写的算法代码是c语言的就可以了吧?或者说只做降噪处理的(算法有点复杂)有没有什么更好的dsp推荐?谢谢

2018-09-25 11:23:38

现想将controlsuite里面的28035的工程,移植到自己的28069板子上,请问怎样从定点DSP工程移植到浮点DSP,应该怎样转换,怎样处理定点DSP里的Q value,像下面这样的语句,应该怎么移植呢,谢谢_IQ(0.004)_IQtoIQ15(0.5)

2020-05-08 09:12:32

由于我后面的课题需要涉及较多的浮点运算,只熟悉f103,它不带FPU,所以软件浮点算法就显得很重要了。这几天在做些小研究和测试。今天又仔细研读了谭浩强的C语言书的数据类型章节,上面有说到c编译系统总

2021-08-04 06:17:25

浮点是最优选的数据类型,可确保算法建模和仿真的高精度计算。传统上,当您想要将这种浮点算法部署到FPGA或ASIC硬件时,您唯一的选择是将算法中的每种数据类型转换为定点,以节省硬件资源并加快计算速度

2018-09-11 21:59:16

Altera公司用FPGA做DSP算法的工具

2006-03-25 13:46:45 39

39 DSP算法程序

2006-03-26 14:15:06 85

85

DSP的浮点运算方法

2008-01-16 09:25:05 4

4 定点dsp浮点运算的多媒体视频教程:

2008-01-24 09:14:21 50

50 定点DSP芯片TMS320F2812实现快速算法应用:摘要:论述了以DSP 芯片TMS320F2812 为核心的一种测量仪器的组成原理、设计思想以及快速定点算法的实现方法,同时对定点和浮点算法结果进

2008-10-30 16:15:31 19

19 针对传统网格简化算法在对边界顶点和边界边、累进网格二义性以及网格拓扑关系有效保持等的处理所存在的不足进行了相应的改进,改进的网格简化算法能有效保持网格模型的形

2009-04-14 08:41:20 11

11

介绍了用VHDL 语言在硬件芯片上实现浮点加/ 减法、浮点乘法运算的方法,并以Altera

公司的FLEX10K系列产品为硬件平台,以Maxplus II 为软件工具,实现了6 点实序列浮点加/ 减法

2009-07-28 14:06:13 85

85 本文提出了基于TMS320C2XX 定点DSP 的浮点开平方算法,给出了实现方法及程序清单。实践证明该方法具有精度高、运算速度快、程序简单等特点。以美国 TI 公司的TMS320C2XX 为代

2009-07-31 08:11:43 42

42 新型应用受益于浮点DSP的高精度:自十多年前浮点数字信号处理器 (DSP) 推出以来,就为实时信号处理提供了算术上更为先进的备选方案。然而,定点器件至今仍是业界的支柱,当然成

2009-09-25 10:43:01 4

4 简化Xilinx和Altera FPGA调试过程:通过FPGAViewTM 解决方案,如混合信号示波器(MSO)和逻辑分析仪,您可以在Xilinx 和Altera FPGA 内部迅速移动探点,而无需重新编译设计方案。能够把内部FPGA

2009-11-20 17:46:26 26

26 在基于浮点DSP 的实时运算中,求平方根算法占用了大量的运算时间,成为运算中的瓶颈之一。本文提出一种基于二进制浮点数结构和查表法结合的快速求浮点数平方根方法。理论

2009-12-18 16:43:15 34

34 基于浮点编码遗传算法的H二控制器设计:本文研究了利用浮点编码的遗传算法的H-控制器的设计方法。文中对于利用遗传算法寻优的几个难点:如容许空间的确定、适应值函数的选取

2010-01-12 16:59:43 9

9 针对如何灵活应用高性能32/64位浮点DSP TMS320C672x提供的性能优良的外部存储器接口(EMIF),分析了EMIF的特点和使用技巧,以TMS320C6722B型 DSP为例,设计了EMIF与外部HY57V281620A型SDR

2010-12-11 15:36:52 20

20 助力航空和军事应用,Altera与Mentor Graphics在DO-254上展开合作

越来越多的航空和军事应用需要通过DO-254认证的组件,对此,Altera公司和Mentor Graphics公司日前宣布,双方展开合

2008-08-23 15:14:45 399

399 TMS320VC33 高性能浮点DSP芯片

TMS320VC33是美国TI公司新推出的TMS320C3X系列新一代浮点式数字信号处理器。它以高速、低功耗、低成本、易于开发为显著特

2009-12-08 14:33:27 6467

6467

浮点DSP,浮点DSP是什么意思

浮点DSP可以完成整数和实数运算,它的数据格式分为阶码和尾数(有一位可以设为符号位)。通常浮点DSP的

2010-03-26 14:57:01 2269

2269 Altera公司日前演示了使用FPGA的浮点DSP新设计流程,这是业界第一款基于模型的浮点设计工具,支持在FPGA中实现复数浮点DSP算法。伯克莱设计技术公司 (Berkeley Design Technology, Inc, BDTI) 进行

2011-09-15 08:48:58 898

898 Altera公司日前演示了使用FPGA的浮点DSP新设计流程,这是业界第一款基于模型的浮点设计工具,支持在FPGA中实现复数浮点DSP算法。

2011-09-15 09:07:10 613

613 WP409利用Xilinx FPGA打造出高端比特精度和周期精度浮点DSP算法实现方案: High-Level Implementation of Bit- and Cycle-Accurate Floating-Point DSP Algorithms with Xilinx FPGAs

2012-01-26 18:03:05 25

25 Altera Stratix25DSP在DSP设计实验教学中的应用

2012-08-15 16:30:44 28

28 电子发烧友网核心提示 :Altera公司昨日宣布,在业界率先在28 nm FPGA器件上成功测试了复数高性能浮点数字信号处理(DSP)设计。独立技术分析公司Berkeley设计技术有限公司(BDTI)验证

2012-10-31 09:24:47 31

31 STM32F4的浮点 DSP 运算效率不高

2015-12-07 17:55:14 0

0 程序设计、寻址方式、COFF结构和DSP芯片特殊功能的编程;根据实际应用讨论了常用算法,最后介绍了两种实验系统,即基TMS320VC33、TMS320C6722的浮点实验系统。

2016-04-26 10:53:09 2

2 程序设计、寻址方式、COFF结构和DSP芯片特殊功能的编程;根据实际应用讨论了常用算法,最后介绍了两种实验系统,即基TMS320VC33、TMS320C6722的浮点实验系统。

2016-04-26 10:53:09 2

2 程序设计、寻址方式、COFF结构和DSP芯片特殊功能的编程;根据实际应用讨论了常用算法,最后介绍了两种实验系统,即基TMS320VC33、TMS320C6722的浮点实验系统。

2016-04-26 10:53:09 1

1 TI的TMS320系列DSP已经有多宽浮点运算

2016-06-21 17:56:39 10

10 前言本文目的是演示如何使用STM32F30x 内部的DSP 进行浮点快速傅立叶变换(FFT),为联系实际应用

2017-09-18 06:44:00 9050

9050 摘 要: 简要分析了伪随机序列中应用广泛的m序列,Gold序列及平衡Gold码的概念、原理和应用。提出了一种基于Altera的DSP Builder工具箱的伪随机序列产生器设计方法,并通过设计实例

2017-10-30 10:37:11 0

0 DSP的比较优势是浮点算法拥趸者们在浮点定点之争的话题中常提及的,也为大多数嵌入式设计工程师所熟知。 然而,由于电路复杂性和制造工艺上的原因,浮点处理器与定点处理器相比在成本和功耗上通常具有明显的劣势,从而导致浮点处理器的卓越处理能力、大

2017-11-02 11:26:22 0

0 引 言 DSP结构可以分为定点和浮点型两种。其中,定点型DSP可以实现整数、小数和特定的指数运算,它具有运算速度快、占用资源少、成本低等特点;灵活地使用定点型DSP进行浮点运算能够提高运算的效率

2017-11-02 11:26:42 2

2 DSP的比较优势是浮点算法拥趸者们在浮点定点之争的话题中常提及的,也为大多数嵌入式设计工程师所熟知。 然而,由于电路复杂性和制造工艺上的原因,浮点处理器与定点处理器相比在成本和功耗上通常具有明显的劣势,从而导致浮点处理器的卓越处理能力、大

2017-11-02 11:46:27 0

0 定点DSP和浮点DSP的区别与比较 定点与浮点运算DSP 的比较DSP数字信号处理器是一种特别适合于进行数字信号处理的微处理器,主要用于实时快速地实现各种数字信号处理算法。 定点运算DSP

2017-12-04 15:57:19 11

11 描述了浮点型算法的加、减、乘、除的verilog代码,编写了6位指数位,20位小数位的功能实现并且通过仿真验证

2018-01-16 14:15:54 1

1 2014年4月23号,北京Altera公司 (Nasdaq: ALTR) 今天宣布在FPGA浮点DSP性能方面实现了变革。Altera是第一家在FPGA中集成硬核IEEE 754兼容浮点运算功能

2018-02-11 13:34:00 6954

6954 浮点运算是计算机运算的重要方式,较之定点运算有着计数范围宽有效精度高的特点。在各种工程计算和科学计算中有着广泛应用。目前浮点运算大多采用DSP芯片实现,具有算法简单,精度高的优点。但同时由于浮点运算

2018-04-10 14:25:53 17

17 此次为期30分钟的视频演示介绍了 Xilinx 提供的 DSP 设计工具。我们从带有浮点 MATLAB® 算法的 AccelDSP™ 着手,并且与测试平台一起生成 VHDL 或 Verilog 模型。

2018-05-24 13:47:00 4141

4141

Altera市场行销部高级副总裁Danny Biran介绍了该公司28nm的DSP创新,拟2011年1季度面试,开发软件DSPB-AB今年5月即可面试。这些Stratix V家族DSP锁定三大海

2018-06-22 05:28:00 3927

3927 本文档的主要内容详细介绍的是DSP28335的测试总结资料和程序免费下载包括了:1 DSP的PWM信号,2 DSP的CAN通信,3 DSP的32位浮点运算测试,4 DSP定时器中断,5 DSP看门狗复位,6 软件报错与处理,7 备注与注意事项,8 附录 C源程序。

2019-08-20 08:00:00 18

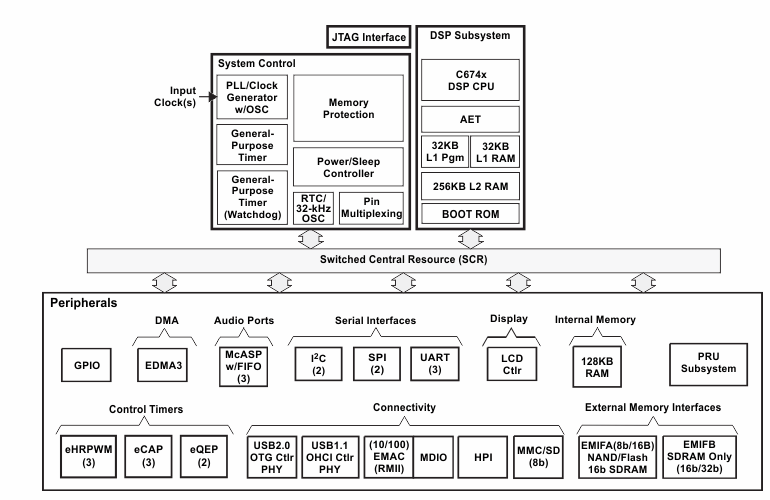

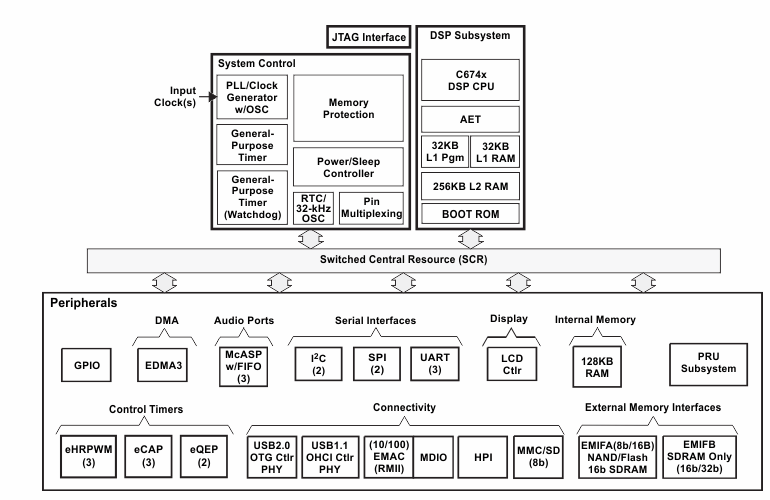

18 TI TMS320C6748定点/浮点DSP C674x处理器提供语音、算法、图像、视频等多种类型实验提供教学实验指导手册和完整的实验代码。

2019-11-10 10:20:45 2761

2761

的逻辑和布线资源。通常一个单精度浮点加法器需要500个查找表(LUT),单精度浮点要占用30%的LUT,指数和自然对数等更复杂的数学函数需要大约1000个LUT。因此随着DSP算法越来越复杂,FPGA

2020-01-14 16:19:55 3213

3213

德州仪器(TI)日前发布的两款超低功耗浮点DSP──TMS320C6745、TMS320C6747,以及一款结合ARM应用处理器与浮点DSP的OMAP-L137。三款组件均以TI C674x DSP核心为基础,具备浮点优势与过去定点装置独具的联机外围、低功耗及低成本等特性。

2021-01-06 11:15:00 2691

2691

该问题由某客户提出,发生在 STM32F407IGT6 器件上。据其工程师讲述:由于在其产品中,需要使用STM32进行大量的浮点数以及浮点DSP运算,所以针对STM32的浮点数运算能力及 DSP

2021-04-28 15:17:02 10

10 先进的数字处理器IC要求通过单独的DC参数和高速数字自动测试设备(ATE)测试,以达到质保要求。这带来了很大的成本和组织管理挑战。本文将介绍ADGM1001 SPDT MEMS开关如何助力一次性通过

2022-11-30 09:39:21 530

530 运算的运算步骤远比定点运算繁琐,运算速度慢且所需硬件资源大大增加,因此基于浮点运算的LMS算法的硬件实现一直以来是学者们研究的难点和热点。 本文正是基于这种高效结构的多输入FPA,在FPGA上成功实现了基于浮点运算的LMS算法。测试

2023-12-21 16:40:01 228

228

电子发烧友App

电子发烧友App

评论