电子发烧友网讯:越接近年末,PLD各大厂商越是动态频频,你追我赶之势更甚。为谋求差异化发展之路,FPGA厂商以及EDA厂商们各有何政策出台?他们如此大张旗鼓,到底意欲何为?电子发烧友网编辑为您对过去一周PLD行业焦点进 行梳理和整合,特此推出最新一期《PLD每周焦点聚焦 (12.09-12.16)——聚焦PLD第51周:谋求差异化发展,PLD厂商意欲何为?》,以飨读者。精彩内容提前看:Xilinx 在华为年度质量评分表中获得满分。Lattice半导体庆祝其超低密度iCE40 FPGA系列出货量达1500万片。Altera一天之内“软硬兼施”,更是携手ARM,意图何在?国产FPGA京微雅格意图抢占FPGA市场份额到底可信与否?EDA厂商集聚一堂,齐齐攻垒应用市场?更多精彩内容,请继续浏览本文,精彩内容不容错过!

1. PLD厂商资讯快递

1.1 赛灵思(Xilinx)荣膺华为“2012年最佳核心合作伙伴”奖

2012年12月11日,中国北京—全球可编程平台领导厂商赛灵思公司(Xilinx)宣布荣膺华为“2012年度核心合作伙伴”大奖,表彰其28nm 技术的领先性及出色的质量、产品交付与服务支持。赛灵思公司因其出色的业务及全球发展的表现,在华为的质量评分表上获得满分。2012年,Xilinx交付下一代所有可编程FPGAs、SoCs、3D ICs和Vivado设计套件。其所有可编程组合系列具备集高性能、低功耗和高集成度于一体,加上Vivado设计套件,为华为在网络、无线、企业和设备等领域的应用提供了更智能、集成性更高、带宽更高的系统解决方案。

1.2 Altera正式发售面向嵌入式系统的Cyclone V SoC FPGA

2012年12月13号,北京——Altera公司今天宣布,首次正式发售其28 nm SoC器件。通过宽带互联干线链接,Altera SoC FPGA紧密集成了双核ARM® Cortex™-A9 MPCore™处理器、存储器控制器、多种外设以及Cyclone® V和Arria® V级FPGA,支持无线通信、工业、视频监控、汽车和医疗设备市场的开发人员开发定制SoC型号产品,优化满足了系统功耗、电路板面积,以及性能和成本需求。

1.3 莱迪思(Lattice)iCE FPGA系列出货量达到1500万片

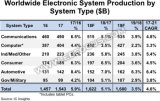

莱迪思半导体公司2012年12月12日宣布自从2011年12月以来,已经发运了1千5百万片iCE FPGA器件,包括其标志性产品超低密度iCE40 FPGA系列,成为了公司过去十年来出货最快的产品。这一了不起的数字反映了iCE40器件正以前所未有的速度获得移动消费类应用的广泛采用,这一领域占据了绝大多数的器件出货量。

1.4 Cadence致力于完善EDA工具,为业界提供整套方案

Cadence致力于完善EDA工具,为业界提供从系统设计 验证、芯片实现到三维封装以及PCB 板级的整套方案。随着先进工艺20nm时代的到来,Cadence在以ADE为主的条件下,继续推广“模拟设计约束”的新方法以减小设计失误,继续加强 PDK的功能以提高设计效率,继续提供DFM的制造和设计工具以增加产品额度。目前,Cadence以QRC、PVS和DFM为主的若干工具已经经过产品 验证并成为代工厂20nm设计的首选。

2. PLD芯品新知

2.1 Altera和ARM携手推出DS-5开发套件,加速产品开发时间

Altrea与安谋国际(ARM)携手突破SoC FPGA除错壁垒。Altera与ARM透过双方特有协议,共同推出DS-5嵌入式软件开发套件,期消除工程师在开发SoC FPGA时,所面临的软硬件除错问题,进一步加速开发时程。DS-5开发套件在上市之后,将支援对运行非对称多处理(AMP)和对称多处理(SMP)系统组态的系统进行除错,还可以透过JTAG和乙太网路除错介面,广泛应用于电路板开发、驱动程式开发、OS移植、裸金属和Linux应用开发和除错。

2.2 东芝新推CMOS多功能门逻辑器件,满足移动设备需求

东芝公司(Toshiba Corporation)推出了新系列的CMOS多功能门逻辑器件,支持5V系统,并采用1.0mm x 1.45mm x 0.55mm的小型MP6封装,适用于移动电话、智能手机、平板电脑、数码相机和数码摄像机等小型移动设备。该系列将于明年1月份推出样品,并计划于3月份开始量产。

2.3 Cypress推出PSoC 5LP器件,助力高精度模拟应用

Cypress公司日前推出了完全认证的PSoC 5LP可编程片上系统系列。这些全新器件可提供无与伦比的高性能可编程模拟、ARM Cortex-M3器件上最佳的ADC、以及利用80多个预验证可随时投产的PSoC Creator IDE组件设计定制系统的灵活性。其它领先同类竞争产品的特性包括0.5-V集成升压启动、1.71-5.5-V全功能模拟以及业界最广泛的工作电压范围(0.5-5.5V)等。这些功能让需要单节电池性能和高精度模拟的全新应用面向固定功能MCU之外的世界敞开了大门。

2.4 攻垒AMS设计方案,EDA商力推模拟/验证工具

电子设计自动化(EDA)大厂正卯足劲强攻高速模拟混合信号(AMS)设计模拟/验证方案。随着系统单晶片(SoC)内部模拟混合讯号电路激增,包括明导国际(Mentor Graphics)、新思科技(Synopsys)及益华电脑(Cadence),均积极扩展相关芯片模拟与验证工具阵容,以便加速高复杂性SoC开发流程,并确保芯片品质与效能无虞。各大EDA厂商举措如何,详见:【攻垒AMS设计方案,EDA商力推模拟/验证工具 】

3. PLD市场动态扫描

3.1 京微雅格何以狭缝求存?

当前,随着FPGA市场竞争日益白热化,Xilinx、 Altera和Lattice等FPGA巨头竞相推陈出新,呈现百舸争流之势。相比Xilinx和Altera等FPGA枭雄,京微雅格似乎显得有些微不足道。京微雅格能否在三国鼎立之势,从FPGA市场中分得一杯羹?电子发烧友网编辑将从国家政策支持、迂回的市场策略以及灵活的产品优势等几个方面来深入观察国产FPGA后起之秀--京微雅格何以在日益激烈的市场竞争中狭缝求存,探求中国FPGA厂商以及技术产品发展之路。

点击图片,浏览原文:【京微雅格何以狭缝求存? 】

3.2 Altera FPGA助力众志和达进军8Gbps存储市场

2012年12月12日,北京—Altera公司宣布,中国信息存储与数据安全领域领先的技术与服务提供商无锡众志和达存储技术股份有限公司(简称众志和达)采用Altera FPGA解决方案构建8Gbps光纤通道协议存储,正式进军8GFC存储市场,也因此成为国内唯一一家具备独立研发光纤通道协议硬核知识产权(IP)、自主生产光纤通道协议主机总线适配器(HBA)实力的领先存储厂商。这是众志和达在其芯片级存储(Storage-on-Chip)技术基础之上的又一次重大突破。

3.3 Cadence为Renesas微系统公司加速实现周期并降低成本

全球电子设计创新领先企业Cadence设计系统公司 日前宣布Renesas微系统有限公司已采用Cadence Encounter RTL Compiler用于综合实现,尤其是将复杂ASIC设计的芯片利用率提高了15%,面积减少了8.4%,加速了实现周期并降低了成本。Cadence的 实现技术为Renesas微系统有限公司提供了更快速、更高效的芯片生产方式。

3.4 Altera“软硬兼施”,携手ARM意欲何为?

FPGA厂商围绕28nm工艺节点的战役已经热热闹闹的上演了两年时 间,就在我们怀疑是否Altera采用的HP工艺出现问题,而导致28nm产品不能上市的时候,Altera宣布其最新SoC FPGA产品开始发售了,客户已经可以开始下订单。同一天,Altera向媒体宣布推出其携手ARM酝酿和开发了一年,旨在消除SoC FPGA中CPU和FPGA间调试壁垒的开发套件DS-5工具包。Altera如此“软硬兼施”,携手ARM到底意欲何为?敬请浏览原文分析:【Altera“软硬兼施”,携手ARM意欲何为? 】

4. PLD热门技术聚焦

4.1 2012年工程师最爱FPGA技术热文TOP10

2012 年电子发烧友网发表和整合了很多FPGA相关的文章。关于FPGA核心知识详解、 FPGA芯片设计、FPGA解决方案、FPGA工程师经验传授,甚至FPGA厂商产品大比拼,精彩无限,不容错过。值此年终之际,电子发烧友网特此推出一 系列回顾性文章,意在帮助电子爱好者、工程师以及相关厂商梳理2012年最受欢迎的技术趋势和最新热点。电子发烧友网更多回顾系列文章即将推出,敬请期待!

点击图片,浏览更多FPGA技术热文【 2012年工程师最爱FPGA技术热文TOP10 】

4.2 赛灵思FPGA DIY系列(3):HDUSec-网络行为分析监控系统

HDUSec-网络行为分析监控是集分析、监控、报警功能于一体的网络行为监控,通过本系统可以实现对局域网中用户网络行为的分析、监控,并且能够对非法攻击进行报警,从而为用户提供一个良好的上网环境。本系统能够提供一个良好的使用和管理环境,为用户提供方便的一体化系统。本系统采用NetFPGA、Linux系统及B/S架构等进行设计与实现。详情浏览原文:【赛灵思FPGA DIY系列(3):HDUSec-网络行为分析监控系统 】

4.3 玩转赛灵思Zedboard开发板(4):如何使用自带外设IP让ARM PS访问FPGA?

本文目的是使用XPS为ARM PS 处理系统添加额外的IP。从IP Catalog 标签添加GPIO,并与ZedBoard板子上的8个LED灯相连。当系统建立完后,产生bitstream,并对外设进行测试。本文给出流水灯实现过程的详细步骤截图。更多赛灵思(Xilinx)Zedboard基础知识、相关手册以及应用实例将陆续推出,以飨读者,敬请期待。原文详见:【如何使用自带外设IP让ARM PS访问FPGA?】,工程文件下载:【相应源代码 】

电子发烧友网编辑点评

纵观第51周各大PLD厂商之间的此起彼伏,可谓是“山雨欲来风满楼”。然则,各大厂商均由早前的“剑拔弩张”,到现在的差异化发展、竞争策略上的互不相让!竞争得最为激烈的要数Xilinx 和Altera双雄,在28nm FPGA战场上,Xilinx和Altera就已经展现了两种完全不同的竞争策略:Xilinx追求性能与功耗并重,Altera则更热衷于性能的提升。到现在两者再一次双双提出20nm规划,Altera以三大创新技术自居,Xilinx则继续领先下一代。如今,国产FPGA顺势崛起,意图分瓜FPGA 市场份额。到底京微雅格能否续写国产FPGA新传奇,终究是需要时日的见证。只是,未来PLD市场的精彩却是毋庸置疑的。PLD领域充满了许多不确定性,各大厂商之间这种良性竞争,对于整个产业链而言,无疑是有百利而无一害。各大厂商间的竞争最直接受益的将会是工程师群体以及整个PLD行业的蓬勃发展。

想了解以往每周PLD厂商之间的精彩PK、获得更多PLD市场动态,请点击关键字【PLD每周焦点 】即可大饱眼福!敬请继续关注电子发烧友网相关报道。

——电子发烧友网版权所有,转载请注明出处!

电子发烧友App

电子发烧友App

评论