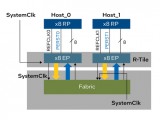

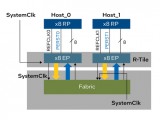

Arm Neoverse S3 是 Arm 专门面向基础设施的第三代系统 IP,应用范围涵盖高性能计算 (HPC) 、机器学习 (ML)、边缘和显示处理单元,是新一代基础设施系统级芯片 (SoC) 的理想技术根基。

2024-03-22 11:30:01 202

202

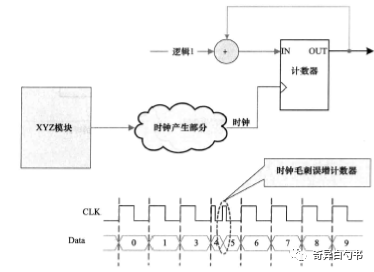

在SPI双机通信中,时钟信号由主机提供,那么从机向主机发送数据时需要时钟信号吗?从机是怎样通知主机产生时钟信号的?

2024-03-14 06:49:32

发现和识别故障实时数据分析数据包分析数据包快速捕获和解码随着基础设施环境的快速变化和技术的不断进步,用户数量和IT基础设施流量迅速增加,服务故障的数量也相应增加。此时,服务中断不仅会带来直接的不便

2024-03-05 08:05:08 227

227

IEEE 802.1Qbv作为一项针对实时流量时间敏感性进行优化的重要标准,在网络通信领域具有广泛的应用前景。通过引入时间感知调度机制和支持多个优先级,IEEE 802.1Qbv为实时应用程序提供了可靠的网络基础设施,满足了各种应用场景对延迟和时序性的高要求。

2024-02-29 17:19:46 332

332

开放式、虚拟化无线接入网络(开放式vRAN)正迎来商用设计和部署的强劲发展势头,智能计算创新和AI对5G基础设施的重要性也在快速增加。作为通信和AI技术的领军企业,高通技术公司一直处于行业前沿推动现代5G网络的未来发展。

2024-02-21 09:11:47 227

227 随着企业信息化程度的不断提高,IT基础设施的重要性日益凸显。如何构建高效、安全的IT基础设施成为了企业面临的重要挑战。KVM矩阵系统作为一种先进的远程管理解决方案,以其高效、灵活、安全的特点,成为

2024-02-18 14:53:02 243

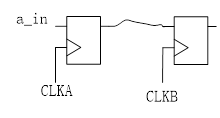

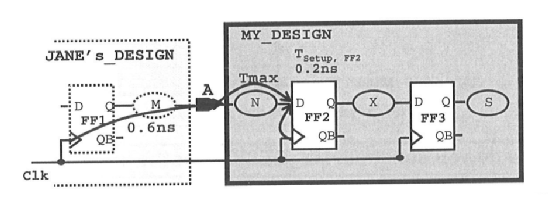

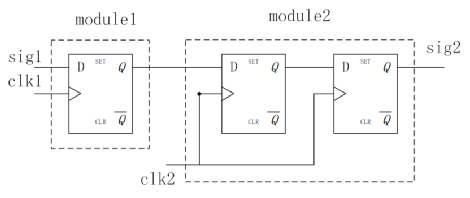

243 时序电路基本原理是指电路中的输出信号与输入信号的时间相关性。简单来说,就是电路的输出信号要依赖于其输入信号的顺序和时间间隔。 时序电路由时钟信号、触发器和组合逻辑电路组成。时钟信号是时序电路的重要

2024-02-06 11:30:00 344

344 时序电路是一种能够按照特定的顺序进行操作的电路。它以时钟信号为基准,根据输入信号的状态和过去的状态来确定输出信号的状态。时序电路广泛应用于计算机、通信系统、数字信号处理等领域。根据不同的分类标准

2024-02-06 11:25:21 393

393 电路,并探讨时序电路中可能存在的状态循环。 首先,同步时序电路是指时序元件按照整个系统的时钟信号进行同步操作的时序电路。常见的同步时序元件有锁存器和触发器。锁存器可以将输入信号“锁定”,在时钟上升沿或下降沿将输入信

2024-02-06 11:22:30 288

288 FPGA输入的时钟信号必须是方波么?正弦波会有影响么? FPGA是一种可编程逻辑器件,通常用于实现数字电路。输入时钟信号是FPGA中非常重要的时序信号,对整个系统的稳定性和性能都有很大

2024-01-31 11:31:42 1238

1238 芯片为什么要时钟信号 时钟芯片的作用是什么? 时钟信号在芯片中起着非常重要的作用。它是芯片的“心脏”,相当于人体的心脏,用于同步和控制芯片中的各个功能模块之间的操作。时钟信号可以提供一个稳定的时间

2024-01-29 18:11:31 621

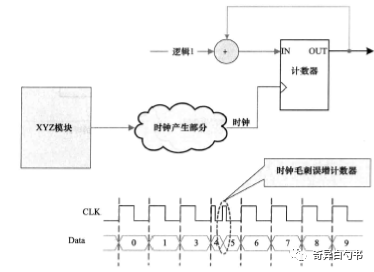

621 什么是时钟信号?数字电路的时钟信号是怎么产生呢? 时钟信号,也称为时钟脉冲,是用于同步数字电路中所有操作的基本信号。它提供了一个参考频率,使得所有电路元件都能按照同样的节奏进行工作。时钟信号

2024-01-25 15:40:52 894

894 将两个支持相同协议的设备通过同步通信串口连接,怎么保证两个通信串口的时钟信号是同步启动的呢?这一步是靠软件实现还是硬件实现,如果在建立完成之前,两台设备的通信时钟恰好是正交的,那么此时该让主设备还是从设备等待这1/4/个周期呢,这1/4个周期会不会影响其它正常功能的运行?

2024-01-19 14:55:15

算力供给的凛冽中,联想点燃AI基础设施的“火种”

2023-12-25 09:53:27 608

608

关注计算能力的提升,通信基础设施的提升跟不上,那么数据中心的整体系统性能依然受限,无法发挥出真正的潜力。DPU的提出背景就是应对这些数据量和复杂性的指数级增长。未来,需要将计算移至接近数据的位置,这是

2023-12-21 10:47:01

作为集信息计算力、网络运载力、数据存储力于一体的新型生产力,算力主要通过算力基础设施向社会提供服务。因此,做强做优做大我国数字经济,促进数字经济与实体经济融合发展,必须筑牢算力基础设施的坚实底座。

2023-12-20 16:26:23 270

270 我最近做一个CCD的项目,需要用到AD9945,因为他的频率高,但是AD9945怎么与STM32F103外部引脚连接,他输出的12位并行数据接到哪里?还有AD9945与STM32之间通过SPI通信,通信时序怎么写?时序图如下:

2023-12-05 08:28:07

以上两图分别为AD2S1210并口配置模式下写时序和普通模式下读时序

请问这两个图中的CLKIN是什么时钟?并口通讯的时候需要用时钟吗?

我的理解是,

并口配置模式下写寄存器,控制信号用nCS

2023-12-04 06:00:23

电子发烧友网站提供《磁隔离对延迟时序性能的改善.pdf》资料免费下载

2023-11-27 09:44:05 0

0 差分探头是一种常用的测量差分时钟时延的工具。差分时钟是指由两个相互关联的时钟信号组成的时钟系统,其中一个时钟信号被称为主时钟,另一个被称为辅助时钟。测量差分时钟时延有助于了解时钟信号的稳定性和准确性

2023-11-24 10:54:42 291

291 时钟的时序特性主要分为抖动(Jitter)、偏移(Skew)、占空比失真(Duty Cycle Distortion)3点。对于低速设计,基本不用考虑这些特征;对于高速设计,由于时钟本身的原因造成的时序问题很普遍,因此必须关注。

2023-11-22 09:29:16 350

350

电子发烧友网站提供《完美时序-时钟产生和分发设计指南.pdf》资料免费下载

2023-11-18 10:27:02 0

0 和时钟偏差组成的。

二、时序路径

时序路径是指从FPGA输入到输出的所有逻辑路径组成的路径。当存在时序路径时,需要考虑时序约束以确保正确的逻辑功能和时序性能。

时序路径中的关键元素包括:

(1) 路径

2023-11-15 17:41:10

我连接了 8 个 LTC6804 用两线制通信都没有问题

但连接到第9 或 10 个时 读取电池电压偶尔就会发生 pec error 问题

请问这情况是什么问题?

是超过了 isoSPI 菊链上限了吗?

2023-11-10 07:45:35

的核心部分。主要包括以下几个方面的指标: - 功耗测试:衡量芯片在不同工作状态下的能耗。 - 时序测试:测试芯片内部各个模块之间的时序关系,确保信号的正确传递。 - 时钟性能测试:评估芯片对外部时钟源的输入和输出响应速度。 - 噪声测试:测

2023-11-09 09:24:20 421

421 同步通信的原理是发送端在发送串行数据的同时,提供一个时钟信号,并按照一定的约定(例如:在时钟信号的上升沿的时候,将数据发送出去)发送数据。接收端根据发送端提供的时钟信号,以及双方的约定,接收数据

2023-11-07 08:07:32 1813

1813

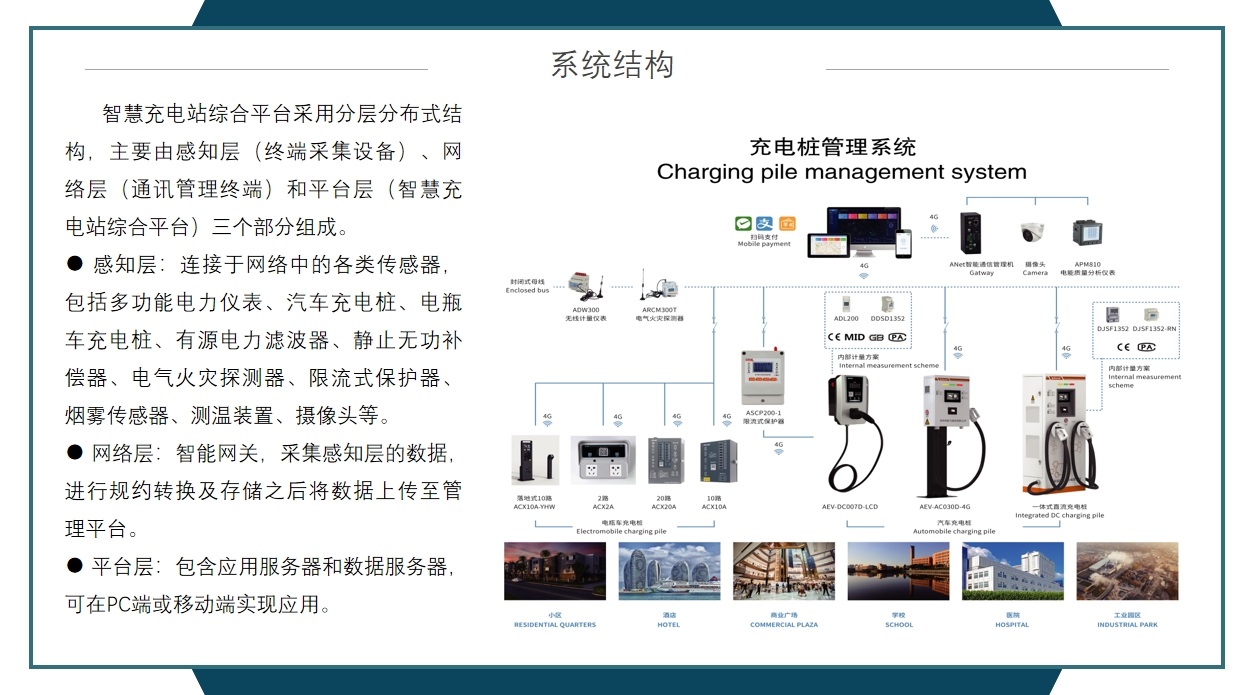

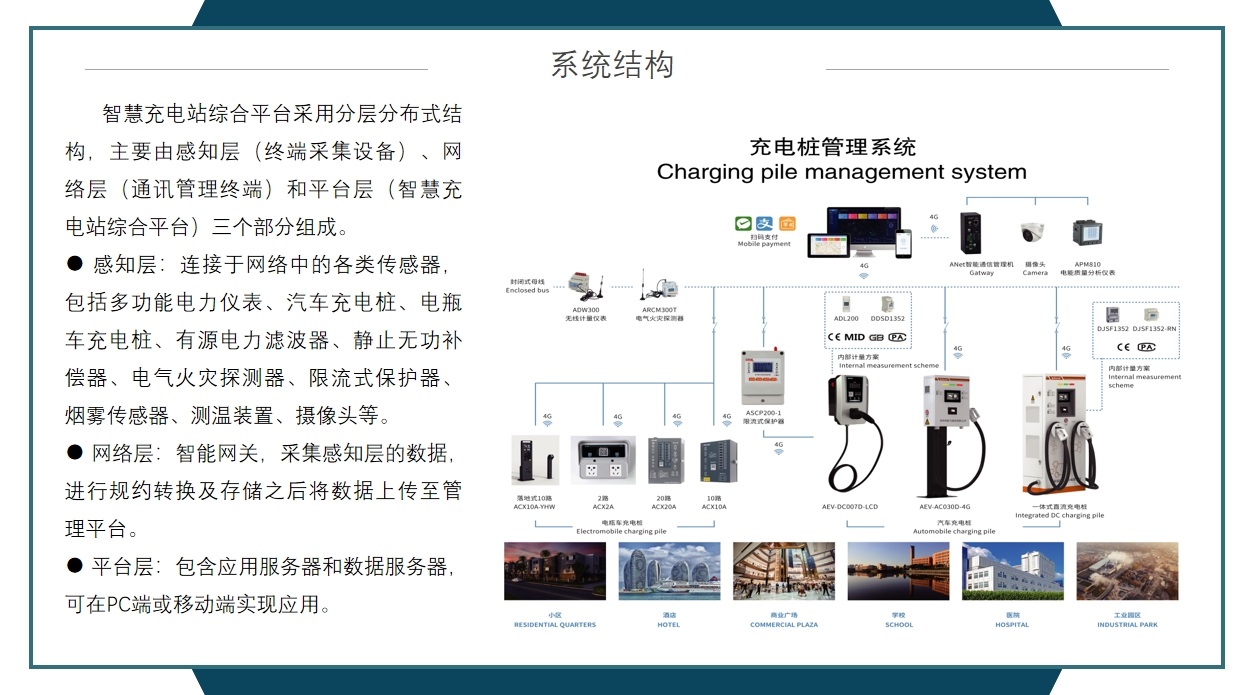

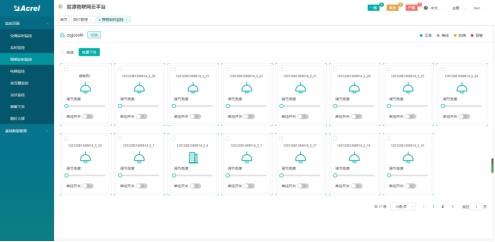

随着新能源汽车的普及,充电基础设施的建设和管理显得尤为重要。为了满足市场需求,提高充电设施的运营效率和服务质量,公司推出了一款充电桩收费运营云平台,为充电设施的智能化管理提供了解决方案。

2023-11-06 14:54:57 368

368

时 , 将输入 D 端的数据给到输出 Q, 当使能条件不满足时 , 输入数据 D 会暂存在触发器当中 , 直到触发条件满足才给到输出 Q。 (2):D 触发器工作时序 时钟 clk: 周期性变化信号 。 时钟极性 (CPOL): 时钟初始值是 0, 时钟极性为 0; 时钟初始值是 1, 时钟极性为 1。

2023-11-02 12:00:01 305

305

我们看到,今年的Forrester Wave超融合基础设施图,领导者(第一象限)是Nutanix和VMware,表现强劲者(第二象限)有HPE,微软和深信服、Cisco。其他的都是竞争者(第三象限),有浪潮信息,华为、IBM、Scale Computing、SmartX。

2023-10-29 17:01:19 511

511

电子发烧友网报道(文/周凯扬)从数智化转型的角度来看,如何结合云边端的基础设施共建智慧园区,已经成了智慧城市建设中最关键的一环。尤其是在城市人口规模持续增长的前提下,无缝结合关键基础设施和数字技术

2023-10-26 09:01:20 1131

1131

如何用时钟振荡器产生稳定的100hz或1hz的时钟信号? 时钟信号是电子系统中至关重要的组成部分,用于同步各种信号和操作。它需要稳定、准确、可靠地工作,以确保系统性能。时钟信号的产生可以通过许多

2023-10-25 15:07:55 954

954 什么器件可以产生时钟信号?时钟信号是用来做什么用的?时钟信号起什么作用? 时钟信号是一个精确的电信号,它可以通过电子器件来产生,并且具有一定的频率和周期。时钟信号在电子系统中具有非常重要的作用,因为

2023-10-25 15:07:45 635

635 不够标准,这可能导致系统性能下降或故障。因此,我们需要对这种情况进行适当的处理。 对于波形和电平不标准的时钟信号,一般应进行以下处理: 1. 时钟信号滤波 波形和电平不标准的时钟信号往往会出现抖动或噪声,这会对数字系

2023-10-24 10:04:38 663

663 2023年IDC全球SD-WAN基础设施市场报告发现, SD-WAN 基础设施市场在 2022 年激增 25%,预计到 2027 年将达到 75 亿美元,复合年增长率为 10.1% 。

2023-10-18 15:37:55 656

656

为什么异步fifo中读地址同步在写时钟域时序分析不通过? 异步FIFO中读地址同步在写时钟域时序分析不通过的原因可能有以下几个方面: 1. 读地址同步在写时钟域时序分析未覆盖完全 在时序分析时,可能

2023-10-18 15:23:55 309

309 时钟信号的同步 在数字电路里怎样让两个不同步的时钟信号同步? 在数字电路中,时钟信号的同步是非常重要的问题。因为在信号处理过程中,如果不同步,就会出现信号的混淆和错误。因此,在数字电路中需要采取一些

2023-10-18 15:23:48 771

771 基础设施,分为硬件基础设施和软件基础设施。硬件基础设施,包含常用器件库、封装库、原理图库和硬件参考设计等等;而今天我们讨论的重点,主要在于软件基础设施。

2023-10-12 16:09:50 363

363 [中国,上海,2023年9月20日] 在华为全联接大会2023期间,华为数字能源举办新型数字产业能源基础设施分论坛,全球200多位行业领袖、技术专家、生态伙伴齐聚上海,共同探讨数据中心能源、行业关键

2023-09-20 19:40:09 388

388

[中国,上海,2023年9月20日] 华为全联接大会2023于9月20-22日在上海世博展览馆盛大举办。华为数字能源展示了绿色低碳的全场景数字能源解决方案及商业实践,新型数字产业能源基础设施、清洁

2023-09-20 19:40:05 353

353

是数据信号(SDA)。SCL信号是在IIC通信中非常重要的一个信号,它确定了数据的传输速率以及同步时序。 IIC时钟信号的产生需要硬件支持,一般通过外部晶振或者内部时钟源产生。在IIC总线使用过程中,时钟信号的频率很重要,必须要与所有设备的时钟频率保持一致。一般来说,为了保证

2023-09-19 17:16:02 735

735 我们设计时要尽可能避免在内部产生时钟,如果操作不当,会导致设计功能和时序问题。总而言之,尽量在代码中避免操作时钟。

2023-09-19 09:26:42 424

424

,这篇文章将会详细介绍它们之间的差异。 单脉冲时钟信号是指在短时间内以一定的速率发生较短、高速峰值的脉冲信号。它们通常用于时序控制,计数和精确时钟测量系统中。一般而言,单脉冲信号所用的频率比较高,可达数百MHz级别,这比其他

2023-09-15 16:28:23 994

994 的基础,因此,在电子学领域中,如何产生和控制时钟信号是一项至关重要的技术。 时钟信号是指一个周期性的方波信号,其周期性能和稳定性非常重要。为了使时钟信号精确可靠地产生,需要考虑多种因素的影响,包括设备的稳定性、

2023-09-15 16:28:22 1490

1490 时钟脉冲的主要作用 时钟脉冲是指一个定时器发出的一系列电脉冲信号,这些脉冲信号在计算机系统中被广泛应用。时钟脉冲的主要作用是为计算机内部的所有操作提供精准的时间基准,包括支持CPU时序、同步数据

2023-09-15 16:28:17 1359

1359 芯片为什么需要时钟信号? 在我们日常生活中,我们所使用的各种电子设备都需要一个时钟信号来进行计时和同步,例如:手机、电脑、电视、汽车、机器人、智能家居等设备都需要时钟信号。对于各种这些电子设备

2023-09-15 16:28:14 1366

1366 件、计算机、数字电路和通讯协议等设备的信号。它的主要作用是进行时序控制,使数据传输和处理的时序保持一致。时钟信号一般由计时器产生,其具有一定的周期性、稳定性和精度。 时钟信号的主要信号参数包括周期、频率、精度和占空比等,

2023-09-15 16:28:12 1763

1763 电子发烧友网站提供《云基础设施速度下的安全控制.pdf》资料免费下载

2023-09-08 09:47:55 0

0 需要时钟信号来控制内部元件的工作节奏,以确保芯片的正常运转。 时钟信号是指一种周期性的信号,在芯片内部被用于同步元件的工作状态。时钟信号的基本作用是为芯片内部提供准确、稳定的时序信号,从而协调芯片内部各个部

2023-09-01 15:38:11 1373

1373 业界高端FPGA的卓越性能和高口碑声誉都有哪些因素了?其中很重要的一个因素就是FPGA内部丰富的时钟资源使得FPGA在处理复杂时钟结构和时序要求的设计中具有很大优势。设计师可以更好地控制和管理时钟信号,提高时序性能、减少时钟相关问题,并满足设计的高性能和稳定性要求。

2023-08-31 10:44:01 530

530 时钟电路的原理基于振荡器和时序控制逻辑。振荡器负责产生稳定的周期性信号,而时序控制逻辑用于控制和同步各个电子组件的操作和通信。

常用的振荡器包括晶体振荡器、RC振荡器和串扰锁相环(PLL

2023-08-24 15:40:10 8076

8076 AMBA™2 AHB™至AMBA 3 AXI™桥使AHB主机能够与AXI从机或互连进行通信(如果时钟和重置信号是公共的)。

该网桥有三种变种,可支持以下接口:

·ARM11 AHB-Lite主控器

2023-08-21 06:43:35

今日,全球著名技术分析机构DCIG(Data Center Intelligence Group)发布报告《DCIG 2023-24企业超融合基础设施TOP5》(以下简称“报告”),华为

2023-08-18 17:15:03 347

347 城市地下市政基础设施建设是城市安全有序运行的的重要基础。随着城市地下空间大面积的开发利用,各类地下空间安全事故呈多发趋势,城市内涝、地面塌陷、燃气爆炸、大面积停水停电等事故都对城市地下空间

2023-08-17 16:39:17 1686

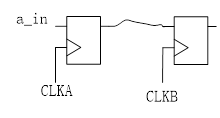

1686 单位宽(Single bit)信号即该信号的位宽为1,通常控制信号居多。对于此类信号,如需跨时钟域可直接使用xpm_cdc_single,如下图代码所示。参数DEST_SYNC_FF决定了级联触发器

2023-08-16 09:53:23 462

462

,每个处理器集群都为每个处理器核心包含一个交叉触发接口(CTI)组件。CTI和处理器核心之间的连接包括:•告知处理器核心停止调试活动的信号•指示处理器核心正在停止的信号每个CTI还连接到交叉触发矩阵

2023-08-10 07:01:18

正如“聚合”的意思(字典)“两个或多个事物聚集在一起的发生”。所以我们可以假设它也与 2 个时钟路径聚集在一起有关。 (了解时钟路径请参考另一篇博客-静态时序分析基础:第1部分“时序路径”)

2023-08-08 10:31:44 524

524

而 Arm 以优异的每瓦性能表现和更出色的吞吐率带来了成本优势,通过提供总拥有成本(TCO)优势及出色的能效表现,成为了 5G 网络基础设施能效考量中的绝佳之选。

2023-08-04 16:14:01 527

527

轻松绘制各种时序图,同时支持快捷键操作功能,操作简单便捷。TimeGen还可以自由设置各个文本框的属性字体样式、字体大小和颜色、可以标注信号之间的关系,调整信号周期的宽度,还能设置信号的背景图案。如下图1是小编自己画的一个时序图。

2023-08-04 10:42:15 6581

6581

FPGA设计中的绝大部分电路为同步时序电路,其基本模型为“寄存器+组合逻辑+寄存器”。同步意味着时序路径上的所有寄存器在时钟信号的驱动下步调一致地运作。

2023-08-03 09:27:25 912

912

可能无法满足时序要求。 跨时钟域信号的约束写法 问题一: 没有对设计进行全面的约束导致综合结果异常,比如没有设置异步时钟分组,综合器对异步时钟路径进行静态时序分析导致误报时序违例。 约束文件包括三类,建议用户应该将这三类约束

2023-08-01 09:18:34 1041

1041

随着每个 OSAT 和代工厂提供自己的技术,支持小芯片和异构结构的 IC 封装选项也不断传播。结果,术语变得相当混乱。值得庆幸的是,这些封装结构比目前行业中存在的术语简单得多。

2023-07-29 14:25:28 880

880

时序:字面意思,时序就是时间顺序,实际上在通信中时序就是通信线上按照时间顺序发生的电平变化,以及这些变化对通信的意义就叫时序。

2023-07-26 10:06:03 1639

1639 “全局时钟和第二全局时钟资源”是FPGA同步设计的一个重要概念。合理利用该资源可以改善设计的综合和实现效果;如果使用不当,不但会影响设计的工作频率和稳定性等,甚至会导致设计的综合、实现过程出错

2023-07-24 11:07:04 655

655

世界越来越依赖太空基础设施。这导致人们越来越意识到,它需要受到保护,免受网络攻击,而网络攻击可能会破坏关键的基础设施,造成巨大破坏。卫星在支持物流系统、自动取款机、航空公司等方面发挥

2023-07-20 16:28:56 414

414 今天我们要介绍的时序分析概念是clock gate。 clock gate cell是用data signal控制clock信号的cell,它被频繁地用在多周期的时钟path,可以节省功耗。

2023-07-03 15:06:03 1479

1479

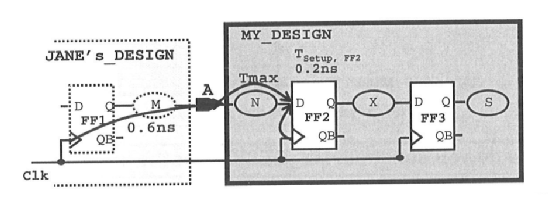

引言 在同步电路设计中,时序是一个非常重要的因素,它决定了电路能否以预期的时钟速率运行。为了验证电路的时序性能,我们需要进行 静态时序分析 ,即 在最坏情况下检查所有可能的时序违规路径,而不需要测试

2023-06-28 09:38:57 713

713

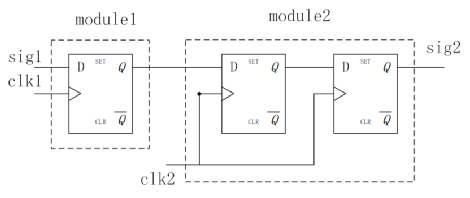

跨时钟域是如何产生的呢?现在的芯片(比如SOC,片上系统)集成度和复杂度越来越高,通常一颗芯片上会有许多不同的信号工作在不同的时钟频率下。

2023-06-27 11:39:41 894

894

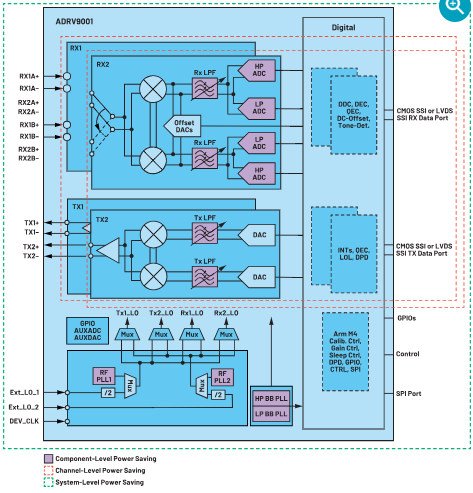

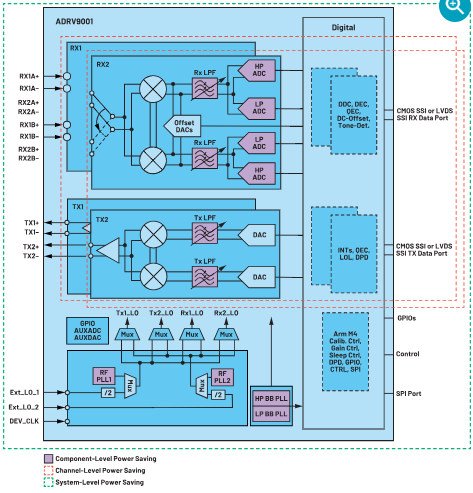

本文探讨了ADRV9001,这是ADI公司最新一代软件定义无线电(SDR)收发器单片集成电路(IC),旨在为卫星、军事、陆地移动、公用事业基础设施和蜂窝网络的众多关键任务型通信应用提供可扩展的功率和性能。它首先从组件级别、通道级别和IC系统级别介绍ADRV9001中的三个用户定义节能选项。

2023-06-14 16:22:37 618

618

前面几篇FPGA时序约束进阶篇,介绍了常用主时钟约束、衍生时钟约束、时钟分组约束的设置,接下来介绍一下常用的另外两个时序约束语法“伪路径”和“多周期路径”。

2023-06-12 17:33:53 861

861 在FPGA设计中,时序约束对于电路性能和可靠性非常重要。在上一篇的文章中,已经详细介绍了FPGA时序约束的主时钟约束。

2023-06-12 17:29:21 1226

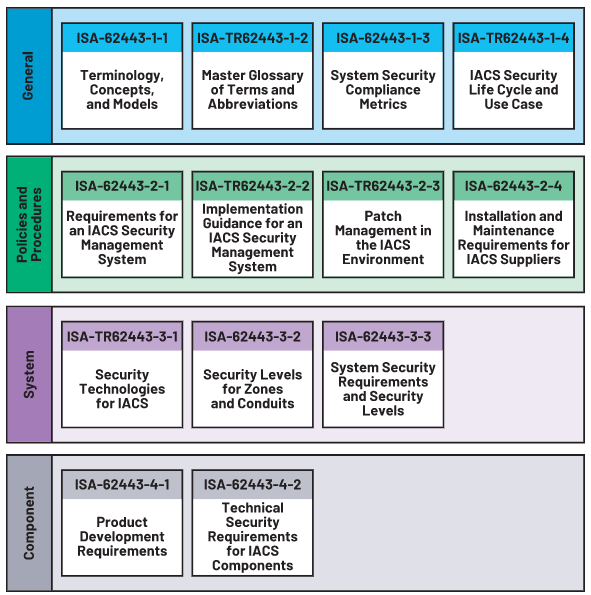

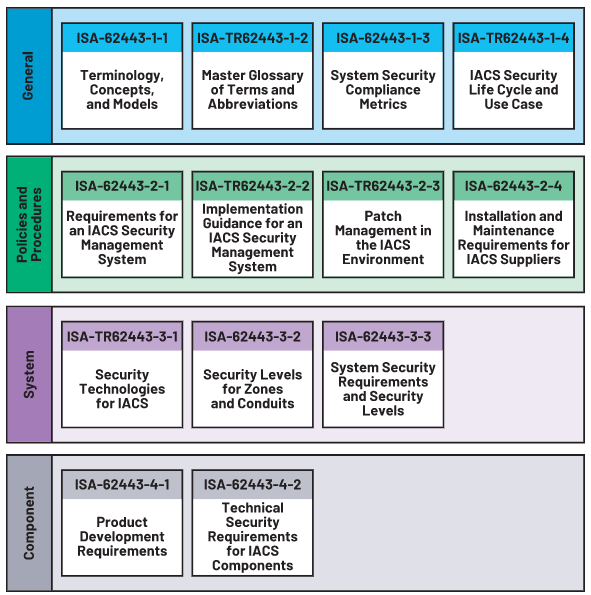

1226 本文探讨了IEC 62443系列标准的基本推理和优势,这是一组旨在确保网络安全弹性的协议 保护关键基础设施和数字化工厂。这一领先的标准提供了广泛的安全层;然而,它给那些寻求认证的人带来了一些挑战。我们将解释安全IC如何为努力实现工业自动化控制系统(IACS)组件认证目标的组织提供必要的帮助。

2023-06-08 11:34:58 1250

1250

在FPGA设计中,时序约束的设置对于电路性能和可靠性都至关重要。在上一篇的文章中,已经详细介绍了FPGA时序约束的基础知识。

2023-06-06 18:27:13 6194

6194

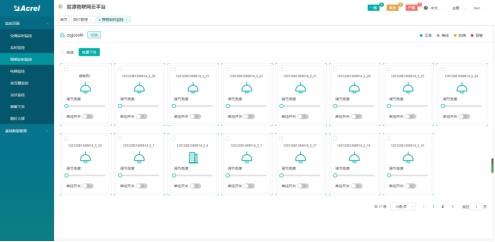

部等8部门共同印发《物联网新型基础设施建设三年行动计划(2021-2023年)》。 Acrel-EIoT能源物联网平台加速电网基础设施智能化改造和智能微电网建设,部署区域能源管理、智能计量体系、综合能源服务等典型应用系统。结合5G等通信设施的部署,搭建能

2023-06-05 09:59:22 607

607

自动驾驶对公路基础设施的影响主要包括物理基础设施、交通控制设备(TCD)和其它路边基础设施、运输管理和运营系统(TSMO)及其基础设施、多

式联运基础设施。

2023-06-01 14:25:57 0

0 随着城市科技现代化发展、综合管廊巡检是城市基础设施建设中重要的一环,承担着电力、通信、供水、排水等关键网络的运输和分发任务。为了保障城市运行的安全和顺畅必须不定时地对综合管廊巡检保养。然而,传统

2023-05-31 16:47:29 434

434

我们的团队可以帮助您选择正确的平台,并迁移您的服务器、数据库和应用程序。基于云解决方案的基础设施有助于最大的企业和增长最快的初创企业变得更加敏捷,并降低成本。

2023-05-30 09:13:44 243

243 设备旨在满足数据中心基础设施、云服务提供商 (CSP)、5G 通信服务提供商 (CoSP) 当前和未来的多种需求。

2023-05-29 15:14:48 1010

1010

算力基础设施是算力网络的核心,以构建高效、灵活、敏捷的算力基础设施为目标,积极引入云原生、无服务器计算、异构计算、算力卸载等技术,探索算力原生、存算一体等新方向, 持续增强算力能力,释放算力价值

2023-05-24 16:38:58 7

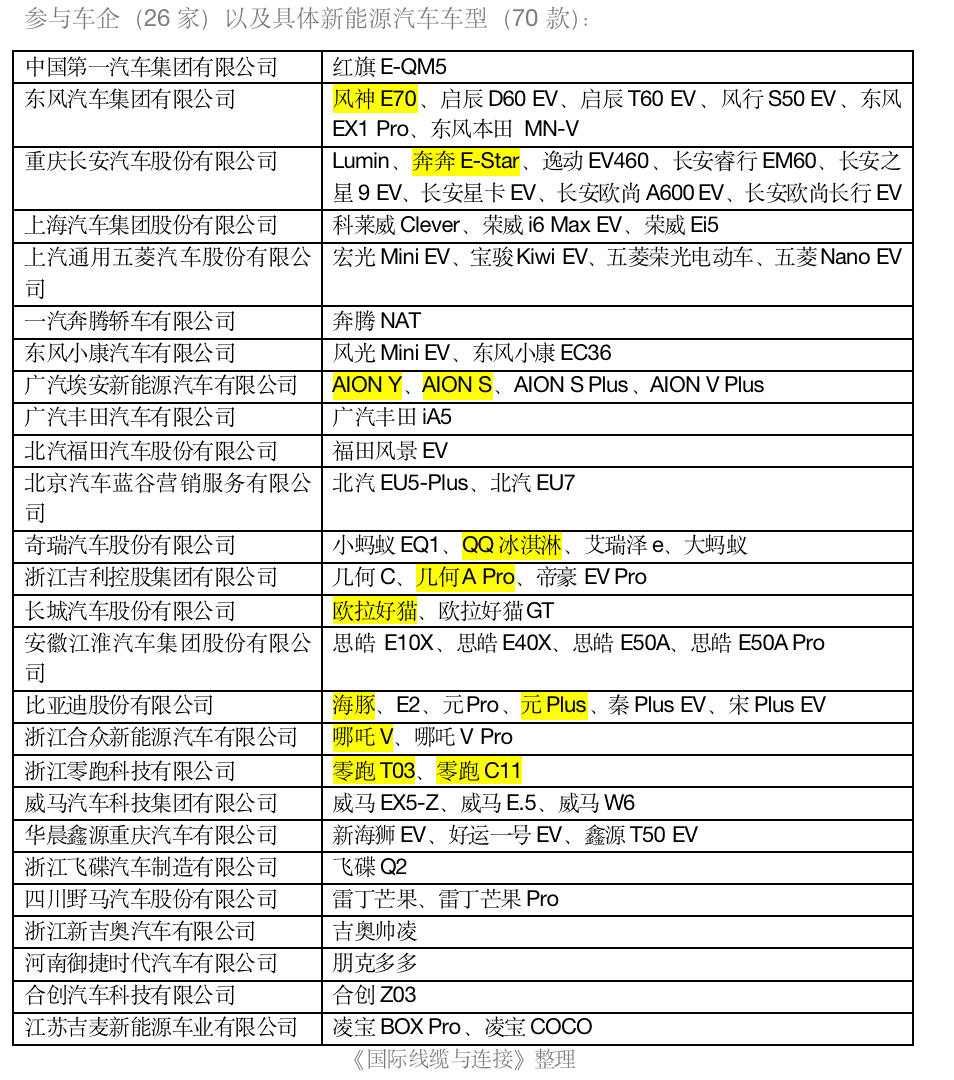

7 5月17日,国家发改委、国家能源局两部门联合发布《关于加快推进充电基础设施建设 更好支持新能源汽车下乡和乡村振兴的实施意见》。

2023-05-19 16:03:02 672

672

在无线通信方便快捷的背后,是一个又一个稳定可靠的通信节点,它们编织在一起,便是全时空场景下的高速移动互联。在每一个通信节点下,光纤、路由器、电源设备等高效协同,为无线通信提供稳定可靠的支持。而今天我们要谈论的元器件则是帮助那些无线通信基础设施满足网速、EMI等指标的连接器——有线连接与接插件。

2023-05-19 10:57:58 717

717

5月5日,国常会提出,要聚焦制约新能源汽车下乡的突出瓶颈,适度超前建设充电基础设施,创新充电基础设施建设、运营、维护模式。

2023-05-08 15:45:19 747

747

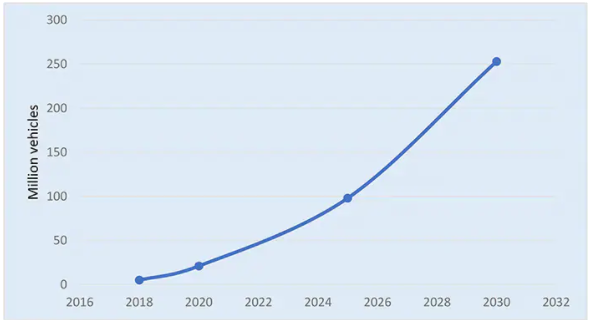

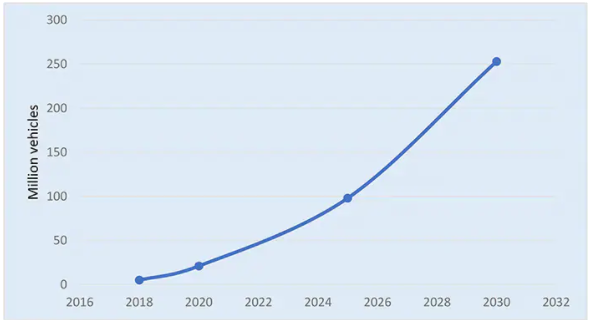

目前世界各地在争相将燃油汽车替换为电动汽车,预计电动汽车的普及率将迅速攀升。与目前部署的充电桩数量相比,预计电动车 (EV) 的迅速采用将会对可用的充电桩数量带来重大改变。在本文中,我们将研究电动车采用率的增加将对配电基础设施提出怎样的要求,以及在规划电动车充电基础设施时必须考虑的一些因素。

2023-05-08 10:29:03 326

326

时钟周期约束:用户需要将设计中的所有时钟进行约束后,综合器才能进行合理的静态时序分析。一个设计中的时钟主要分为两类:主时钟和生成时钟。主时钟包括由全局时钟引脚接入的时钟、高速收发器的输出时钟。

2023-05-06 09:31:34 1253

1253

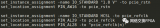

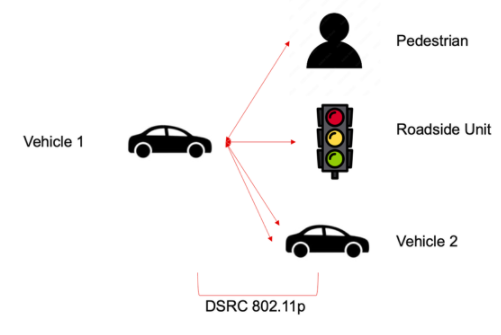

车辆到基础设施 (V2I) 是一种通信模型,允许车辆与支持一个国家高速公路系统的组件共享信息,例如交通信号灯、车道标记、路灯、标牌、架空 RFID 阅读器、摄像头和停车计时器。几乎任何物体,从建筑物到灯柱再到住宅区,都可以配备此功能。

2023-05-04 09:52:55 337

337

我正在尝试使用 i.MX8MP EVK 输出 LVDS,但我无法调整 LVDS 输出时钟频率和时序。我需要修改哪些源码,应该怎么修改?需要的时序参数如下:像素时钟 = 54.13 MHz有效分辨率

2023-04-18 09:46:58

BMS 使用 ADI 的 LTC6820 连接到 MC33772C,具有菊花链唤醒功能,但没有唤醒功能。MC33772C上电后进入INIT,等待60S后进入IDLE状态。 通信正常,唤醒时序为6820的CS下拉、上拉、下拉、上拉操作,但没有唤醒。关于在菊花链唤醒中寻找什么的任何建议?

2023-04-17 07:49:25

展频IC在4M时钟上的应用

2023-04-14 10:12:27 0

0 单位宽(Single bit)信号即该信号的位宽为1,通常控制信号居多。对于此类信号,如需跨时钟域可直接使用xpm_cdc_single

2023-04-13 09:11:37 911

911 当设计存在多个时钟时,根据时钟的相位和频率关系,分为同步时钟和异步时钟,这两类要分别讨论其约束

2023-04-06 14:34:28 886

886

我们在ASIC或FPGA系统设计中,常常会遇到需要在多个时钟域下交互传输的问题,时序问题也随着系统越复杂而变得更为严重。

2023-04-06 10:56:35 413

413 形式。储能市场在过去几年里的火爆程度大家也项目共睹。 “光伏+储能”模式里,光伏逆变器和储能变流器是两大核心基础设施。经由这两大核心基础设施如何把大量组件的电量汇集在一起,都依赖于电缆和连接器。光伏连接器和储

2023-04-06 00:32:00 2092

2092

系统时序设计中对时钟信号的要求是非常严格的,因为我们所有的时序计算都是以恒定的时钟信号为基准。但实际中时钟信号往往不可能总是那么完美,会出现抖动(Jitter)和偏移(Skew)问题。

2023-04-04 09:20:56 1633

1633 信号完整性仿真重点分析有关高速信号的3个主要问题:信号质量、串扰和时序。对于信号质量,目标是获取具有明确的边缘,且没有过度过冲和下冲的信号。

2023-04-03 10:40:07 887

887 设置 Input-to-Reg 时序路径的约束时,不仅需要创建时钟模型,还需要设置输入延时 (input delay)。设置 input delay 时,需要假设输入 port 信号是与时钟

2023-03-31 16:39:14 1044

1044

理论上讲,快时钟域的信号总会采集到慢时钟域传输来的信号,如果存在异步可能会导致出现时序问题,所以需要进行同步处理。此类同步处理相对简单,一般采用为延迟打拍法,或延迟采样法。

2023-03-28 13:50:29 1386

1386

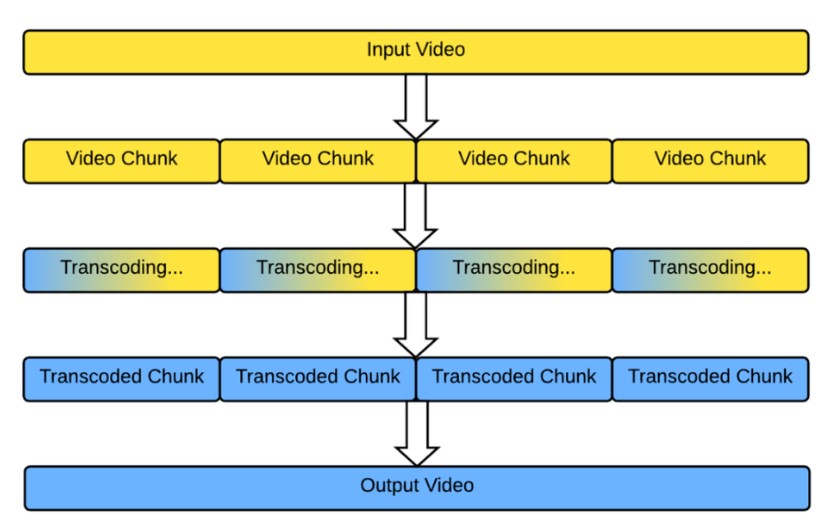

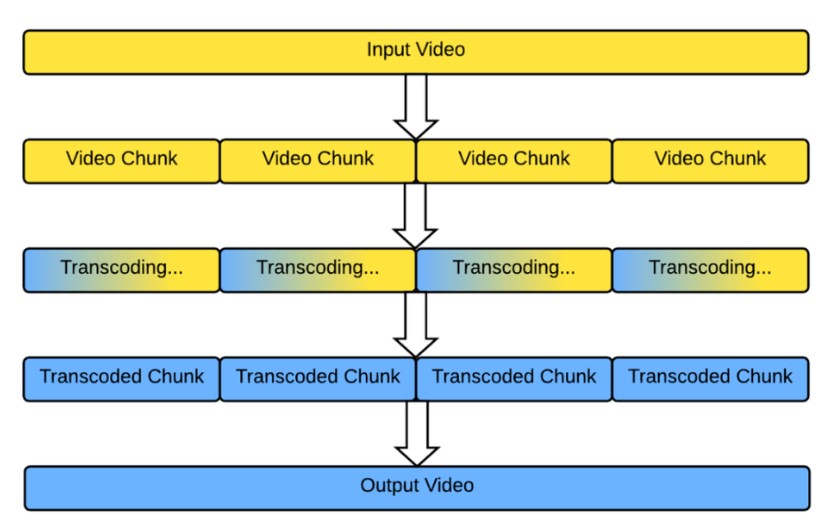

Vimeo发布新转码基础设施Falkor——降低成本的同时将速度推向极限。

2023-03-28 10:55:30 445

445

电子发烧友App

电子发烧友App

评论