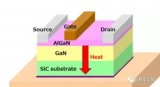

外延工艺是指在衬底上生长完全排列有序的单晶体层的工艺。一般来讲,外延工艺是在单晶衬底上生长一层与原衬底相同晶格取向的晶体层。外延工艺广泛用于半导体制造,如集成电路工业的外延硅片。MOS 晶体管

2023-02-13 14:35:47 10447

10447 在microLED显示器和功率器件的驱动下,外延设备的出货量在未来五年将增长三倍以上。 外延在半导体产业链中的位置 化合物半导体外延片正大举进军超越摩尔领域 据麦姆斯咨询介绍,目前,外延生长用于

2020-01-30 09:58:58 4545

4545 ,热量是不能及时传导,易形成局部高温,进而可能损伤元器件、组件,从而影响系统的可靠性及正常工作周期 。所以慎重选择电源灌封胶非常重要,可以使用有机硅材质的电源灌封胶,因其优良的物理化学性能和工艺性能成为灌

2019-02-27 17:19:23

硅-硅直接键合技术主要应用于SOI、MEMS和大功率器件,按照结构又可以分为两大类:一类是键合衬底材料,包括用于高频、抗辐射和VSIL的SOI衬底和用于大功率高压器件的类外延的疏水键合N+-N-或

2018-11-23 11:05:56

日前,在广州举行的2013年LED外延芯片技术及设备材料最新趋势专场中,晶能光电硅衬底LED研发副总裁孙钱博士向与会者做了题为“硅衬底氮化镓大功率LED的研发及产业化”的报告,与同行一道分享了硅衬底

2014-01-24 16:08:55

本指南提供了有关Arm SystemReady计划和SystemReady预硅启用的常见问题的答案。

信息分为以下几个部分:

•SystemReady一般常见问题解答回答了有关SystemReady

2023-08-08 06:21:04

有被非硅材料逐渐替代的现象,学术研究人员现在开始专注于开发聚合物和纸基微型器件。利用这些材料开发的器件,不仅工艺环保,而且制作设备简单、成本较低。相对硅材料,它们大幅缩减了研发经费预算。许多聚合物和纸基

2016-12-09 17:46:21

恩智浦半导体(NXP Semiconductors),近日推出业界领先的QUBIC4 BiCMOS硅技术,巩固了其在射频领域的领导地位,实现在高频率上提供更优的性能和更高集成度的同时,为客户带来成本

2019-07-12 08:03:23

嗨,我绕了一圈想弄清楚RN4871上如何启用不同的电源模式,以及它们对于设备行为的意义,所以我在下面列出了电源模式的参考资料。特别是,我试图进入最低功率模式,根据数据表绘制1至1.7uA。注意,在

2020-04-17 07:48:38

Verilog设计内外延时

2012-08-15 16:31:14

ch9328的USB端可以外延带屏蔽的标准USB线吗,有线长要求吗?

2022-07-07 06:08:49

各位大侠,小女子在做半导体退火的工艺,不知道哪位做过有n型单晶硅退火?具体参数是什么?任何经验都可以提,请照顾一下新手,谢谢!:handshake

2011-03-01 09:37:32

清洁 - 表面问题:金属污染的起源:来源:设备、工艺、材料和人力,Si表面的过渡金属沉淀是关键。去污:可以对一些暴露于碱或其他金属污染物的基材进行去污。晶片不得含有任何污染薄膜。这通常在硅的 KOH

2021-07-01 09:42:27

书籍:《炬丰科技-半导体工艺》文章:硅纳米柱与金属辅助化学蚀刻的比较编号:JFSJ-21-015作者:炬丰科技网址:http://www.wetsemi.com/index.html摘要

2021-07-06 09:33:58

书籍:《炬丰科技-半导体工艺》文章:CMOS 单元工艺编号:JFSJ-21-027作者:炬丰科技网址:http://www.wetsemi.com/index.html晶圆生产需要三个一般过程:硅

2021-07-06 09:32:40

可控硅是中频电源 的心脏,它的正确使用对中频电源的运行至关重要。一台中频电源一年损坏三五只可控硅尚属正常,如果经常烧硅,电炉停摆,影响生产,就要引起警觉了。可控硅的工作电流从几百安到几千安,电压

2013-10-17 09:37:47

可控硅是中频电源的心脏,它的正确使用对中频电源的运行至关重要。一台中频电源一年损坏三五只可控硅尚属正常,如果经常烧硅,电炉停摆,影响生产,就要引起警觉了。可控硅的工作电流从几百安到几千安,电压通常在

2013-10-14 10:26:02

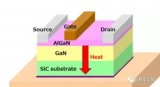

)、氮化镓(GaN)、碳化硅(SiC)、双极硅、绝缘硅(SoI)和蓝宝石硅(SoS)等工艺技术给业界提供了丰富的选择。虽然半导体器件的集成度越来越高,但分立器件同样在用这些工艺制造。随着全球电信网络向

2019-08-02 08:23:59

我想了解关于LED关于外延片生长的结构,谢谢

2013-12-11 12:50:27

与表面驱逐力紧紧粘合材料或蚀刻表面。某种程度来讲,等离子清洗实质上是等离子体刻蚀的一种较轻微的情况。进行干式蚀刻工艺的设备包括反应室、电源、真空部分。工件送入被真空泵抽空的反应室。气体被导入并与等离子体

2018-09-03 09:31:49

)、氮化镓(GaN)、碳化硅(SiC)、双极硅、绝缘硅(SoI)和蓝宝石硅(SoS)等工艺技术给业界提供了丰富的选择。虽然半导体器件的集成度越来越高,但分立器件同样在用这些工艺制造。随着全球电信网络向

2019-07-05 08:13:58

)、氮化镓(GaN)、碳化硅(SiC)、双极硅、绝缘硅(SoI)和蓝宝石硅(SoS)等工艺技术给业界提供了丰富的选择。虽然半导体器件的集成度越来越高,但分立器件同样在用这些工艺制造。随着全球电信网络向长期

2019-08-20 08:01:20

本帖最后由 eehome 于 2013-1-5 09:48 编辑

单晶硅太阳能电池详细工艺

2012-08-06 11:49:37

可控硅电源采用的串联谐振,即电压型谐振频率跟踪。因此效率较高、功率因数较高。所以有明显的节电效果,加热每吨棒料用电341度。 可控硅电源前级不可控全桥整流,不会在整流段引起波形的变形,没有关断角

2014-02-27 11:53:46

通俗的说,可控硅是一个控制电压的器件,由于可控硅的导通角是可以用电路来控制的,固此随着输出电压Uo的大小变化,可控硅的导通角也随着变化。加在主变压器初级的电压Ui也随之变化。

2019-10-16 09:01:04

可控硅中频电源装置简称可控硅中频装置,是利用可控硅的开关特性把50Hz的工频电流变换成中频电流的一种电源装置,主要是在感应熔炼,感应加热,感应淬火等领域中广泛应用。它的优点是:1) 效率高可控硅电源

2013-12-27 09:11:10

梁上在10 000gn加速度作用下压阻元件所受的平均应力,如表2所示。 4 压阻式硅微型加速度传感器加工工艺 压阻式传感器的悬臂梁常采用CVD工艺在硅片上外延生长一层外延层刻蚀而成,文中试用键合

2018-11-01 17:23:05

`工厂直销:13系列,双向可控硅,单向可控硅,稳压电源联系:137-3532-316913系列1300313003D13005D双向可控硅BT136BT137BT151BT139单向可控硅X04052P4M2P6M稳压电源TL43178M057805L7805CVL7808CVL7809CVL7812CV`

2020-04-08 20:19:00

中元器件的介质隔离,彻底消除了体硅CMOS电路中的寄生闩锁效应;采用这种材料制成的集成电路还具有寄生电容小、集成密度高、速度快、工艺简单、短沟道效应小及特别适用于低压低功耗电路等优势,因此可以说SOI

2012-01-12 10:47:00

` 有谁用过SEMILAB的SRP-2000外延片厚度测试仪,关于测试仪的机构和控制部分,尤其是精度部分希望交流,资料可发g-optics@163.com,多谢!`

2018-11-20 20:25:37

问个菜的问题:半导体(或集成电路)工艺 来个人讲讲 半导体工艺 集成电路工艺 硅工艺 CMOS工艺的概念和区别以及联系吧。查了一下:集成电路工艺(integrated

2009-09-16 11:51:34

最近在做一个用晶闸管或者可控硅做电源开关的项目,请问在这个电路里可控硅怎么实现开通和关断?非常感谢!

2017-07-11 22:41:13

几个问题:一是硅的缺陷比较多,它的发光效率比较差。二是用硅做外延成长时,由于硅本身会吸收光线,因此必须把硅拿掉,用别的基材(不管是用金属还是其他基材)来做光源的承载体。这里必须做一个基板的转换,这个工艺本身

2012-03-15 10:20:43

1995年希腊科学家A.G.Nassiopuoulos等人用高分辨率的紫外线照相技术,各向异性的反应离子刻蚀和高温氧化的后处理工艺,首次在硅平面上刻划了尺寸小于20nm的硅柱和 硅线的表面结构,观察到了类似于多孔硅的光激发光现象。

2019-09-26 09:10:15

外延生长法(LPE)外延生长法(epitaxial growth)能生长出和单晶衬底的原子排列同样的单晶薄膜。在双极型集成电路中,为了将衬底和器件区域隔离(电绝缘),在P型衬底上外延生长N型单晶硅层

2019-08-16 11:09:49

表面硅MEMS加工技术是在集成电路平面工艺基础上发展起来的一种MEMS工艺技术,它利用硅平面上不同材料的顺序淀积和选择腐蚀来形成各种微结构。什么是表面硅MEMS加工技术?表面硅MEMS加工技术先在

2018-11-05 15:42:42

我对工艺不是很懂,在氧化层上直接淀积的话是不是非晶硅?如果要单晶硅的话应该怎么做?(有个思路也可以)

2011-06-23 11:06:36

非隔离开关电源方案,怎样负压驱动双向可控硅啊!

2018-07-30 11:48:27

组件可以通过创建和获取电源管理锁来控制功耗编译时可使用CONFIG_PM_ENABLE选项启用电源管理功能电源管理配置(摘自官网)启用电源管理功能将会增加中断延迟。额外延迟与多个因素有关,例如CPU频率

2021-12-27 06:11:35

表面组装技术是以工艺为中心的制造技术。产品种类、功能、性能和品质要求决定工艺,工艺决定设备。不同产品设计要求采用相应的工艺,而不同工艺要求相应的设备。 (1)贴装工艺与设备,如同计算机软件

2018-09-06 10:44:00

两方面: (1)工艺质量 其关键做法在于分清工艺和设备特性和参数。对任何一个产品,首先应该有明确的工艺要求,再从工艺要求中推出什么设备特性参数会影响这些工艺特性,明确如何设置和控制这些设备特性参数

2018-09-07 15:18:04

NPN 硅外延三极管型号

2009-11-12 14:28:41 21

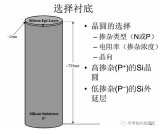

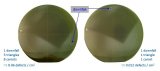

21 硅单晶外延层的质量检测与分析

表征外延层片质量的主要参数是外延层电阻率、厚度、层错及位错密度、少数载流子寿命

2009-03-09 13:55:40 2682

2682

IR收购ATMI硅外延服务部

电源管理技术领先供应商国际整流器公司(International Rectifier,简称IR)宣布收购ATMIInc.(纳斯达克:ATMI)的特殊硅外延服务部。目

2009-07-06 08:45:27 934

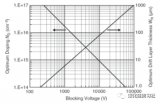

934 ASM启用功新的PowerFill外延技术的电源设备

ASM今天推出了其PowerFill(TM)的外延硅(Epi Si)沟槽填充工艺。新工艺可使带有掺杂物的外延硅深沟无缝隙填充。 PowerFill是一个精

2010-01-23 09:32:32 795

795 采用PowerFill外延硅工艺的电源器件

ASM International推出了其PowerFill的外延硅(Epi Si)沟槽填充工艺。新工艺可使带有掺杂物的外延硅深沟无缝隙填充。 PoweRFill是一个精

2010-01-25 09:17:05 525

525 ASM启用新的PowerFill外延技术的电源设备

ASM International近日推出了其PowerFillTM的外延硅(Epi Si)沟槽填充工艺。新工艺可使带有掺杂物的外延硅深沟无缝隙填充。owerFill是

2010-01-27 08:39:29 1820

1820 国内光伏企业启用零污染节能新工艺

3月24日早间消息,总部设在保定的太阳能公司英利绿色能源宣布,今年扩展400兆瓦产能,将总产

2010-03-24 08:35:08 482

482 本内容介绍了LED外延片基础知识,LED外延片--衬底材料,评价衬底材料必须综合考虑的因素

2012-01-06 15:29:54 2743

2743 济宁高新区联电科技园核心企业冠铨(山东)光电科技有限公司成功研制出4寸LED 外延片,并生产出第一炉。此次研制成功的4寸外延片,每片产出的芯片数量约为2寸工艺的4倍。

2012-11-26 09:25:46 1043

1043 如何启用USB主机到主机设备的API支持Android_英版。

2016-10-12 16:05:10 0

0 对于禁用和启用网卡,找到控制面板的网络设置里面就可以搞定的,但他们偏偏不,就要用批处理实现,好吧,微软的 DevCon 工具就可以命令行禁用或启用网卡,下面是两个批处理的例子。

2017-09-20 14:37:35 5

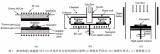

5 一般来说,GaN 的成长须要很高的温度来打断NH3 之N-H 的键解,另外一方面由动力学仿真也得知NH3 和MO Gas 会进行反应产生没有挥发性的副产物。 LED 外延片工艺流程如下: 衬底

2017-10-19 09:42:38 11

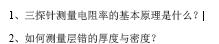

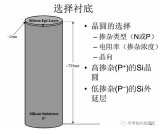

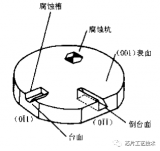

11 CMOS工艺流程介绍1.衬底选择:选择合适的衬底,或者外延片,本流程是带外延的衬底;2. 开始:Pad ox

2018-03-16 10:40:16 108618

108618

LED的波长、亮度、正向电压等主要光电参数基本上取决于外延片材料,因此,外延片材料作为LED工作原理中的核心部分,了解LED外延片技术的发展及工艺非常重要。

2018-11-01 16:41:12 4524

4524 重庆市大足区人民政府官网信息显示,近日,聚力成半导体(重庆)有限公司(以下简称“聚力成半导体”)一期厂房正式启用,计划10月开始外延片的量产,生产线达21条,年产能达12万片。

2019-06-10 16:43:31 4390

4390 晶棒长成以后就可以把它切割成一片一片的,也就是外延片。

2020-04-16 17:08:32 1817

1817 最近做芯片和外延的研究,发现同样的外延工艺和芯片工艺做出来的芯片性能差别很大,大到改变试验设计的“世界观”。基板衬底的质量好坏很关键。

2021-08-12 10:55:58 4302

4302

组件可以通过创建和获取电源管理锁来控制功耗编译时可使用CONFIG_PM_ENABLE选项启用电源管理功能电源管理配置(摘自官网)启用电源管理功能将会增加中断延迟。额外延迟与多个因素有关,例如CPU频率、单/双核模式、是否需要进行频率切换等(CPU 频率为 240 MHz 且未启用频率调节时,最小额外延迟

2022-01-05 14:38:44 3

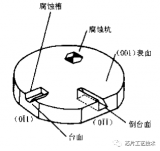

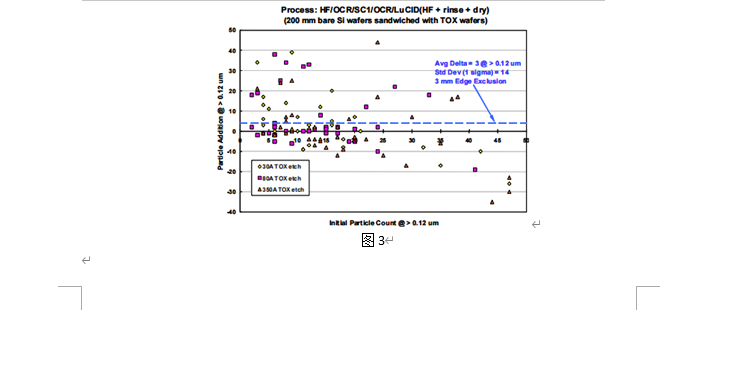

3 本文研究了外延沉积前原位工艺清洗的效果,该过程包括使用溶解的臭氧来去除晶片表面的有机物,此外,该过程是在原位进行的,没有像传统上那样将晶圆从工艺转移到冲洗罐。结果表明,与不使用溶解臭氧作为表面处理

2022-04-12 13:25:49 559

559

CMOS工艺流程介绍,带图片。

n阱的形成 1. 外延生长

2022-07-01 11:23:20 27

27 通过图形化硅氧化或氮化硅掩蔽薄膜生长,可以在掩蔽膜和硅暴露的位置生长外延层。这个过程称为选择性外延生长(SEG)。

2022-09-30 15:00:38 5892

5892 本文聊一下GaN芯片的制备工艺。

GaN-般都是用外延技术制备出来。GaN的外延工艺大家可以看看中村修二的书。

2022-10-19 11:53:40 1459

1459 固相外延,是指固体源在衬底上生长一层单晶层,如离子注入后的热退火实际上就是一种固相外延过程。离于注入加工时,硅片的硅原子受到高能注入离子的轰击

2022-11-09 09:33:52 10250

10250 氮化镓外延片生长工艺较为复杂,多采用两步生长法,需经过高温烘烤、缓冲层生长、重结晶、退火处理等流程。两步生长法通过控制温度,以防止氮化镓外延片因晶格失配或应力而产生翘曲,为目前全球氮化镓外延片主流制备方法。

2023-02-05 14:50:00 4345

4345 氮化镓外延片指采用外延方法,使单晶衬底上生长一层或多层氮化镓薄膜而制成的产品。近年来,在国家政策支持下,我国氮化镓外延片行业规模不断扩大。

2023-02-06 17:14:35 3012

3012 通常是指的在蓝宝石衬底上用外延的方法(MOCVD)生长的GaN。外延片上面一般都已经做有u-GaN,n-GaN,量子阱,p-GaN。

2023-02-12 14:31:25 2100

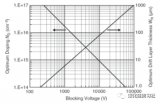

2100 碳化硅(SiC)是制作高温、高频、大功率电子器件的理想电子材料,近20 年来随着外延设备和工艺技术水平不断 提升,外延膜生长速率和品质逐步提高,碳化硅在新能源汽车、光伏产业、高压输配线和智能电站

2023-02-16 10:50:09 6935

6935 氮化镓外延片工艺是一种用于制备氮化镓外延片的工艺,主要包括表面清洗、氮化处理、清洗处理、干燥处理和检测处理等步骤。

2023-02-20 15:50:32 10569

10569 从保障外延片品质入手,提升Micro LED生产效率,降低生产成本外,应用更大尺寸的外延片也是Micro LED成本考量的关键。传统的LED行业普遍在4英寸,而Micro LED的生产工艺会扩大到6乃至8英寸,更大的衬底尺寸可以更好控制Micro LED的成本。

2023-05-10 09:50:04 543

543 在半导体科学技术的发展中,气相外延发挥了重要作用,该技术已广泛用于Si半导体器件和集成电路的工业化生产。

2023-05-19 09:06:46 2467

2467

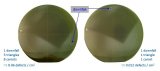

外延层是在晶圆的基础上,经过外延工艺生长出特定单晶薄膜,衬底晶圆和外延薄膜合称外延片。其中在导电型碳化硅衬底上生长碳化硅外延层制得碳化硅同质外延片,可进一步制成肖特基二极管、MOSFET、 IGBT 等功率器件,其中应用最多的是4H-SiC 型衬底。

2023-05-31 09:27:09 2827

2827

如何计算启用4个内核的T4241的功率? 要计算T4241启用4个内核的功率,需要知道以下信息: 1. T4241的额定电源电压和电流 2. T4241启用一个内核的功耗 3. T4241启用四个

2023-06-01 15:12:47 278

278 在SEMICON China 2023上海展上,中国电科集团携集成电路、第三代半导体、半导体显示、光伏及热工等领域设备和工艺整体解决方案重装亮相,全面展示了最新实践和成果。

2023-07-24 10:29:45 797

797 碳化硅功率器件与传统硅功率器件制作工艺不同,不能直接制作在碳化硅单晶材料上,必须在导通型单晶衬底上额外生长高质量的外延材料,并在外延层上制造各类器件。

2023-08-03 11:21:03 286

286

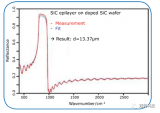

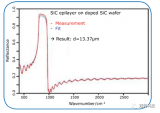

对于掺杂的SiC外延片,红外光谱测量膜厚为通用的行业标准。碳化硅衬底与外延层因掺杂浓度的不同导致两者具有不同的折射率,因此试样的反射光谱会出现反映外延层厚度信息的连续干涉条纹。

2023-08-05 10:31:47 914

914

碳化硅功率器件与传统硅功率器件制作工艺不同,不能直接制作在碳化硅单晶材料上,必须在导通型单晶衬底上额外生长高质量的外延材料,并在外延层上制造各类器件。

2023-08-15 14:43:34 1001

1001

列阵探测器引起了人们的广泛关注。为了满足高性能、双多色红外焦平面器件制备的要求,需要对碲镉汞p型掺杂与激活进行专项研究。使用分子束外延方法直接在碲镉汞工艺中进行掺杂,As很难占据Te位,一般作为间隙原子或者占据金属位,

2023-09-26 09:18:14 284

284

电子发烧友网站提供《LED外延芯片工艺流程及晶片分类.doc》资料免费下载

2023-11-03 09:42:54 0

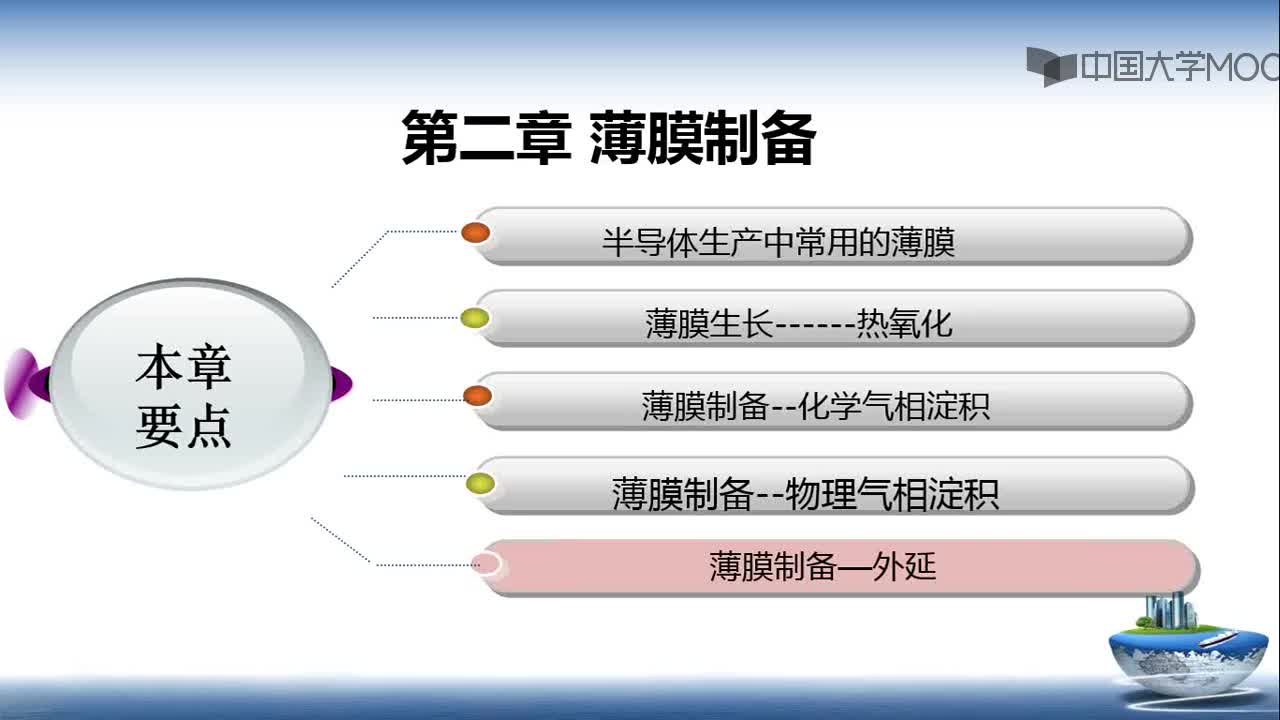

0 外延工艺的介绍,单晶和多晶以及外延生长的方法介绍。

2023-11-30 18:18:16 878

878

碳化硅衬底有诸多缺陷无法直接加工,需要在其上经过外延工艺生长出特定单晶薄膜才能制作芯片晶圆,这层薄膜便是外延层。几乎所有的碳化硅器件均在外延材料上实现,高质量的碳化硅同质外延材料是碳化硅器件研制的基础,外延材料的性能直接决定了碳化硅器件性能的实现。

2023-12-15 09:45:53 607

607

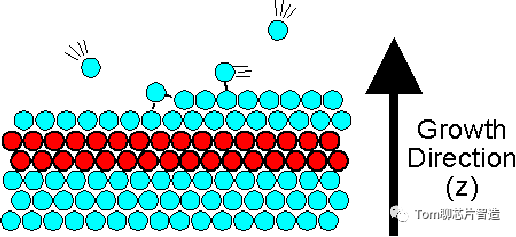

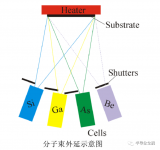

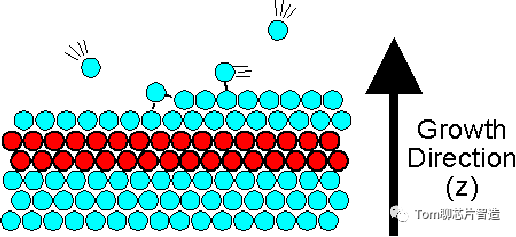

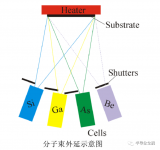

分子束外延(Molecular beam epitaxy,MBE)是一种在超高真空状态下,进行材料外延技术,下图为分子束外延的核心组成,包括受热的衬底和释放到衬底上的多种元素的分子束。

2024-01-15 18:12:10 963

963

预计该项目投资总额3.5亿元人民币,将引进碳化硅外延设备及辅助设备共计116套。其中包括一条具备24万片年产量的6英寸低密度缺陷碳化硅外延材料产线。

2024-02-29 16:24:01 217

217 衬底(substrate)是由半导体单晶材料制造而成的晶圆片,衬底可以直接进入晶圆制造环节生产半导体器件,也可以进行外延工艺加工生产外延片。

2024-03-08 11:07:41 161

161

聚焦碳化硅衬底片和碳化硅外延设备两大业务。公司已掌握行业领先的8英寸碳化硅衬底技术和工艺,量产晶片的核心位错达到行业领先水平。

2024-03-22 09:39:29 65

65

电子发烧友App

电子发烧友App

评论