完善资料让更多小伙伴认识你,还能领取20积分哦,立即完善>

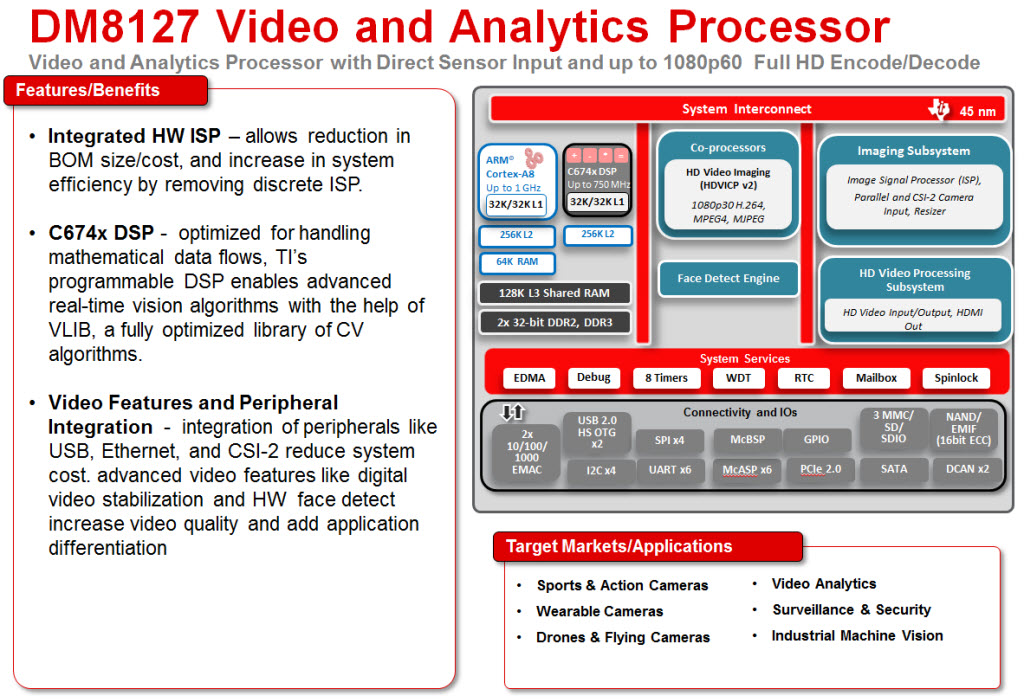

TMS320DM8127达芬奇数字媒体处理器是高度集成的可编程平台,利用该技术满足以下应用的处理需求,仅举几例:IP网络摄像机工业自动化网络摄像机立体摄像机视频监控高清视频会议汽车黑匣子家庭音频和视频设备

该设备使原始设备制造商(OEM)和原始设计制造商(ODM)能够快速推向市场强大的操作系统支持,丰富的用户界面和高处理性能,通过完全集成的混合处理器解决方案的最大灵活性。该器件还将可编程视频和音频处理与高度集成的外设集相结合。

可编程性由具有Neon扩展,TI C674x VLIW浮点DSP内核和高电平的ARM Cortex-A8 RISC CPU提供。定义视频和成像协处理器。 ARM允许开发人员将控制功能与DSP和协处理器上编程的A /V算法分开,从而降低系统软件的复杂性。具有Neon浮点扩展的ARM Cortex-A8 32位RISC内核包括:32KB指令缓存; 32KB的数据缓存; 256KB的L2 Cache; 48KB的Boot ROM;和64KB的RAM。

丰富的外设集可以控制外部外围设备并与外部处理器通信。有关每个外围设备的详细信息,请参阅本文档中的相关章节以及相关的外围设备参考指南。外设集包括:高清视频处理子系统双端口千兆以太网MAC(10/100/1000 Mbps)[以太网交换机],带有MII /RMII /GMII /RGMII和支持IEEE 1588时间戳,AVB和工业以太网协议的MDIO接口2 USB端口,集成2.0 PHY PCIe x1 GEN2兼容接口两个10串行器McASP音频串行端口(带DIT模式)四个四串行器McASP音频串行端口(带DIT模式)一个McBSP多通道缓冲串行端口六个UART,支持IrDA和CIR四个SPI串行接口三个MMC /SD /SDIO串行接口四个 2 C主从接口并行摄像机接口(CAM)多达128个通用I /O(GPIO)八个32位通用定时器系统看门狗定时器双DDR2和DDR3 SDRAM接口灵活的8位或16位异步存储器接口两个控制器局域网(DCAN)模块Spin LockMailbox

TMS320DM8127达芬奇数字媒体处理器还包括一个高清视频和想象g协处理器2(HDVICP2)可以从DSP内核卸载许多视频和图像处理任务,为常见的视频和成像算法提供更多的DSP MIPS。此外,TMS320DM8127达芬奇数字媒体处理器还为ARM和DSP提供了一整套开发工具,包括C编译器,简化编程和调度的DSP汇编优化器,以及用于查看源代码执行情况的Microsoft®Windows™调试器界面。

C674x DSP内核是TMS320C6000 DSP平台中的高性能浮点DSP生成器,与上一代C64x定点和C67x浮点DSP生成代码兼容。 C674x浮点DSP处理器使用32KB的L1程序存储器和EDC以及32KB的L1数据存储器。最多32KB的L1P可配置为程序缓存。剩余内存是不可缓存的无等待状态程序内存。最多可将32KB的L1D配置为数据高速缓存。剩余内存是不可缓存的无等待状态数据内存。 DSP具有256KB带有ECC的L2 RAM,可以定义为SRAM,L2高速缓存或两者的组合。所有C674x L3和片外

| Applications |

| Operating Systems |

| Arm CPU |

| Arm MHz (Max.) |

| DSP |

| DSP MHz |

| Video Acceleration |

| Video Resolution/Frame Rate |

| Video Port (Configurable) |

| USB |

| PCI/PCIe |

| EMAC |

| DRAM |

| SPI |

| I2C |

| UART (SCI) |

| On-Chip L2 Cache/RAM |

| Operating Temperature Range (C) |

| Pin/Package |

| TMS320DM8127 |

|---|

| Machine Vision Industrial Cameras Portable Cameras Video Surveillance IP Cameras |

| 0 |

| 1 ARM Cortex-A8 |

| 1000 |

| 1 C674x |

| 750 |

| 1 HDVICP |

| 1080P 60FPS or less |

| 2 Output 1 Input 2 SD DACs 1 HDMI TX |

| 2 USB2.0 w/phy |

| PCIe x1 GEN2 |

| 10/100/1000 2-port |

| LPDDR DDR2 DDR3 |

| 4 |

| 4 |

| 6 |

| 256 KB |

| -40 to 90 0 to 90 |

| 684FCBGA |