完善资料让更多小伙伴认识你,还能领取20积分哦,立即完善>

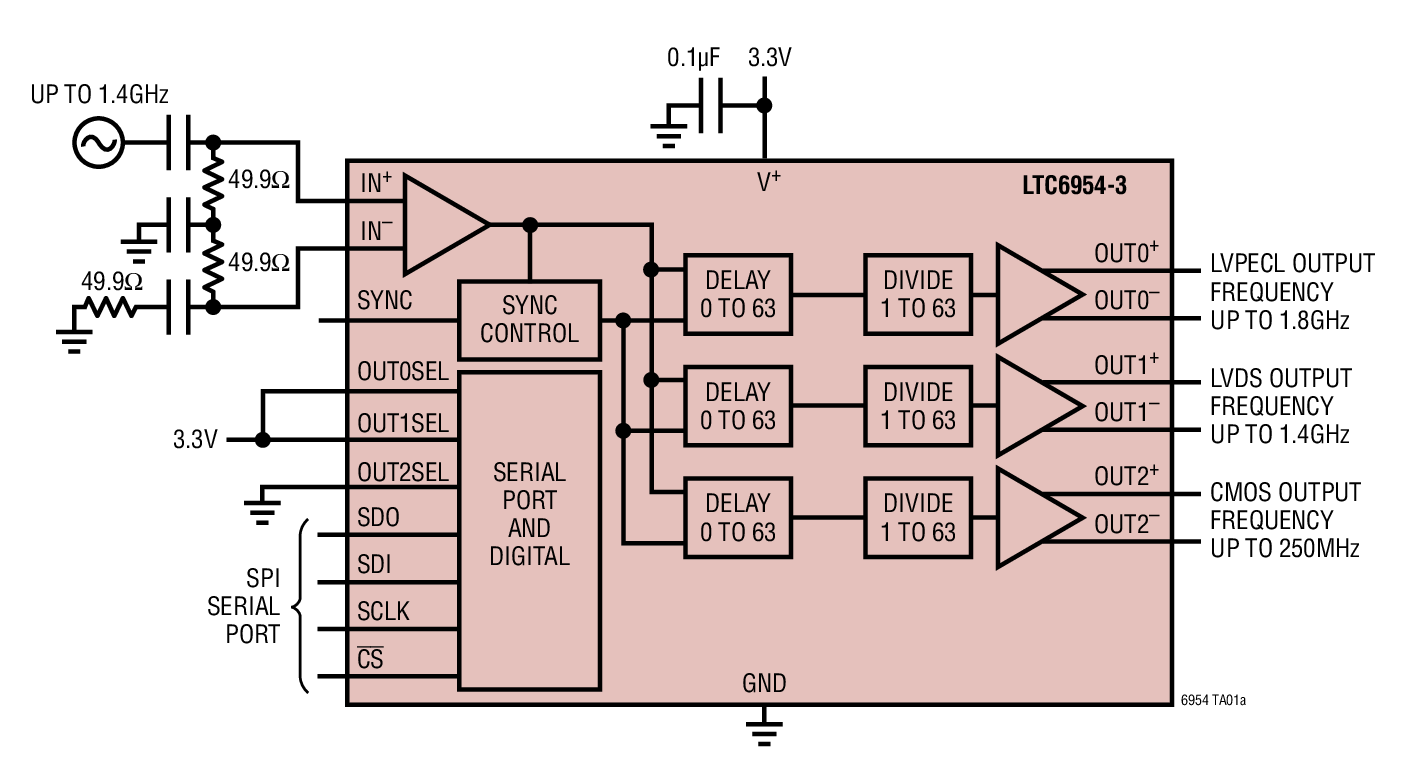

LTC®6954 是一个非常低相位噪声时钟分配器件系列。每款器件具有三个输出,而且每个输出具有一个可个别编程的分频器和延迟。该系列包括以下 4 个具有不同输出逻辑信号类型的成员:

LTC6954-1:三个 LVPECL 输出

LTC6954-2:两个 LVPECL 和一个 LVDS/CMOS 输出

LTC6954-3:一个 LVPECL 和两个 LVDS/CMOS 输出

LTC6954-4:三个 LVDS/CMOS 输出

每个输出可个别地编程以利用从 1 至 63 的任何整数来对输入频率进行分频,并把每个输出延迟 0 至 63 个输入时钟周期。输出占空比始终为 50%,这与分频数无关。LVDS/CMOS 输出可由跳线通过 OUTxSEL 引脚进行选择,以提供一个 LVDS 逻辑输出或一个 CMOS 逻辑输出。

另外,LTC6954 还采用了凌力尔特的 EZSync 系统,以每次都能实现理想的时钟同步和对准。

所有的器件设置均通过一个 SPI 兼容型串行端口来控制。