完善资料让更多小伙伴认识你,还能领取20积分哦,立即完善>

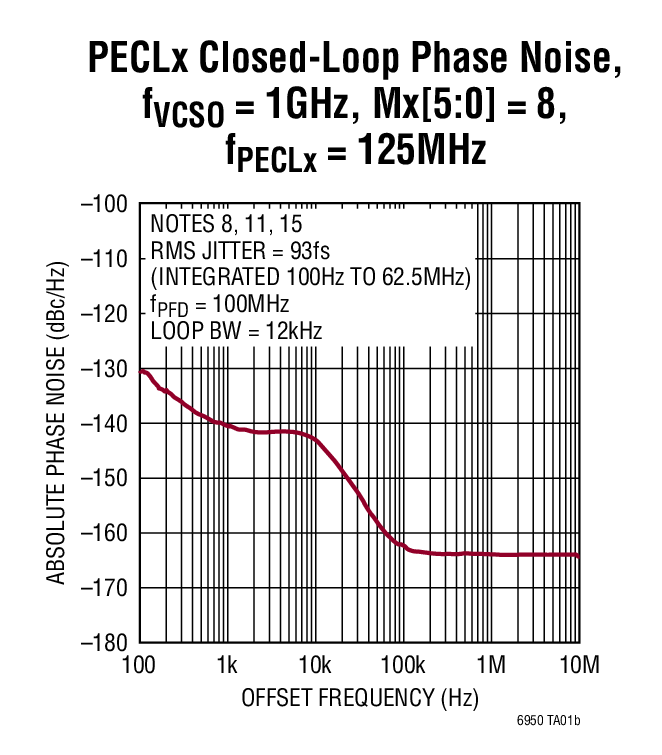

LTC®6950 是一款具时钟分配功能的低相位噪声整数 N 频率合成器内核。LTC6950 可提供高频、高分辨率数据采集系统中所需的低相位噪声时钟信号。

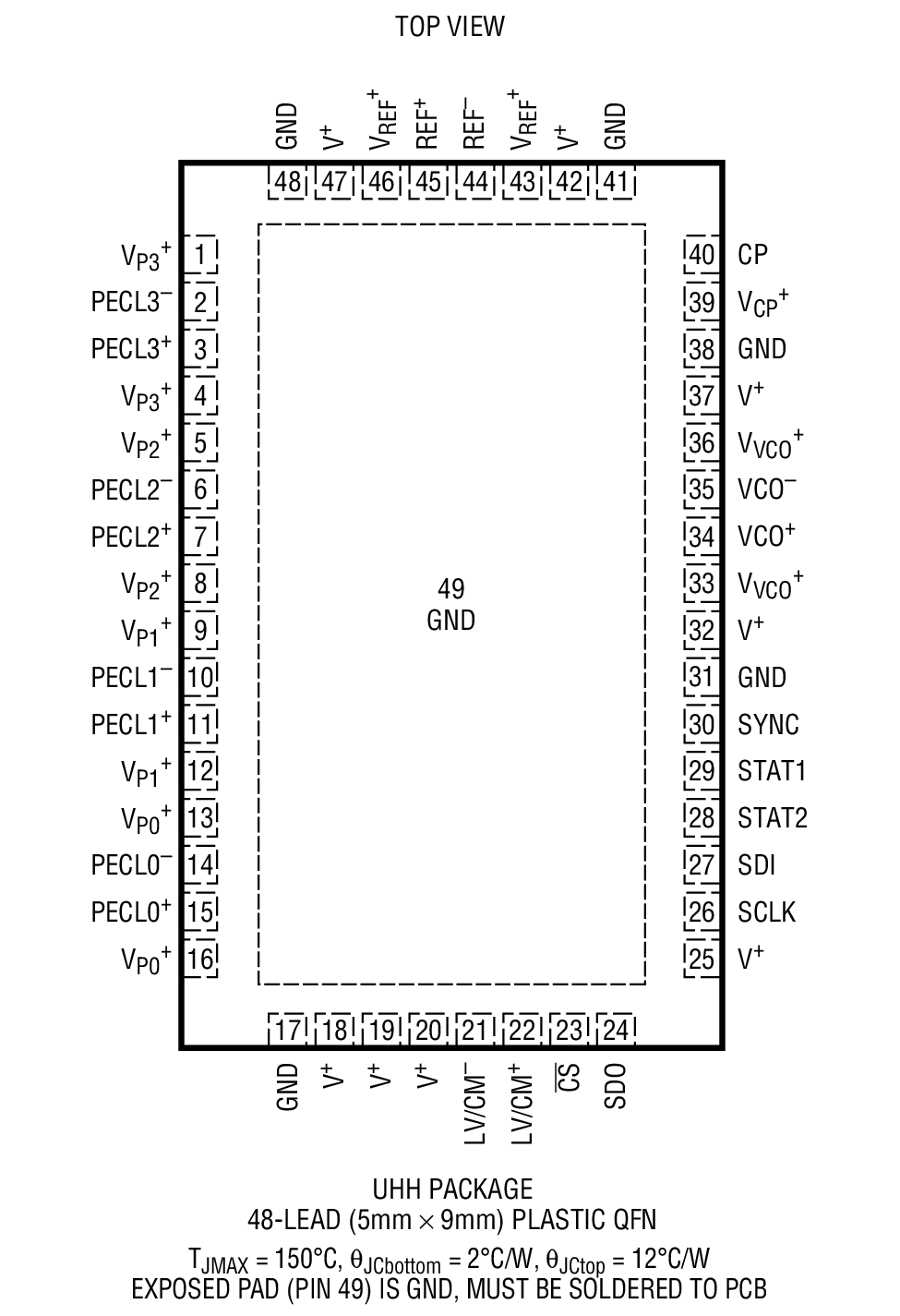

频率合成器包含一个完整的低噪声 PLL 内核,以及一个可编程基准分频器 (R)、一个可编程反馈分频器 (N)、一个相位 / 频率检测器 (PFD) 和一个低噪声充电泵 (CP)。LTC6950 的时钟分配部分提供了多达 5 个基于 VCO 输入的输出。每个输出进行个别编程,以利用从 1 至 63 的任何整数对 VCO 输入频率进行分频,并使输出延迟 0 至 63 个 VCO 时钟周期。其中的 4 个输出具有能够在高达 1.4GHz 频率下运作的非常低噪声、低偏斜 LVPECL 逻辑信号。第 5 个输出可选择为 LVDS (800MHz) 或 CMOS (250MHz) 逻辑类型。另外,还通过编程使该输出产生一个基于 VCO 输入或基准分频器输出的输出信号。