完善资料让更多小伙伴认识你,还能领取20积分哦,立即完善>

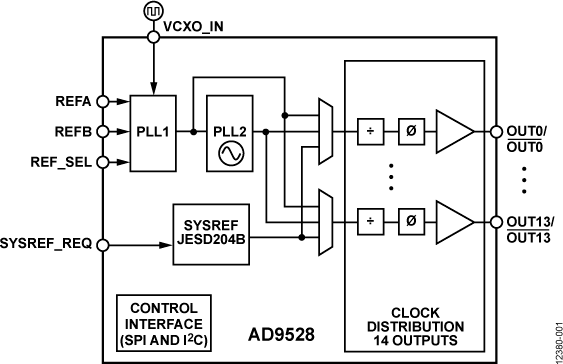

AD9528是一款双级PLL,集成JESD204B SYSREF发生器,可用于多器件同步。第一级锁相环(PLL) (PLL1)通过减少系统时钟的抖动,从而实现输入基准电压调理。第二级PLL (PLL2)提供高频时钟,可实现来自时钟输出驱动器的较低积分抖动以及较低宽带噪声。外部VCXO提供PLL2所需的低噪声基准电压,以满足苛刻的相位噪声和抖动要求,实现可以接受的性能。片内VCO的调谐频率范围为3.450 GHz至4.025 GHz。集成的SYSREF发生器输出单次、N次或连续信号,并与PLL1和PLL2输出同步,以便对齐多个器件的时间。

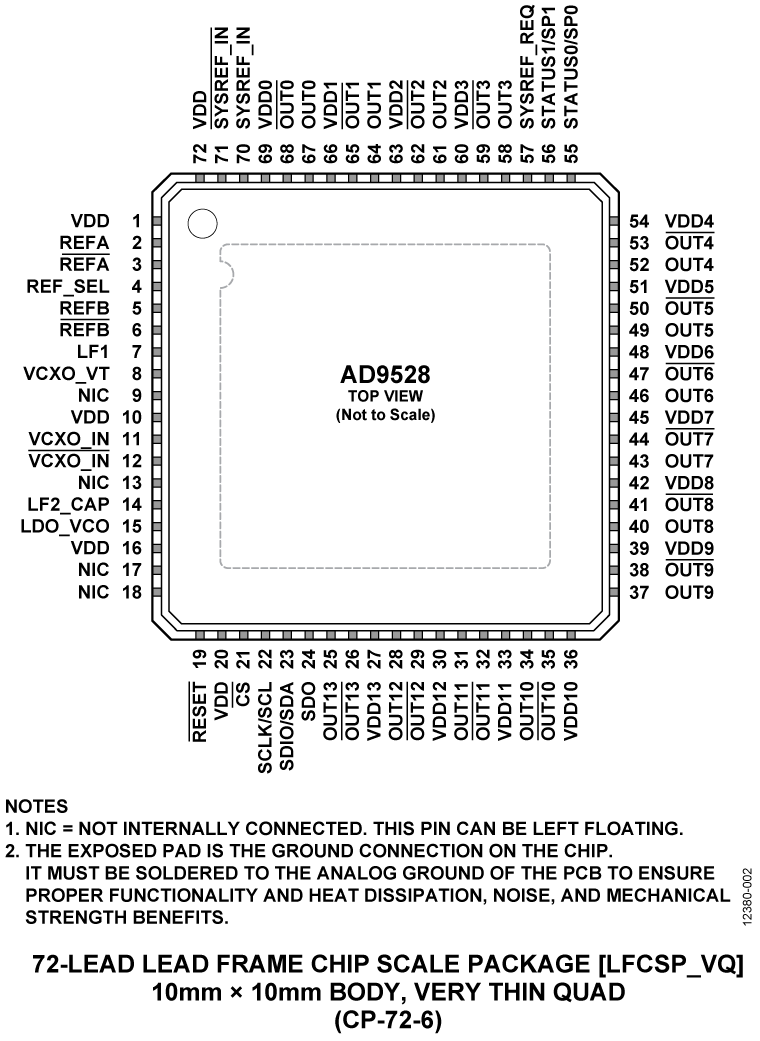

AD9528产生最高频率为1.25 GHz的六路输出(输出0至输出3、输出12和输出13),以及最大频率高达1 GHz的八路输出。每一路输出均可配置为直接从PLL1、PLL2或内部SYSREF发生器输出。14路输出通道的每一路都包含一个带数字相位粗调功能的分频器,以及一个模拟微调相位延迟模块,允许全部14路输出具有时序对齐的高度灵活性。AD9528还可用作灵活的双通道输入缓冲器,以便实现14路器件时钟和/或SYSREF信号的分配。上电时,AD9528直接向输出12和输出13发送VCXO信号,用作上电就绪时钟。