完善资料让更多小伙伴认识你,还能领取20积分哦,立即完善>

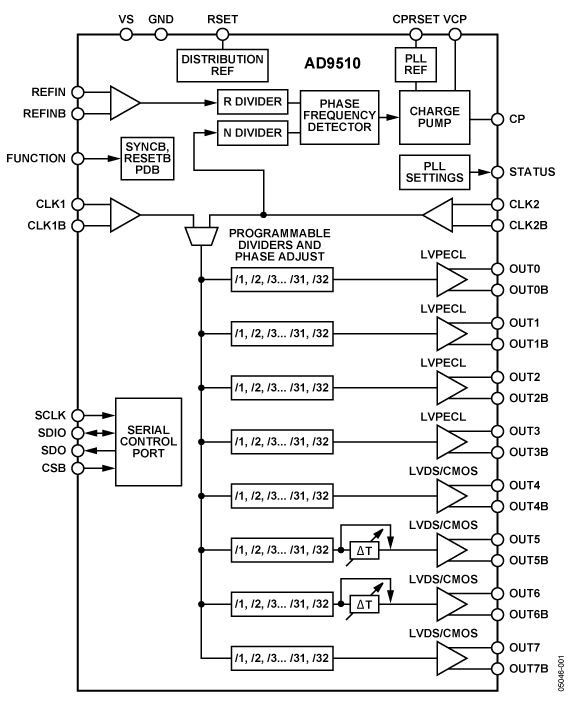

PLL部分由可编程参考分频器(R)、低噪声鉴频鉴相器(PFD)、精密电荷泵(CP)和可编程反馈分频器(N)组成。将外部VCXO或VCO连接到CLK2和CLK2B引脚时,最高达1.6 GHz的PLL输出频率可以与输入参考REFIN同步。

时钟分配部分提供LVPECL输出和可编程为LVDS或CMOS的输出。每路输出都有一个可编程分频器,可以旁路该分频器或者设置最高32的整数分频比。

用户可以通过各分频器改变一路时钟输出相对于其它时钟输出的相位,这种相位选择功能可用于时序粗调。某些输出还提供可编程延迟特性,具有最长10 ns的用户可选满量程延迟值。该精调延迟模块通过一个5位字进行编程,提供32个可用的延迟时间供用户选择。

AD9510非常适合数据转换器时钟应用,利用亚皮秒抖动编码信号,可实现最佳的转换器性能。

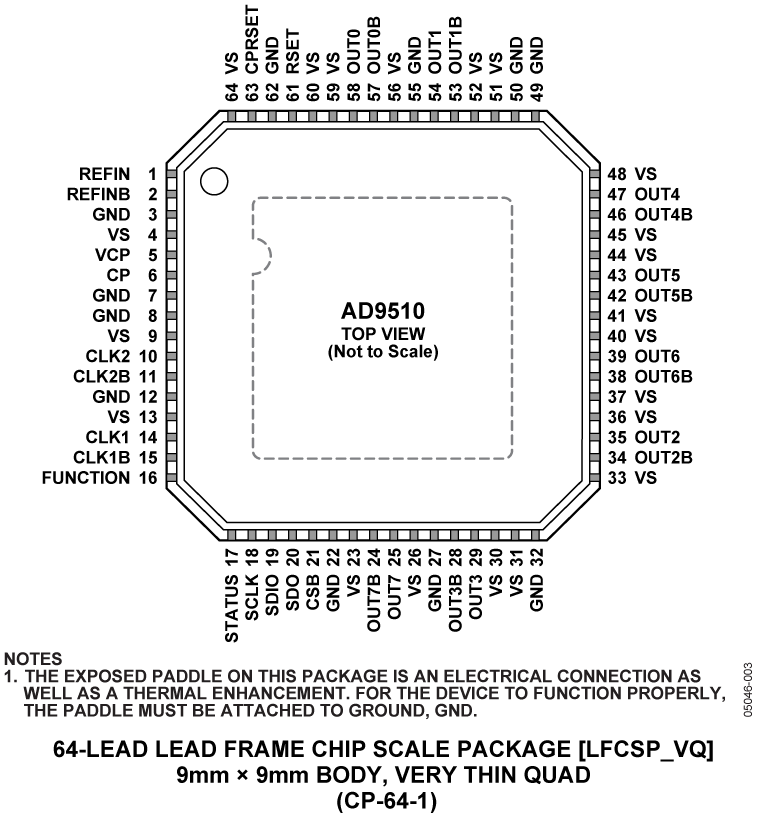

AD9510提供64引脚LFCSP封装,额定温度范围为-40°C至+85°C,可以采用3.3 V单电源供电。如果用户希望扩展外部VCO的电压范围,可以利用最高达5.5V的电荷泵电源VCP。