优势和特点

- 双 DPLL 可同步 1 Hz 到 500 MHz 物理层时钟,可在提供频率转换的同时去除噪声基准电压源的信号抖动

- 符合 ITU-T G.8262 和 Telcordia GR-253 标准

- 支持 Telcordia GR-1244、ITU-T G.812、G.813、G.823、G.824、G.825 和 G.8273.2

- 针对低至 50 ppb 的频率偏移可进行持续频率监控和基准电压源验证

- 两个 DPLL 都配有带有 24 位可编程模块的 24 位小数分频器

- 可编程数字环路滤波器带宽:10-4 至 1850 Hz

- 两个独立的可编程辅助 NCO(1 Hz 至 65,535 Hz,分辨率 < 1.4 × 10−12 Hz),适合 PTP 应用中的 IEEE-1588 第 2 版伺服反馈

- 自动和手动保持和基准电压源切换,实现零延迟、无中断或相位增建

- 基于可编程优先级的基准电压源切换,支持手动、自动可逆和自动不可逆模式

- 5 对时钟输出引脚,每对都可用作差分 LVDS/HCSL/CML 或者两个单端输出(1 Hz 至 500 MHz)

- 2 个差分或 4 个单端输入基准电压源

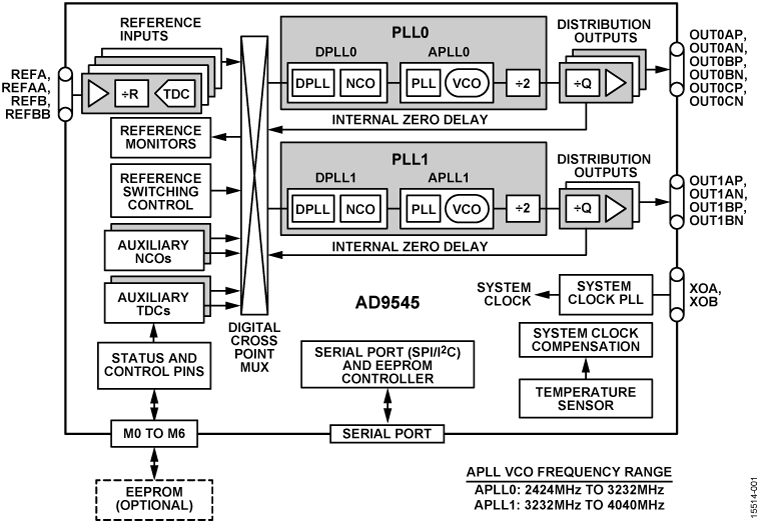

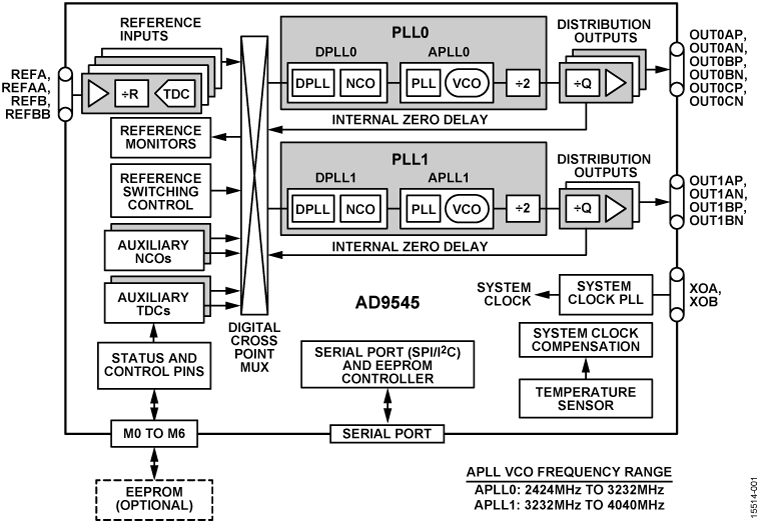

- 交叉点多路复用器将基准输入与 PLL 互连

- 支持嵌入(模块化)输入/输出时钟信号

- 快速 DPLL 时钟模式

- 支持 25 MHz 至 52 MHz 晶体谐振器、TCXO 或 OCXO 作为系统时钟,提供系统时钟频率稳定性补偿

- 自动初始化的外部 EEPROM 支持

- 1.8 V 单电源供电,带有内部调节功能

- 内置温度监控器/警报和温度补偿,可增强零延迟性能

产品详情

AD9545 支持针对在服务提供商包交换网络上提供频率、相位和当日时间的现有和新兴 ITU 标准。

将 AD9545 的 10 个时钟输出同步为多达四个输入基准电压源中的任意一个。数字锁相环 (PLL) 可减少与外部基准电压源相关的定时抖动。数字控制的环和保持电路即使在所有基准输入失败时仍可持续产生低抖动输出信号。

AD9545 提供 48 引脚 LFCSP (7 mm × 7 mm) 封装,可在 −40°C 至 +85°C 的温度范围内工作。

应用

- GPS、PTP (IEEE-1588) 以及 SyncE 去除信号抖动和同步

- 光传送网络 (OTN)、SDH、运营商级以太网以及宏和小蜂窝基站。

- 带有去除信号抖动功能的 OTN 映射/解映射

- 小基站时钟,包括基带和无线电

- Stratum 2、Stratum 3e 和 Stratum 3 保持、去除信号抖动和相位瞬态控制

- JESD204B 支持模数转换器 (ADC) 和数模转换器 (DAC) 时钟

- 线缆基础设施

- 运营商级以太网

方框图