完善资料让更多小伙伴认识你,还能领取20积分哦,立即完善>

LTC®2273/LTC2272 是 80Msps/65Msps、16 位 A/D 转换器,具有一个高速串行接口。它们专为对具有一个 700MHz 输入带宽的高频、宽动态范围信号进行数字化处理而设计。该 ADC 的输入范围可以采用 PGA 前端进行优化。根据用于数据转换器的 JEDEC 串行接口规范 (JESD204) 对输出数据进行串行化处理。

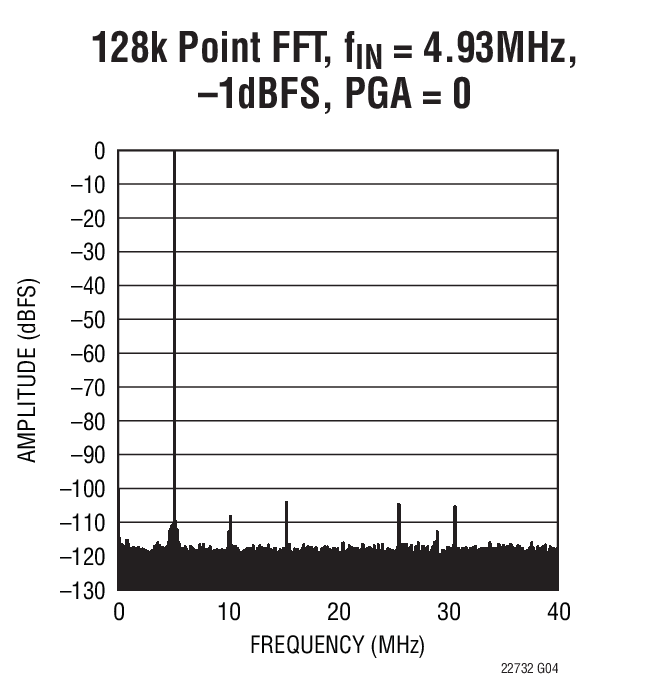

LTC2273/LTC2272 非常适合于那些希望把敏感的模拟电路与噪声数字逻辑电路隔离开来的苛刻应用。其 AC 性能包括 77.7dB 噪声层和 100dB 无寄生动态范围 (SFDR)。80fs RMS 的超低内部抖动实现了高输入频率的欠采样和卓越的噪声性能。最大 DC 规格包括在整个温度范围内的 ±4.5LSB INL 和 ±1LSB DNL (无漏失码)。

可以利用一个正弦波、PECL、LVDS、TTL 或 CMOS 输入对编码时钟输入、ENC+ 和ENC– 进行差分或单端驱动。一个时钟占空比稳定器在全速和各种时钟占空比条件下实现了高性能。