完善资料让更多小伙伴认识你,还能领取20积分哦,立即完善>

ADRF6601是一款高动态范围有源混频器,集成锁相环(PLL)和压控振荡器(VCO)。PLL/频率合成器利用小数N分频PLL产生fLO输入,供给混频器。基准输入可以进行分频或倍频,然后施加于PLL鉴频鉴相器(PFD)。

PLL支持12 MHz至160 MHz范围内的输入基准频率。PFD输出控制一个电荷泵,其输出驱动一个片外环路滤波器。

然后,环路滤波器输出施加于一个集成式VCO。VCO输出(2 × fLO)再施加于一个LO分频器和一个可编程PLL分频器。可编程PLL分频器由一个Σ-Δ调制器(SDM)进行控制。SDM的模数可以在1至2047范围内编程。

有源混频器可将单端50 Ω RF输入转换为200 Ω差分IF输出。IF输出的工作频率最高可达500 MHz。

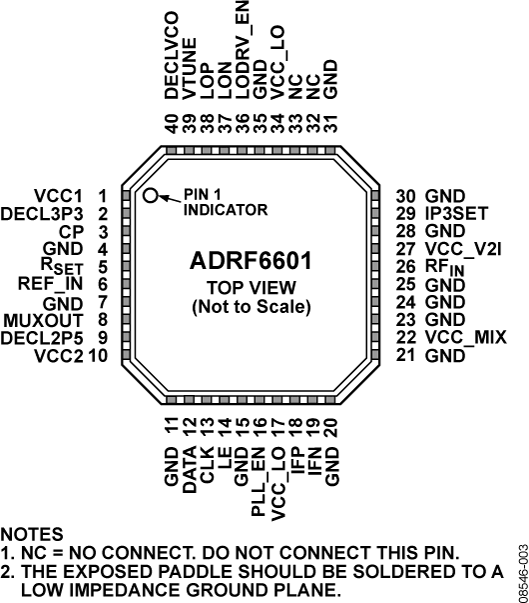

ADRF6601采用先进的硅锗BiCMOS工艺制造,提供40引脚、裸露焊盘、符合RoHS标准的6 mm x 6 mm LFCSP封装。额定温度范围为−40°C至+85°C。

应用