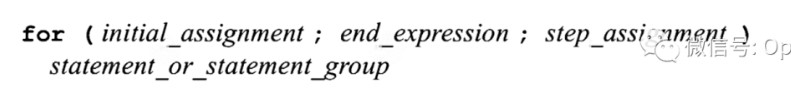

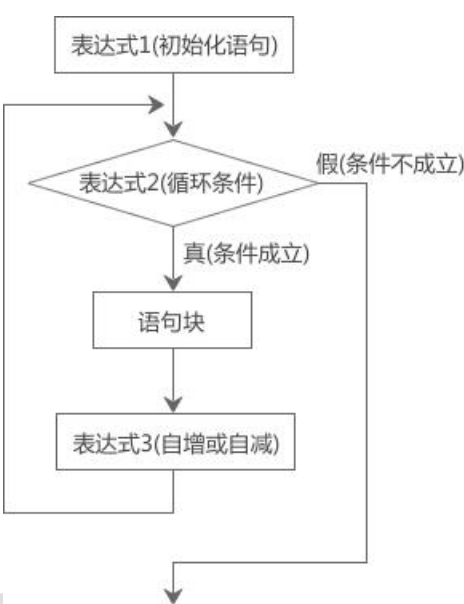

循环语句允许多次执行编程语句或begin-end语句组。SystemVerilog中的循环语句有:for、repeat、while、do..while、foreach和forever。

2022-11-03 09:10:33 1354

1354

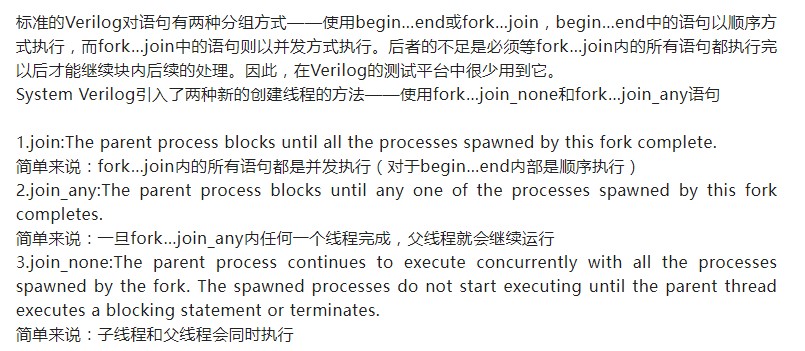

C语言基础知识(5)--循环语句

2023-06-15 10:18:54 1275

1275

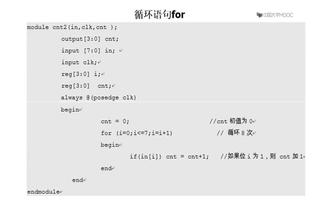

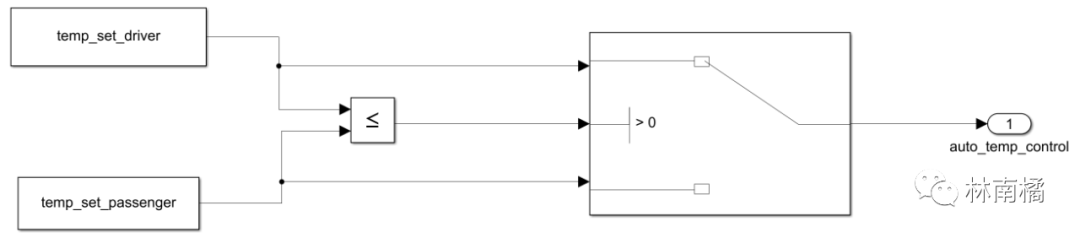

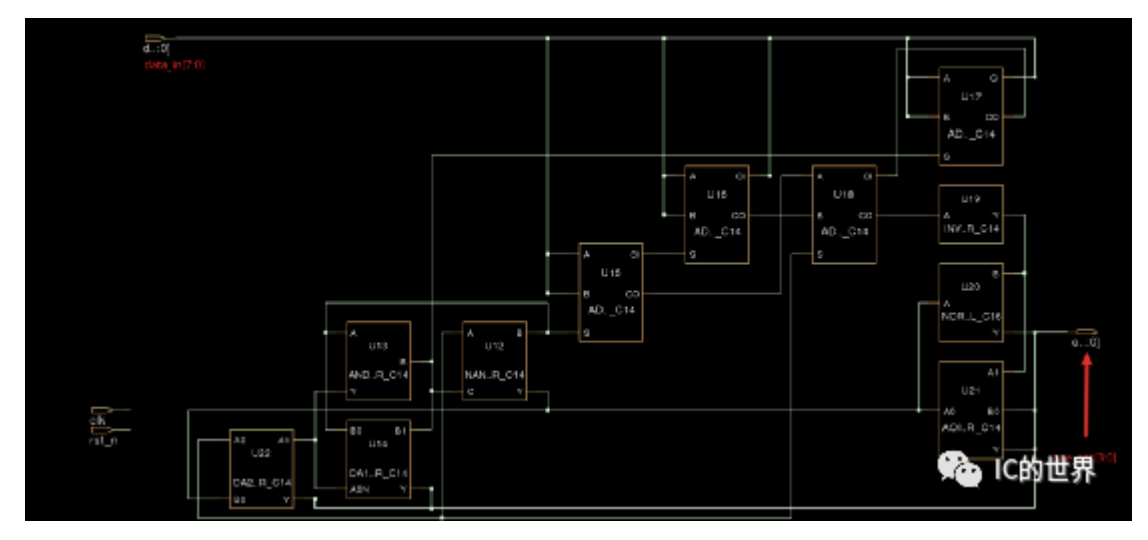

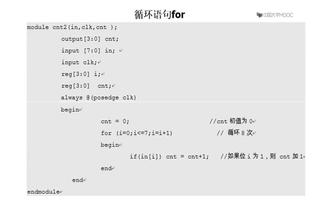

利用for循环实现对信号的赋值。

2023-08-03 10:22:27 1482

1482 在C语言中,break语句是一种控制流语句,它用于终止当前所在的循环结构(for、while、do-while)或者switch语句,从而跳出循环或者结束switch语句的执行。

2023-08-17 15:35:46 917

917 FOR循环语句应用比较广泛,在机器人编程、PLC编程、C语言编程中都有应用。能读懂这些程序语句,可以更好地理解机电设备控制原理,为机电设备安装维修工作带来便利。

2023-09-25 17:14:51 2516

2516

首先,考虑x和z在verilog条件语句中的使用情况,然后我们再考虑在verilog中用x和z给其他reg/wire赋值的情况。

2023-11-02 09:40:10 478

478

,不同的模拟选项导致开始模拟时现象不同建议: 在0时刻通过非阻塞赋值设置reset信号;第一个半周期设置clock为0编写Verilog代 码的一些经验:Verilog文件名和模块名相同不要在可综合代码

2019-03-26 08:00:00

1.Verilog 中generate if语句如何用systemc实现?例如:generateif (SIZE < 8)assign y = a & b & c;else

2014-08-29 16:11:21

Verilog可综合子集

2013-04-01 12:44:46

Verilog 中generate if语句如何用systemc实现?例如:generateif (SIZE < 8)assign y = a & b & c;else

2014-08-28 12:06:43

Verilog中的always块内的语句执行的速度是什么样的,如果always块是时钟上升沿触发的,会不会块内语句还未执行完,而下一个时钟上升沿又来了???

2015-10-29 22:30:43

以前很少用for语句,以为是不可综合的。在印象中好像只用循环生成(for...generate)语句综合过多个模块。最近在仔细研读《轻松成为设计高手——Verilog HDL使用精解》这本书,才知道

2014-08-13 14:59:34

在书上看到,“for循环更多的表示为根据循环次数来复制一个电路”。那么我现在有一个问题,for循环的次数是一个input型的参数(位宽已知,具体是多少是由输入决定的)。这样可以被综合吗?

2018-08-22 13:22:20

1,在一个verilog程序里,如果循环是一个循环次数不可定的循环,那么它能被综合工具综合吗2,如果程序里有always @(clock)里面又嵌套了@(clock)这样的控制事件,这个能被综合吗

2015-02-03 15:29:11

。 建立可综合模型的原则 要保证Verilog HDL赋值语句的可综合性,在建模时应注意以下要点: (1)不使用初始化语句。 (2)不使用带有延时的描述。 (3)不使用循环次数不确定的循环语句,如

2012-10-20 08:10:13

,若不是,则只能用于仿真),while, 建立可综合模型的原则 要保证Verilog HDL赋值语句的可综合性,在建模时应注意以下要点: (1)不使用initial。 (2)不使用#10。 (3)不使

2015-01-05 19:42:44

,arrays,memories,repeat,task,while。建立可综合模型的原则 要保证Verilog HDL赋值语句的可综合性,在建模时应注意以下要点: (1)不使用initial。 (2)不使

2012-02-27 15:01:27

,使用生成语句能大大简化程序的编写过程。Verilog-2001添加了generate循环,允许产生module和primitive的多个实例化,generate语句的最主要功能就是对module、reg

2020-12-23 16:59:15

各位大神,我在学习verilog的过程中遇到一个问题,如图中代码,后面3个@(...)是什么意思?有什么作用?为什么我用Xilinx的综合工具不能综合?请大神们指教!(真诚脸

2017-08-14 12:06:47

考虑清楚了。可以看着图直接写code。 要知道,最初Verilog是为了实现仿真而发明的.不可综合的Verilog语句也是很重要的.因为在实际设计电路时,除了要实现一个可综合的module外,你还要

2017-04-05 20:34:43

verilog的仿真和综合有什么区别,请具体一点?

2018-06-06 22:41:18

verilog设计练习进。我们可以先理解样板模块中每一条语句的作用,然后对样板模块进行综合前和综合后仿真,再独立完成每一阶段规定的练习。当十个阶段的练习做完后,便可以开始设计一些简单的逻辑电路和系统

2012-08-15 16:29:30

可综合的Verilog语法和语义(剑桥大学,影印)

2012-08-06 13:03:57

For循环是任何HDL语言中最让人容易误解的代码之一。For循环可以以可综合与不可综合两种版本实现。不过C语言中的For循环与HDL众的For循环不太一样,要想熟练运用的话就得先理解它。将软件编程

2019-08-07 05:00:00

可综合的语法子集3本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt(1) 多语句定义:begin…end

2015-06-17 11:53:27

类似C的环路结构如for-loop可能对学过C语言的人存在陷阱。其原因是在硬件语言中并没有隐含的寄存器这个条件,所以一般这些环路不可以在可综合代码中用来做算法迭代。在Verilog中,for循环一般

2018-08-08 11:02:25

一:基本Verilog中的变量有线网类型和寄存器类型。线网型变量综合成wire,而寄存器可能综合成WIRE,锁存器和触发器。二:verilog语句结构到门级的映射1、连续性赋值:assign连续性

2012-02-24 10:37:21

,都有Xilinx公司自己写好的可综合的模块,想请教一下为什么要分成这样两项?它们里面的模块有区别吗?2、上述谈到的可综合模块和ISE 自带的IP core又有什么区别呢?

2013-09-28 18:17:54

chisel 中可以用Verilog 语句吗 ?

2022-03-11 14:23:16

Verilog HDL 在执行语句时分为顺序和并行两种方式。在顺序语句块中,语句按给定次序顺序执行;在并行语句块中,语句并行执行。顺序语句块的语法和实例如下:begin[:block_id

2018-09-25 09:22:19

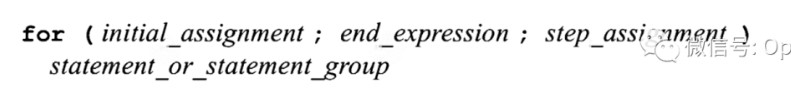

流程控制语句包括:• if 语句;• case 语句;• 循环语句。if 语句的语法如下:if(condition_1)procedural_statement_1{else

2018-09-26 09:21:53

本帖最后由 630183258 于 2016-11-4 13:41 编辑

关于阻塞:计算RHS并更新LHS,此时不能允许有来自任何其他Verilog语句的干扰。 所谓阻塞的概念是指在同一个

2016-11-03 20:26:38

HDL操作数和操作符4.Verilog HDL和VHDL语言的对比5.Verilog HDL循环语句6.Verilog HDL程序的基本结构7.Verilog HDL语言的数据类型和运算符

2018-09-19 11:34:03

do{..........} while(1) 和for(;;)[..............]这两个语句都代表死循环吧都是一样的意思吧!

2018-09-26 17:37:01

大多是可综合的。Verilog中绝大多数运算操作符都是可综合的,其列表如下:+// 加-// 减!// 逻辑非~// 取反&// 与~&// 与非|// 或~|// 或非

2017-12-19 21:36:24

1、不使用初始化语句;2、不使用延时语句;3、不使用循环次数不确定的语句,如:forever,while等;4、尽量采用同步方式设计电路;5、尽量采用行为语句完成设计;6、always过程块描述组合

2021-07-29 06:10:04

我在verilog中尝试了for循环中的模块实例化...我需要在特定条件到达时停止执行循环。任何人请告诉我如何阻止它。

2019-10-25 09:38:11

verilog 中的 generate for 语句好理解,但是 generate if 和 generate case 语句怎么理解??

2014-12-21 12:44:21

在循环中嵌入定时语句,比如"always @ posedge clk" 能不能被综合呢,为什么书上的说可以,但是在quatus里面却提示不能,是不是不同的综合工具对这种综合的支持还不一样

2015-02-02 19:39:40

采用列表框选择 1 2 3 然后 条件语句相应会有反应。问题: 打算点击每个while的stop然后退出此while,然后选择列表框另一选项,相应的另一while循环动作。

2016-02-16 12:30:01

在本篇里,我们讨论 Verilog 语言的综合问题,Verilog HDL (Hardware Description Language) 中文名为硬件描述语言,而不是硬件设计语言。这个名称提醒我们

2021-07-29 07:42:25

Verilog HDL 综合实用教程第1章 基础知识第2章 从Verilog结构到逻辑门第3章 建模示例第4章 模型的优化第5章 验证附录A 可综合的语言结构附录B 通用库

2009-07-20 11:21:13 86

86 switch/case开关语句是一种多分支选择语句,是用来实现多方向条件分支的语句。虽然从理论上讲采用条件语句也可以实现多方向条件分支,但是当分支较多时会使条件语句的嵌套层

2010-07-15 14:26:00 18

18 单片机c语言教程第十三课 C51循环语句

循环语句是几乎每个程序都会用到的,它的作用就是用来实现需要反复进行多次的操 作。如一个 12M 的 51 芯片应用电路中要求

2009-04-15 09:42:25 1629

1629 if语句和while循环

C语言中,if语句和while循环都会用到布尔表达式。下面是一个使用if语句的简单例子:

#include

2009-07-29 10:48:32 8304

8304 电子发烧友网站提供《Verilog HDL数字设计与综合(第二版).txt》资料免费下载

2012-04-04 15:57:24 0

0 可综合的Verilog语法和语义(剑桥大学,影印):第七版

2012-05-21 14:50:14 27

27 电子发烧友网站提供《Verilog HDL_数字设计与综合第二版.txt》资料免费下载

2012-08-07 15:17:15 0

0 电子发烧友网站提供《Verilog_HDL数字设计与综合_夏宇闻译(第二版).txt》资料免费下载

2013-01-23 12:45:01 0

0 电子发烧友网站提供《夏宇闻译(第二版)-Verilog HDL数字设计与综合.txt》资料免费下载

2014-09-17 00:08:46 0

0 电子发烧友网站提供《详解Verilog HDL数字设计与综合 夏宇闻译(第二版).txt》资料免费下载

2014-09-25 22:19:09 0

0 电子发烧友网站提供《Verilog HDL数字设计与综合_夏宇闻译(第二版).txt》资料免费下载

2015-09-08 17:43:22 0

0 介绍Verilog HDL数字设计与综合的课件

2015-12-23 10:58:54 0

0 C++语言基础讲解视频do while循环语句

2016-01-14 15:32:08 5

5 C++语言基础讲解视频while循环语句,喜欢的朋友可以下载来学习。

2016-01-14 15:31:45 3

3 通过本章十个阶段的练习,一定能逐步掌握Verilog HDL 设计的要点。我们可以先理解样板模块中每一条语句的作用,然后对样板模块进行综合前和综合后仿真,再独立完成每一阶段规定的练习。

2016-06-08 14:10:53 11

11 Verilog HDL数字设计与综合 夏宇闻译(第二版),感兴趣的小伙伴们可以瞧一瞧。

2016-11-11 11:20:11 0

0 在很多地方都能看到,verilog中if与case语句必须完整,即if要加上else,case后要加上default语句,以防止锁存器的发生,下载内容中就谈到了其中原因。

2017-09-16 09:29:03 24

24 循环语句是几乎每个程序都会用到的,它的作用就是用来实现需要反复进行多次的操 作。如一个 12M 的 51 芯片应用电路中要求实现 1 毫秒的延时,那么就要执行 1000 次空语句 才能达到延时的目的

2017-11-22 12:43:01 866

866 本文档的主要内容详细介绍的是Java的循环语句的详细资料说明包括了:1、while循环语句,2、do…while循环语句,3、for循环语句

2019-03-22 08:00:00 0

0 在接触Verilog 语法参考手册的时候,我们发现其提供了一组非常丰富的功能来描述硬件。所以大家往往会疑惑那些Verilog语句是可综合的,那些是只能用于写Testbench的,其实,参考手册中只有

2019-04-20 10:59:39 4022

4022 本文档的主要内容详细介绍的是FPGA视频教程之Verilog中两种不同的赋值语句的资料说明免费下载。

2019-03-27 10:55:59 6

6 1、在许多实际问题中,需要程序进行有规律的重复执行,这时可以用循环语句来实现。在c语言中。用来实现循环的语句有for语句,while语句,do-while语句,goto语句等。

2019-08-20 17:31:00 1

1 关于Verilog HDL综合的讨论早在1988年就已经展开。但时至今日,此领域的优秀教材尚未囊括其基本概念。这本关于Verilog HDL综合实用教程全面地介绍了这一新技术。它通过提供便于理解

2019-05-13 08:00:00 74

74 本课程以目前流行的Xilinx 7系列FPGA的开发为主线,全面讲解FPGA的原理及电路设计、Verilog HDL语言及VIVADO的应用,并循序渐进地从组合逻辑、时序逻辑的开发开始,深入到FPGA的基础应用、综合应用和进阶应用。

2019-12-03 07:08:00 2366

2366

可综合设计的特点:1、不使用初始化语句。2、不使用带有延时的描述。3、不使用循环次数不确定的循环语句,如: forever 、while 等。4、尽量采用同步方式设计电路。5、除非是关键路径的设计,一般不调用门级元件来描述设计的方法,建议采用行为语句来完成设计。

2019-08-01 16:55:54 11

11 本文档的主要内容详细介绍的是Verilog教程之Verilog HDL程序设计语句和描述方式。

2020-12-09 11:24:23 46

46 1、如何使用Verilog HDL描述可综合电路 Verilog 有什么奇技淫巧?我想最重要的是理解其硬件特性。Verilog HDL语言仅是对已知硬件电路的文本描述。所以编写前: 对所需实现的硬件

2021-04-04 11:19:00 3838

3838

条件语句的可综合性 HDL语言的条件语句与算法语言的条件语句,最大的差异在于: 1.不管条件:当前输入条件没有对应的描述,则该条件为不管条件(Don’t Care)。对应不管条件的信号称为不管信号

2021-05-12 09:12:22 1558

1558

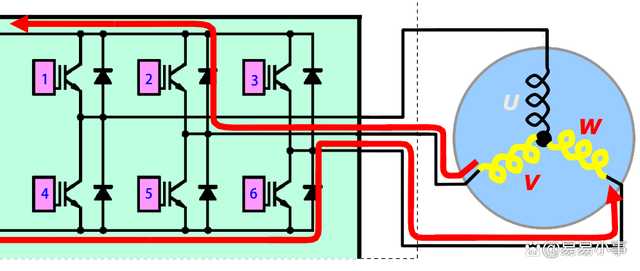

(含循环体)组成的代码块,EDA称为循环框架(Loop Frame)。 在这里,HDL循环语句与算法语言的循环语句的差异: 1.HDL的循环变量i是以常量进入循环体。算法语言则是以变量进入循环体。 2.HDL的循环体并不被循环执行,而是被重复描述(多次重复综合),从而实现建

2021-05-12 09:27:48 1830

1830

解释verilog HDL中的initial语句的用法。

2021-05-31 09:11:33 0

0 1. 块语句有两种,一种是 begin-end 语句, 通常用来标志()执行的语句;一种是 fork-join 语句,通常用来标志()执行的语句。 答案:顺序,并行 解析: (1)begin_end

2021-06-18 15:16:49 2741

2741 在Verilog中有两种类型的赋值语句:阻塞赋值语句(“=”)和非阻塞赋值语句(“=”)。正确地使用这两种赋值语句对于Verilog的设计和仿真非常重要。 Verilog语言中讲的阻塞赋值

2021-12-02 18:24:36 5005

5005

“ 本文主要分享了在Verilog设计过程中一些经验与知识点,主要包括循环语句(forever、repeat、while和for)、运算符。”

2022-03-15 11:41:58 4027

4027 begin_end顺序块,用于将多条语句组成顺序块,语句按顺序一条一条执行(除了带有内嵌延迟控制的非阻塞赋值语句),每条语句的延迟时间是相对于由上一条语句的仿真时间而言;

2022-05-18 10:29:25 1085

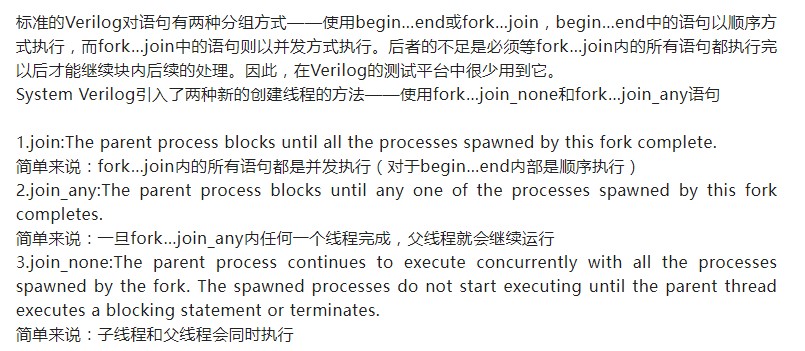

1085 标准的Verilog对语句有两种分组方式——使用begin…end或fork…join,begin…end中的语句以顺序方式执行,而fork…join中的语句则以并发方式执行。

2022-09-14 11:02:03 627

627

迭代语句主要用于重复执行的程序,在 CoDeSys 中,常见的迭代语句有 FOR,REPEAT 及WHILE 语句。

2023-01-30 17:45:29 1695

1695 在循环的过程中如果要退出循环,我们可以用break语句和continue语句。

2023-02-23 11:17:43 1853

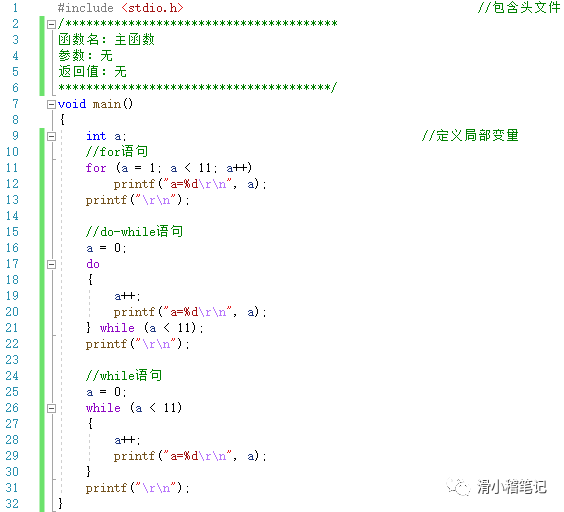

1853 循环结构是C语言中最后一种结构,常规中能够实现循环效果的语句有while,do-while和for三种,下面采用举例的方式来说明三种循环语句

2023-03-02 10:07:51 485

485

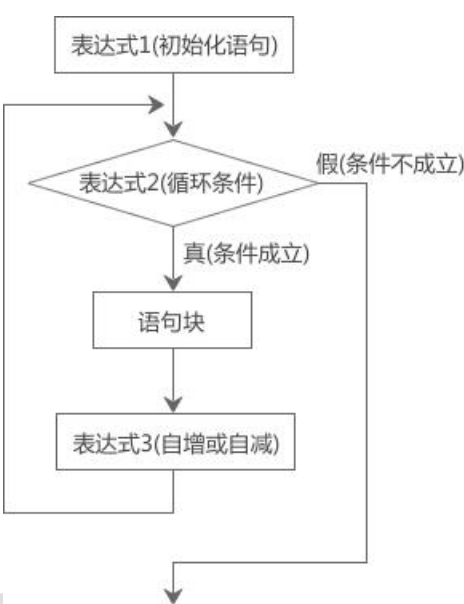

除了可以用while语句和do...while语句实现循环外,C语言还提供for语句实现循环,而且for语句更为灵活,不仅可以用于循环次数已经确定的情况,还可以用于循环次数不确定而只给出循环结束条件的情况,它完成可以代替while语句。

2023-03-09 11:14:19 750

750 一个循环体内又包含另一个完整的循环结构,称为循环的嵌套。内嵌的循环体中还可以嵌套循环,这就是多层循环。

3种常用循环语句:while语句、do...while语句和for语句可以相互嵌套。

2023-03-09 11:16:15 475

475 在这篇文章中,我们讨论了可以在verilog中使用的不同类型的循环 - for循环,while循环,forever循环和repeat循环。

2023-04-15 09:19:38 1789

1789 我们在上一篇文章中已经看到了如何使用程序块(例如 always 块来编写按顺序执行的 verilog 代码。

2023-04-18 09:45:45 2421

2421 我们在上一篇文章中已经看到了如何使用程序块(例如 always 块来编写按顺序执行的 verilog 代码。

我们还可以在程序块中使用许多语句来控制在我们的verilog设计中信号赋值的方式

2023-05-11 15:37:36 2835

2835

哈喽大家好,我是知道。今天带大家了解下Python的循环语句 定义循环语句允许我们执行一个语句或语句组多次 类型Python提供了两种不同类型的循环 for循环:重复执行语句 #打印1-10for

2023-05-11 17:39:33 595

595 本文主要介绍verilog常用的循环语句,循环语句的用途,主要是可以多次执行相同的代码或逻辑。

2023-05-12 18:26:43 1140

1140 综合就是将HDL语言转化成与,非,或门等等基本逻辑单元组成的门级连接。因此,可综合语句就是能够通过EDA工具自动转化成硬件逻辑的语句。

2023-06-28 10:39:46 784

784 MATLAB提供了多种条件语句和循环结构。

2023-07-05 09:41:27 2108

2108 条件语句和循环语句是计算机编程中常用的两种控制结构

2023-07-21 16:48:09 5583

5583

条件判断 语句块 什么是语句块呢? 语句块是在条件为真(条件语句)时执行或者执行多次(循环语句)的一组语句。在代码前放置空格来缩进语句即可创建语句块。 关于缩进: 使用tab键也可以缩进语句

2023-09-12 16:41:56 548

548 循环控制循环控制语句可以改变循环正常的执行顺序 循环控制语句 break语句:跳出本次循环(嵌套循环中只跳出一层循环) continue语句:跳过当前一轮循环体的剩余语句,重新测试循环状态,进入下一

2023-09-12 16:59:58 514

514

采用for循环语句,逐个bit位判断是否为1,为1则累加,否则保持不变,最终输出输入信号中1的数量。

2023-10-09 16:31:00 1247

1247

单片机中的for语句是一种常见的循环控制结构,用于重复执行一段代码块,可以简化程序的编写和减少代码量。本文将详细介绍单片机中for语句的运用。 一、for语句的基本结构和功能 for语句是一种迭代

2024-01-05 14:02:03 351

351 中的for循环也是并行执行的。 Verilog中的for循环可以用来实现重复的操作,例如在一个时钟周期中对多个电路进行操作。在循环内部,多个语句可以同时执行,而不受循环次数的限制。这种并行执行的机制使得Verilog在硬件设计中非常高效和灵活。 在Verilog中,for循环有两

2024-02-22 16:06:23 307

307

电子发烧友App

电子发烧友App

评论