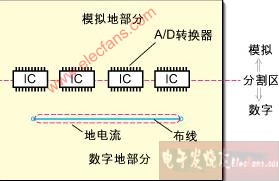

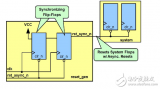

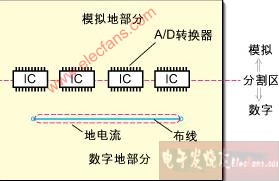

混合信号PCB的分区设计原则

混合信号电路PCB的设计很复杂,元器件的布局、布线以及电源和地线的处理

2009-03-25 11:40:23 785

785

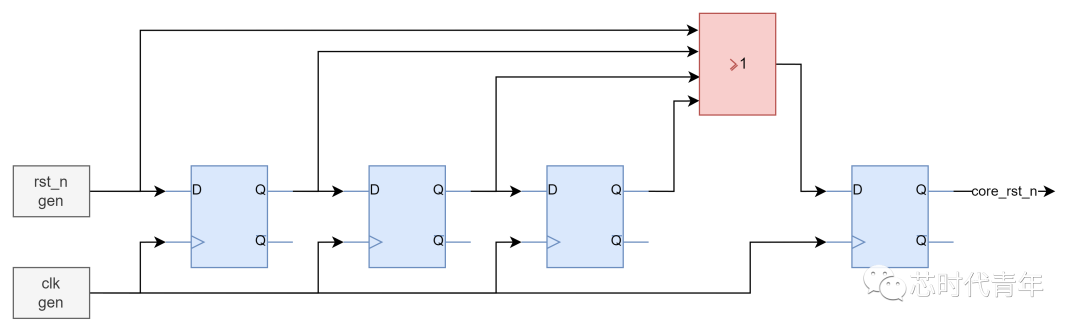

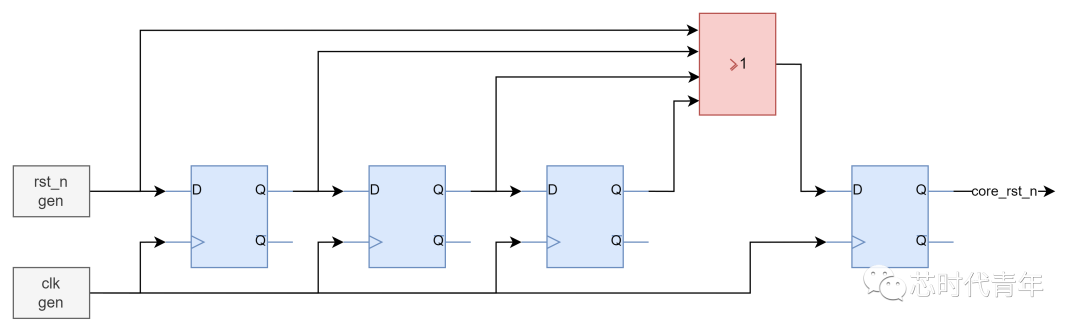

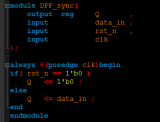

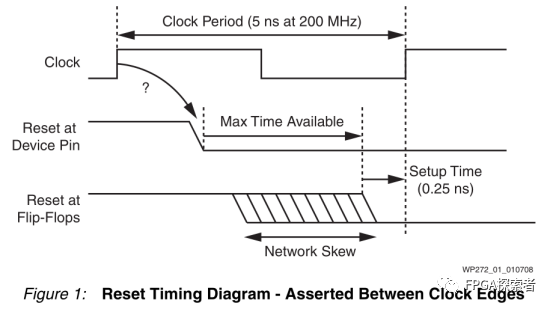

对FPGA设计中常用的复位设计方法进行了分类、分析和比较。针对FPGA在复位过程中存在不可靠复位的现象,提出了提高复位设计可靠性的4种方法,包括清除复位信号上的毛刺、异步复位同步释放、采用专用全局

2014-08-28 17:10:03 8153

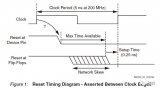

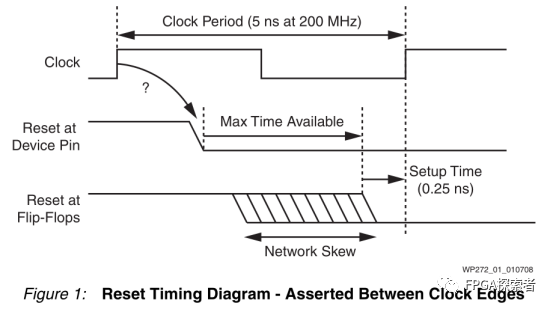

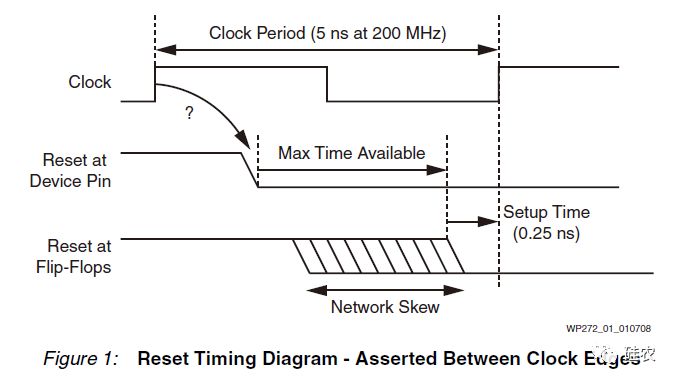

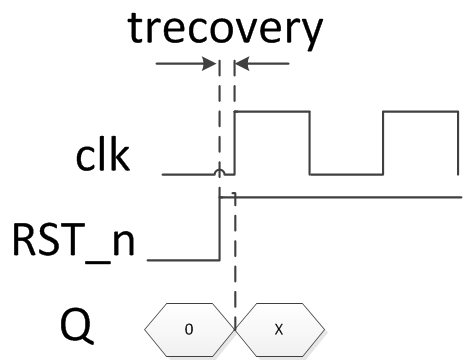

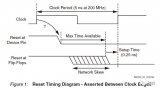

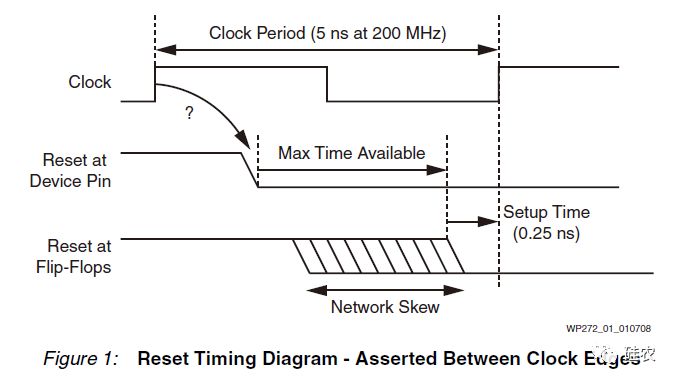

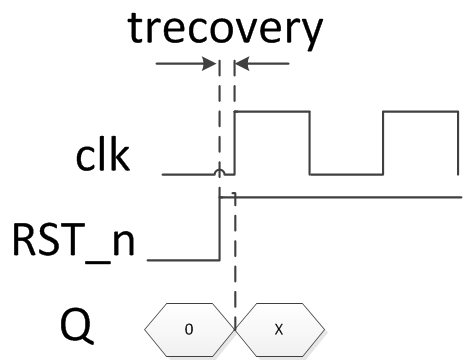

8153 异步复位信号a是异步复位信号源,异步复位信号b、c、d是到达触发器的异步信号。我们可以看到,b信号是在本周期就撤离了复位;c信号则由于复位恢复时间不满足,则可能导致触发器输出亚稳态;而d信号则由于延时太长(但是满足了复位去除时间),在下一个周期才撤离复位。

2020-06-26 05:36:00 22799

22799

本篇文章参考Xilinx White Paper:Get Smart About Reset: Think Local, Not Global 在没看这篇文章前,回想一下平时我们常用的复位方式

2020-11-18 17:32:38 3110

3110 内都是将复位信号作为一个I/O口,通过拨码开关硬件复位。后来也看了一些书籍,采用异步复位同步释放,对自己设计的改进。 不过自从我研读了Xilinx的White Paper后,让我对复位有了更新的认识

2020-12-25 12:08:10 2303

2303

复位信号在数字电路里面的重要性仅次于时钟信号。 对电路的复位往往是指对触发器的复位,也就是说电路的复位中的这个“电路”,往往是指触发器,这是需要注意的。

2023-04-21 09:16:49 505

505

针对异步复位、同步释放,一直没搞明白在使用同步化以后的复位信号时,到底是使用同步复位还是异步复位?

2023-06-21 09:59:15 647

647

在前面的文章中有过对于寄存器行为的描述,而复位方面,在电路设计时建议使用带异步复位/置位的寄存器。

2023-07-13 17:33:58 623

623

复位信号几乎是除了时钟信号外最常用的信号了,几乎所有数字系统在上电的时候都会进行复位,这样才能保持设计者确定该系统的系统模式的状态,以便于更好的进行电子设计,并且在任意时刻,确保使用者总能对电路系统进行复位,使电路从初始的状态开始工作。

2023-07-27 09:48:30 4638

4638

在前面的文章中有过对于寄存器行为的描述,而复位方面,在电路设计时建议使用带异步复位/置位的寄存器。

2023-08-01 16:04:11 1230

1230

复位信号在数字电路里面的重要性仅次于时钟信号。对一个芯片来说,复位的主要目的是使芯片电路进入一个已知的,确定的状态。

2023-08-27 10:18:51 1322

1322

复位信号在数字电路里面的重要性仅次于时钟信号。对电路的复位往往是指对触发器的复位,也就是说电路的复位中的这个“电路”,往往是指触发器,这是需要注意的。

2023-09-13 16:26:49 888

888

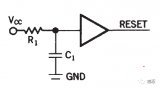

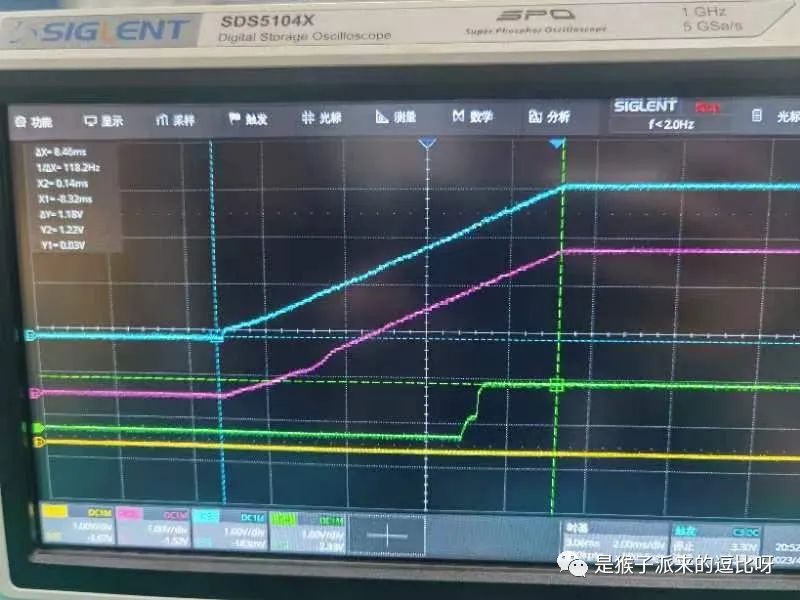

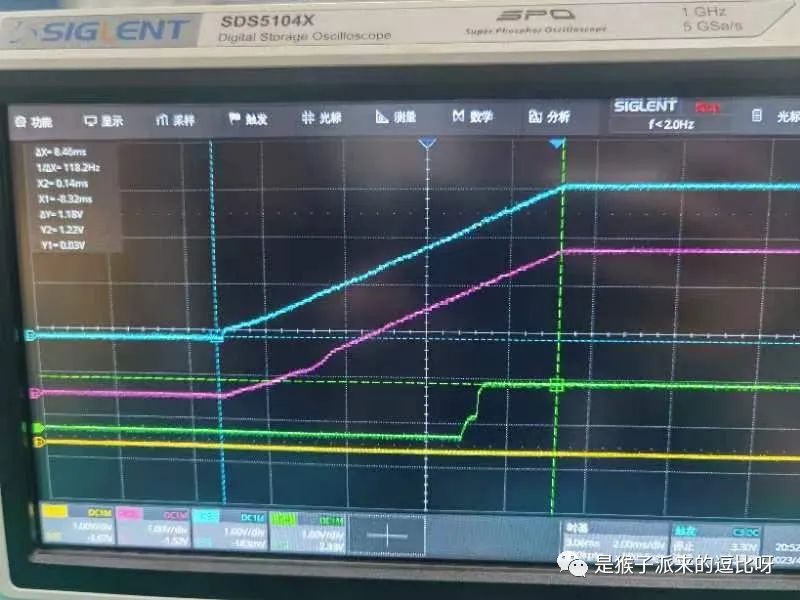

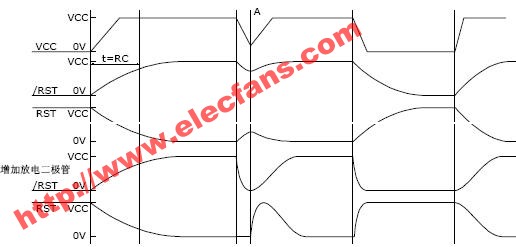

蓝色的是3.3V上电信号(除个别芯片使用其他电压外,整板使用3.3V供电),粉红色的复位信号(此处的复位信号是低电平有效的RC接反相器之后的输出),横轴每格为2ms,纵轴每格为1V。复位信号的产生

2023-11-22 15:03:07 1350

1350

经常在面试时问到一个问题:对于芯片中的复位信号我们通常会有哪些特殊处理?这个时候我一般希望得到的回答包括:复位消抖、异步复位同步撤离、降频复位、关断时钟复位和复位保护等处理方案。

2023-12-25 09:52:56 415

415

Xilinx Artix7 DEVB_124X92MM 6~16V

2023-03-28 13:05:55

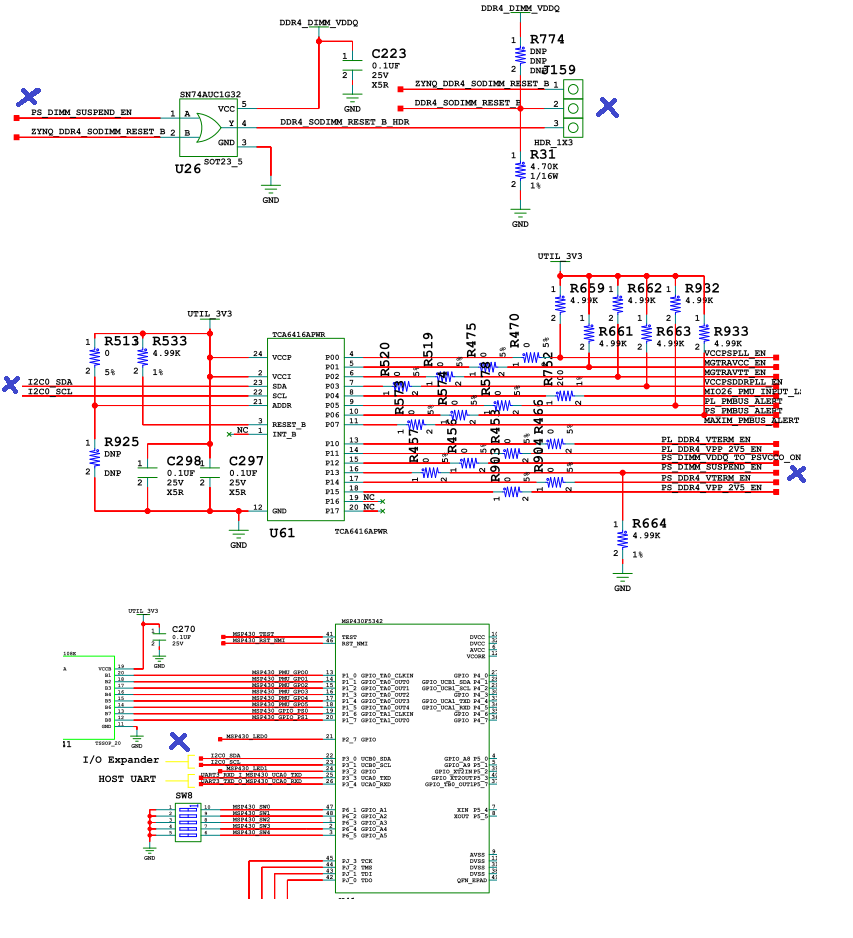

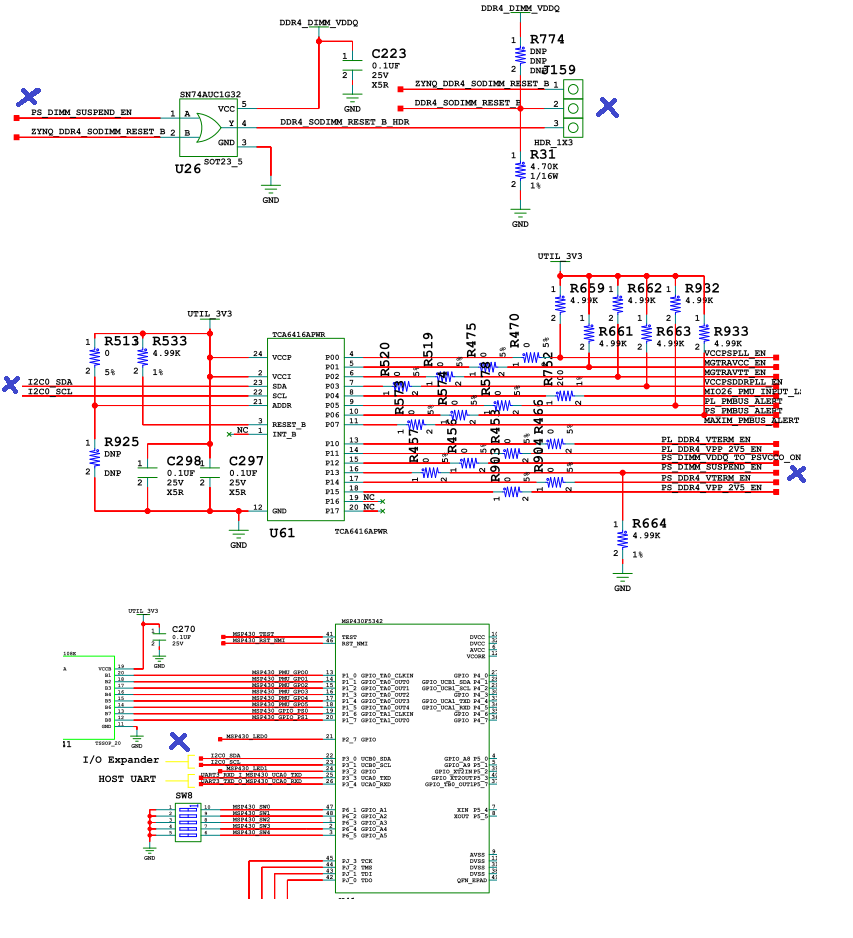

Xilinx-ZYNQ7000系列-学习笔记(3):系统复位与启动一、复位ZYNQ-7000 SoC系统中的复位可以由硬件、看门狗定时器、JTAG控制器或软件产生,可用于驱动系统中每个模块的复位信号

2022-01-25 06:49:13

Xilinx-ZYNQ7000系列-学习笔记(3):系统复位与启动一、复位ZYNQ-7000 SoC系统中的复位可以由硬件、看门狗定时器、JTAG控制器或软件产生,可用于驱动系统中每个模块的复位信号

2022-01-25 07:05:36

个MUX。利用这种2+1的组合可以产生DDR操作,Xilinx称之为ODDR2。每个存储单元都有6个接口信号:时钟+时钟时能,数据输入+输出,置位复位+翻转输入除了这些信号,存储单元还有一些属性设置

2012-08-02 22:48:10

信号完整性处理的8个基本原则

2021-01-14 07:19:08

需要注意以下几个要点:●尽可能使用FPGA的专用复位引脚。(特权同学,版权所有)●上电复位时间的长短需要做好考量。(特权同学,版权所有)●确保系统正常运行过程中复位信号不会误动作。(特权同学,版权所有) Xilinx FPGA入门连载

2019-04-12 06:35:31

FPGA引脚信号指配有什么原则?

2021-04-30 07:04:56

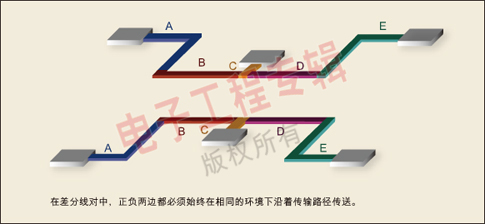

3W原则,例如时钟线,差分线,视频、音频信号线,复位信号线及其他系统关键电路需要遵循3W原则,而并不是板上所有的布线都要强制符合3W原则。 满足3W原则能使信号间的串扰减少70%,而满足10W则能使信号

2020-09-27 16:49:19

ADAPTER TC2050 FOR XILINX CABLE

2023-03-22 19:59:52

我很抱歉,如果这是一个愚蠢的问题,因为似乎答案应该在我面前,但我无法弄清楚。Xilinx VC707评估板中的复位信号在哪里?它没有在主约束文件中列出,我似乎无法在示例VC707项目中找到它。人们如何将电路重置为此电路板上的已知状态?提前致谢

2020-04-01 08:54:50

图中,可看到启动转换前送入一个复位信号,搞不清这个复位信号是内部产生的,还是外部操作复位引脚产生的,因在手册中数字复位与同步信号章节,提到SYNC_IN加入一脉冲,会使得数字模块发生内部复位,该复位与图中复位时同一个复位信号吗!实际开启采集,需每次给这个信号吗?

2023-12-11 06:15:17

大家好我有一个关于如何处理virtex 5中的复位信号的问题。用于复位整个设计的同步复位信号。复位信号的时序很难满足,因为扇出很大。如果我减少synplify pro中的扇出限制。我为其余的东西留下了很多复杂的线条。这需要很多逻辑。应该有更好的解决方案。有人可以帮助吗?问候小东宇

2020-06-03 08:18:11

的时候,其间距应该遵循3W原则,例如时钟线,差分线,视频、音频信号线,复位信号线及其他系统关键电路需要遵循3W原则,而并不是板上所有的布线都要强制符合3W原则。20H原则:由于电源层与地层之间的电场是变化

2019-05-08 08:30:00

`手机Layout中信号布线原则介绍 ,整个文档内容如下,非常不错的资料,在这里跟大家分享了[hide] [/hide]`

2011-12-20 11:21:38

是否有Xilinx或任何其他实例提供的编码风格指南?我知道综合指南讲述了如何编写某些结构,但我正在寻找有关过程,信号,流水线信号,项目组织,...的命名约定的指导。我可以想象Xilinx编写IP代码

2019-04-10 10:54:37

设备,直接威胁铁路正常的安全生产。所以,加强信号设备防雷工作尤为重要。铁路信号综合防雷整治的原则铁路信号设备本身的电磁兼容性应符合《铁道信号电气设备电磁兼容性试验及其限制》(TB/T3073-2003

2012-02-03 14:05:25

图中,可看到启动转换前送入一个复位信号,搞不清这个复位信号是内部产生的,还是外部操作复位引脚产生的,因在手册中数字复位与同步信号章节,提到SYNC_IN加入一脉冲,会使得数字模块发生内部复位,该复位与图中复位时同一个复位信号吗!实际开启采集,需每次给这个信号吗?

2018-08-02 08:10:35

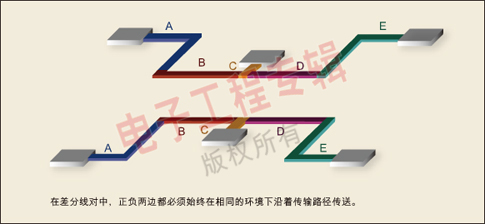

差分信号走线原则

差分线对的工作原理是使接收到的信号等于两个互补并且彼此互为参考的信号之间的差值,因此可以极大地降低信

2008-05-09 10:00:36 38812

38812

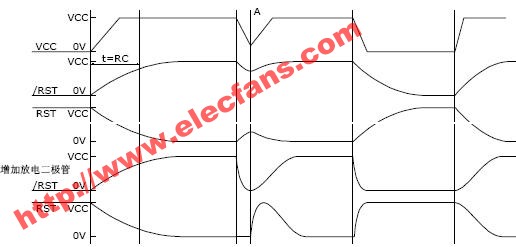

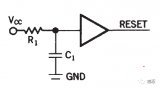

RC复位电路

复位电路的基本功能是:系统上电时提供复位信号,直至系统电源稳定后,撤销复位信号。为可靠起见,电

2008-10-24 15:30:29 2841

2841

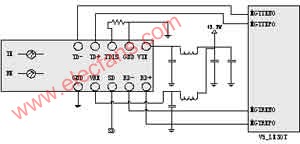

本文设计的基于Xilinx FPGA的千兆位以太网及E1信号的光纤传输系统采用Xilinx XC5VLX30T芯片,通过以太网测试仪和数据误码仪对本系

2010-07-06 09:09:10 2336

2336

本实用新型公开了一种复位电路及具有所述复位电路的电视机。本实用新型通过采用分立元器件组建复位电路为电视机内部控制系统提供上电复位信号

2011-11-11 17:25:54 45

45 上一篇写了基于Xilinx FPGA的通用信号发生器的案例,反响比较好,很多朋友和我探讨相关的技术,其中就涉及到信号的采集,为了使该文更有血有肉,我在写一篇基于Xilinx FPGA的通用信号采集器,望能形成呼应,以解答大家的疑问。

2017-02-11 03:11:37 1712

1712

在Xilinx 的FPGA器件中,全局的复位/置位信号(Global Set/Reset (GSR))(可以通过全局复位管脚引入)是几乎绝对可靠的,因为它是芯片内部的信号。

2017-02-11 11:46:19 876

876

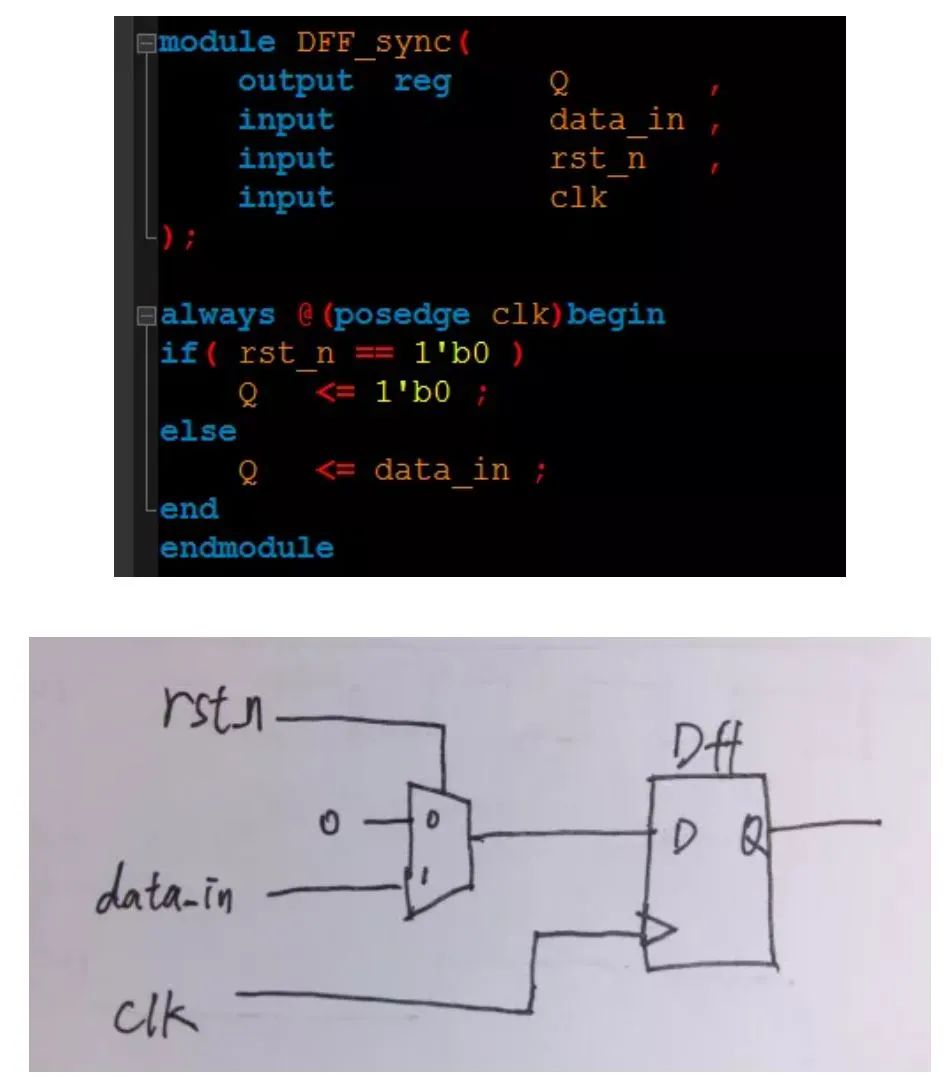

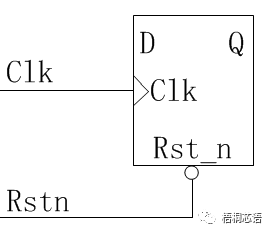

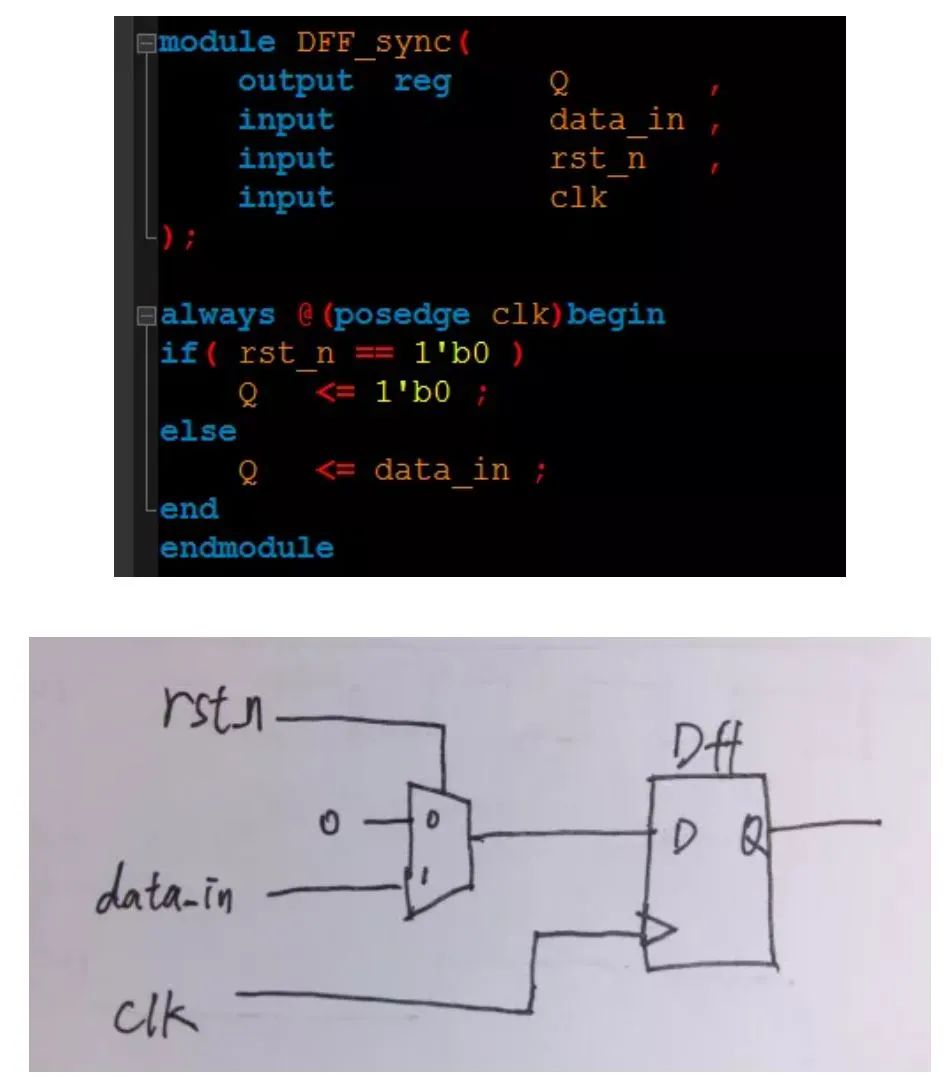

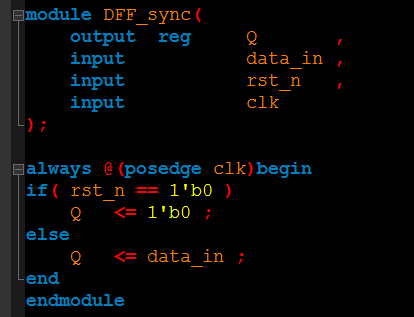

顾名思义,同步复位就是指复位信号只有在时钟上升沿到来时,才能有效。否则,无法完成对系统的复位工作。

2017-02-11 12:40:11 7563

7563

系统的复位系统由POR和PUC信号驱动,各种不同的事件能触发产生这些复位信号,而根据不同的复位信号会产生不同的初始化状态。

2017-09-21 15:59:59 1

1 在FPGA设计中,复位起到的是同步信号的作用,能够将所有的存储元件设置成已知状态。在数字电路设计中,设计人员一般把全局复位作为一个外部引脚来实现,在加电的时候初始化设计。全局复位引脚与任何其它输入

2017-11-22 17:03:45 5125

5125

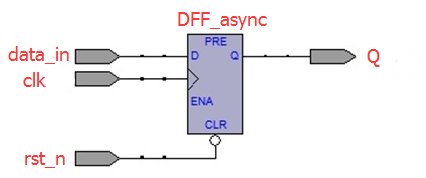

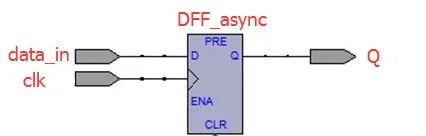

异步复位原理:异步复位只要有复位信号系统马上复位,因此异步复位抗干扰能力差,有些噪声也能使系统复位,因此有时候显得不够稳定,要想设计一个好的复位最好使用异步复位同步释放。

2017-11-30 08:45:46 94797

94797

是指复位信号是异步有效的,即复位的发生与clk无关。后半句“同步释放”是指复位信号的撤除也与clk无关,但是复位信号是在下一个clk来到后起的作用(释放)。

2017-11-30 08:58:14 23613

23613

在带有复位端的D触发器中,当reset信号“复位”有效时,它可以直接驱动最后一级的与非门,令Q端“异步”置位为“1”or“0”。这就是异步复位。当这个复位信号release时,Q的输出由前一级的内部输出决定。

2017-11-30 09:15:37 10572

10572

POR是上电复位信号,它只在以下两个事件发生时产生:1、芯片上电。2、RST/NMI设置成复位模式,在RST/NMI引脚上出现低电平信号。

2018-04-10 16:15:32 6130

6130 Xilinx公司将讲述:灵活混合信号处理技术演示。

2018-06-01 11:47:00 3392

3392 对于xilinx 7系列的FPGA而言,flip-flop支持高有效的异步复/置位和同步复位/置位。对普通逻辑设计,同步复位和异步复位没有区别,当然由于器件内部信号均为高有效,因此推荐使用高有效的控制信号,最好使用高有效的同步复位。输入复位信号的低有效在顶层放置反相器可以被吸收到IOB中。

2018-07-13 09:31:00 6091

6091 通常情况下,复位信号的异步释放,没有办法保证所有的触发器都能在同一时间内释放。触发器在A时刻接收到复位信号释放是最稳定的,在下一个时钟沿来临被激活,但是如果在C时刻接收到复位信号释放无法被激活,在B时刻收到复位信号释放,则会引起亚稳态。

2018-11-19 10:34:01 9401

9401

嵌入式世界2012的Xilinx 7系列模拟混合信号评估平台演示

2018-11-22 06:24:00 3121

3121 异步复位是不受时钟影响的,在一个芯片系统初始化(或者说上电)的时候需要这么一个全局的信号来对整个芯片进行整体的复位,到一个初始的确定状态。

2019-01-04 08:59:20 6296

6296 xilinx推荐尽量不复位,利用上电初始化,如果使用过程中需要复位,采用同步高复位。

2019-02-14 14:29:49 5419

5419 在普通印制电路板的布线中由于信号是低速信号,所以在3W原则的基本布线规则下按照信号的流向将其连接起来,一般都不会出现问题。但是如果信号是100M以上的速度时,布线就很有讲究了。由于最近布过速度高达300M的DDR信号,所以仔细说明一下DDR信号的布线原则和技巧。

2019-03-24 10:00:06 6908

6908

同步复位和异步复位都是状态机的常用复位机制,图1中的复位电路结合了各自的优点。同步复位具有时钟和复位信号之间同步的优点,这可以防止时钟和复位信号之间发生竞争条件。但是,同步复位不允许状态机工作在直流时钟,因为在发生时钟事件之前不会发生复位。与此同时,未初始化的I/O端口可能会遇到严重的信号争用。

2019-08-12 15:20:41 6901

6901

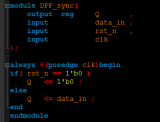

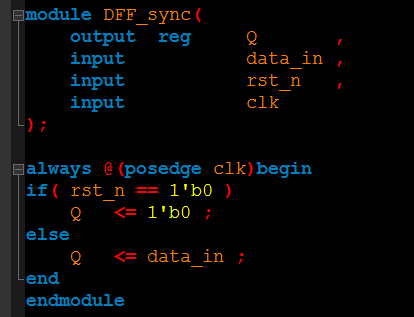

同步复位:顾名思义,同步复位就是指复位信号只有在时钟上升沿到来时,才能有效。否则,无法完成对系统的复位工作。用Verilog描述如下:异步复位:它是指无论时钟沿是否到来,只要复位信号有效,就对系统进行复位。用Verilog描述如下:

2020-09-14 08:00:00 0

0 Xilinx的开发板ZCU102支持休眠到内存(suspend-to-ram)。休眠到内存时,DDR进入自刷新,MPSoC被关电,完全不耗电。唤醒时,MPSoC根据外部输入信号判断出不是上电启动而是

2020-11-04 17:02:46 2422

2422

线长距离走线的时候,其间距应该遵循3W原则,例如时钟线,差分线,视频、音频信号线,复位信号线及其他系统关键电路需要遵循3W原则,而并不是板上所有的布线都要强制符合3W原则。 满足3W原则能使信号间的串扰减少70%,而满足10W则能使信号间的串扰减少近

2022-12-26 09:35:56 841

841 最近看 advanced fpga 以及 fpga 设计实战演练中有讲到复位电路的设计,才知道复位电路有这么多的门道,而不是简单的外界信号输入系统复位。 流程: 1. 异步复位: 优点:⑴大多数

2020-10-30 12:17:55 323

323 ,其间距应该遵循 3W 原则,例如时钟线,差分线,视频、音频信号线,复位信号线及其他系统关键电路需要遵循 3W 原则,而并不是板上所有的布线都要强制符合 3W 原则。 满足 3W 原则能使信号间的串扰减少 70%,而满足 10W 则能使信号间的串扰减少近 98%。 3W 原则

2023-02-01 16:53:07 3977

3977 遵循 3W 原则,例如时钟线,差分线,视频、音频信号线,复位信号线及其他系统关键电路需要遵循 3W 原则,而并不是板上所有的布线都要强制符合 3W 原则。

2020-12-16 14:49:00 23

23 本文档的主要内容详细介绍的是如何使用Xilinx的FPGA对高速PCB信号实现优化设计。

2021-01-13 17:00:59 25

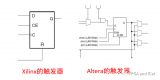

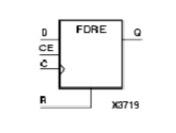

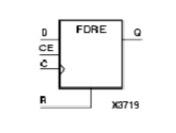

25 FDRE代表一个单D型触发器,含的有五个信号分别为: 数据(data,D)、时钟使能(Clock enable,CE)、时钟(Clock)、同步复位(synchronous reset,R)、数据

2022-07-25 18:12:44 3300

3300

FDRE代表一个单D型触发器,含的有五个信号分别为: 数据(data,D)、时钟使能(Clock enable,CE)、时钟(Clock)、同步复位(synchronous reset,R)、数据

2021-01-25 07:27:20 3

3 针对异步复位、同步释放,一直没搞明白在使用同步化以后的复位信号时,到底是使用同步复位还是异步复位?

2021-04-27 18:12:10 4196

4196

有客户在产品的设计中,使用外部IC的GPIO通过连接NRST引脚来对STM32MCU进行复位控制时,会遇到以下问题:IC可以对MCU进行复位控制,但是芯片内部的复位信号(如看门狗等)不能对MCU进行复位,甚至影响引脚功能

2021-04-28 15:16:41 19

19 一、复位电路概述 复位信号在数字电路里面的重要性仅次于时钟信号。对电路的复位往往是指对触发器的复位,也就是说电路的复位中的这个“电路”,往往是指触发器,这是需要注意的。有的电路需要复位信号,就像

2021-06-28 09:49:22 6086

6086 产品在设计中某些状态下需要MCU进行复位,华大MCU包含了7个复位信号来源,每个复位信号都可以让 CPU 重新运行,绝大多数寄存器会被复位到复位值,程序计数器 PC 会被复位指向 00000000。

2021-10-12 11:24:40 1693

1693 对于硬件设计来说,复位电路是必不可少的一部分,为了确保微机系统中电路稳定可靠工作,复位电路的第一功能是上电复位。在 FPGA 设计中,复位起到的是同步信号的作用,能够将所有的存储元件设置成已知状态

2021-11-06 09:20:57 20

20 MSP430的复位信号有2种: 文档: 上电清除信号(PUC)、 上电复位信号(POR)。 个人理解: POR是第一次上电复位,PUC是在带电的情况下发生复位,冷启动和热启动

2021-12-16 16:56:51 12

12 MSP430的复位信号有2种: 文档: 上电清除信号(PUC)、 上电复位信号(POR)。 个人理解: POR是第一次上电复位,PUC是在带电的情况下发生复位,冷启动和热启动

2021-12-16 16:57:09 10

10 复位芯片内含阈值电压精确抗干扰能力强的施密特触发器,当系统一上电或电源电压跌落到规定值时,复位芯片输出一个低电平复位信号,当电压升高到规定值以上时,复位芯片输出高阻态。

2021-12-20 11:15:30 17874

17874 第二篇文章——STM32电源、复位、时钟电源管理电源电压调节器可编程电压监测器(PVD: Programmable voltage detector )低功耗模式复位Cortex-M3的复位信号

2022-01-05 14:25:10 10

10 对于我们使用Xilinx或其他的成熟IP而言,IP相当于一个黑匣子,内部实现的逻辑功能我们知道,但是控制不了,只能默认OK;一般而言,成熟IP都是经过反复验证和使用,确实没有什么问题。所以,IP能不能用,首先要做的就是确保时钟和复位。

2022-02-19 18:30:07 3732

3732

复位信号在数字电路里面的重要性仅次于时钟信号。对电路的复位往往是指对触发器的复位,也就是说电路的复位中的这个“电路”,往往是指触发器,这是需要注意的。

2022-03-22 08:53:24 8701

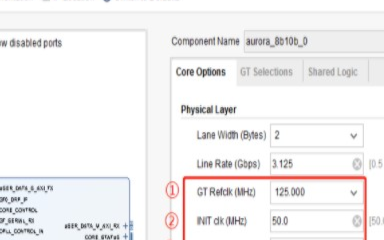

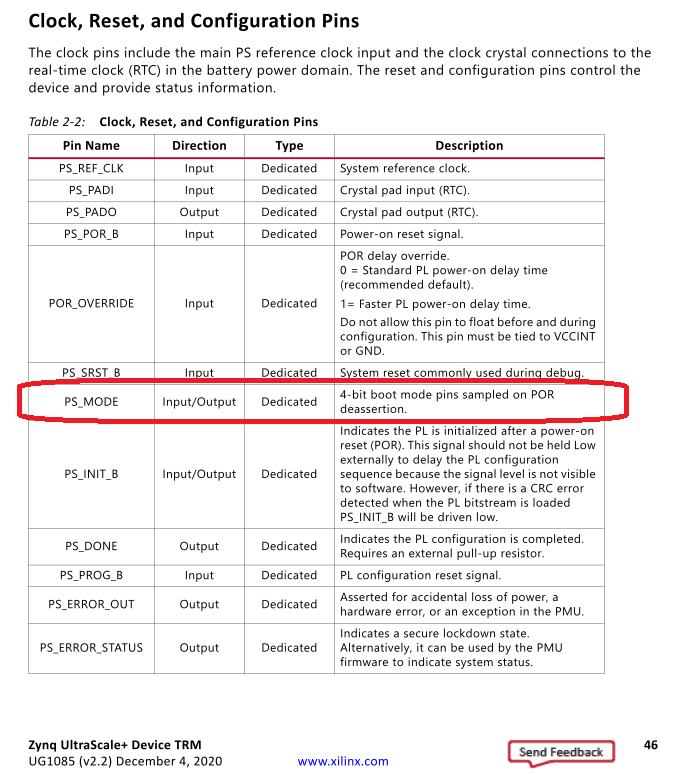

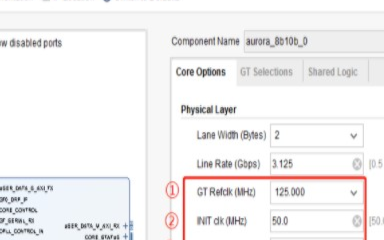

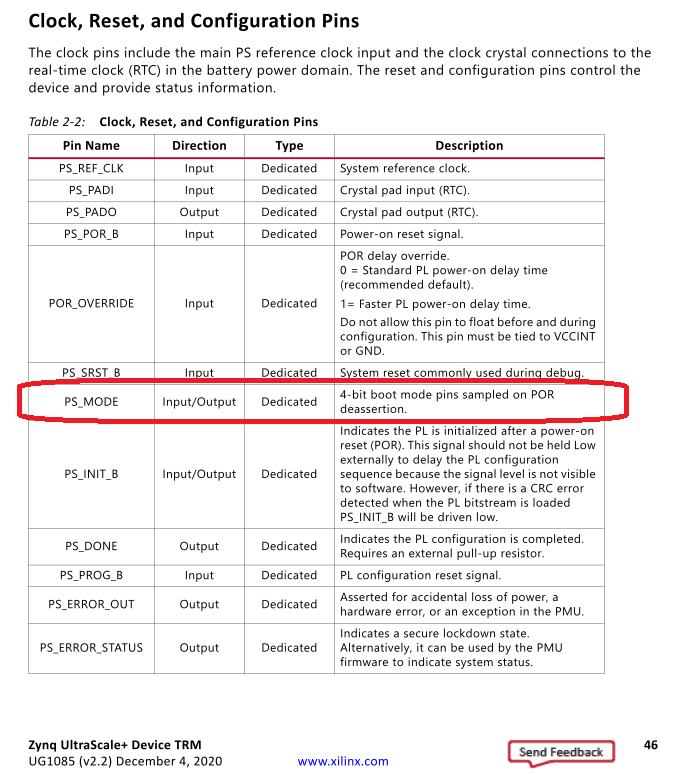

8701 在Xilinx的ZCU102和ZCU106单板设计中,使用了管脚PS_MODE1作为外部USB Phy的复位信号。在MPSoC的文档ug1085和ug1087中,关于PS_MODE1的信息比较少。下面是更详细的描述。

2022-08-02 09:38:51 2142

2142

复位信号在数字电路里面的重要性仅次于时钟信号。对一个芯片来说,复位的主要目的是使芯片电路进入一个已知的,确定的状态。主要是触发器进入确定的状态。在一般情况下,芯片中的每个触发器都应该是可复位的。

2022-09-19 10:07:20 20385

20385 FPGA设计中几乎不可避免地会用到复位信号,无论是同步复位还是异步复位。我们需要清楚的是复位信号对时序收敛、资源利用率以及布线拥塞都有很大的影响。

2023-03-30 09:55:34 806

806 1、定义 复位信号是一个脉冲信号,它会使设计的电路进入设定的初始化状态,一般它作用于寄存器,使寄存器初始化为设定值;其脉冲有效时间长度必须大于信号到达寄存器的时延,这样才有可能保证复位的可靠性

2023-04-06 16:45:02 782

782 现在的FPGA正变得越来越复杂,向引脚分配信号的任务曾经很简单,现在也变得相当繁复。下面这些用于向多用途引脚指配信号的指导方针有助于设计师根据最多到最少的约束信号指配原则提前考虑信号指配,并减少反复的次数。

2023-05-04 17:38:53 597

597 复位信号在数字电路里面的重要性仅次于时钟信号。 对电路的复位往往是指对触发器的复位,也就是说电路的复位中的这个“电路”,往往是指触发器,这是需要注意的。

2023-05-18 09:08:08 1464

1464

功能会对 FPGA 设计的速度、面积和功耗产生不利影响。 在继续我们的讨论之前,有必要强调一个基本原则:FPGA 是可编程设备,但这并不意味着我们可以对FPGA 中的每个功能进行编程。这一基本原则将在本文的其余部分进一步阐明。 在添加复位输

2023-05-25 00:30:01 483

483 复位信号在数字电路里面的重要性仅次于时钟信号。对电路的复位往往是指对触发器的复位,也就是说电路的复位中的这个“电路”,往往是指触发器,这是需要注意的。

有的电路需要复位信号,就像是有的电路需要时钟信号那样,而有的电路是不需要复位信号的。

2023-05-25 14:30:11 270

270

复位信号在数字电路里面的重要性仅次于时钟信号。对电路的复位往往是指对触发器的复位,也就是说电路的复位中的这个“电路”,往往是指触发器,这是需要注意的。

有的电路需要复位信号,就像是有的电路需要时钟信号那样,而有的电路是不需要复位信号的。

2023-05-25 14:31:21 346

346

jtag端口的复位信号jtag_trst用于复位TAP状态机模块,该复位信号可选。

2023-05-25 15:09:43 622

622

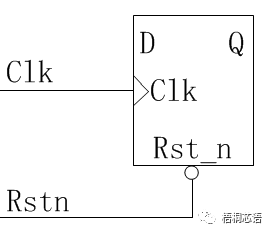

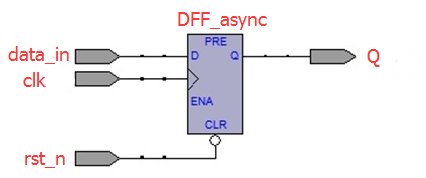

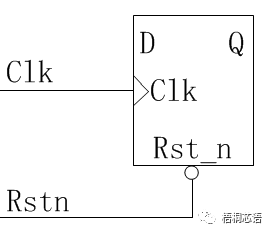

异步复位触发器则是在设计触发器的时候加入了一个复位引脚,也就是说**复位逻辑集成在触发器里面**。(一般情况下)低电平的复位信号到达触发器的复位端时,触发器进入复位状态,直到复位信号撤离。带异步复位的触发器电路图和RTL代码如下所示:

2023-05-25 15:57:17 567

567

尽量少使用复位,特别是少用全局复位,能不用复位就不用,一定要用复位的使用局部复位;

2023-06-21 09:55:33 1337

1337

对于复位信号的处理,为了方便我们习惯上采用全局复位,博主在很长一段时间内都是将复位信号作为一个I/O口,通过拨码开关硬件复位。

2023-06-21 10:39:25 651

651

能不复位尽量不用复位,如何判断呢?如果某个模块只需要上电的时候复位一次,工作中不需要再有复位操作,那么这个模块可以不用复位,用上电初始化所有寄存器默认值

2023-06-28 14:44:46 526

526

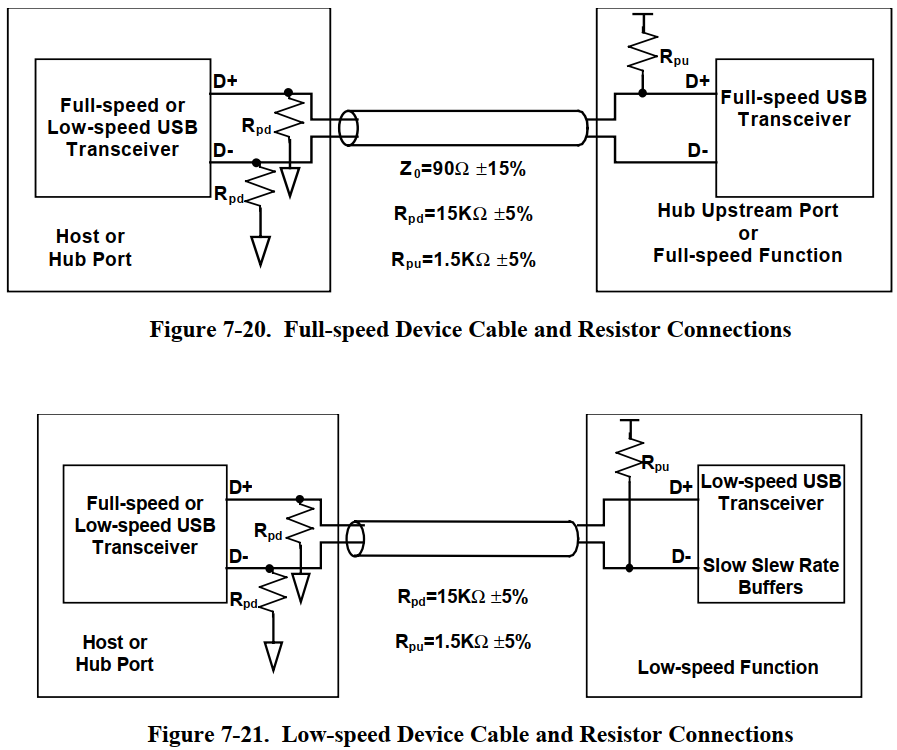

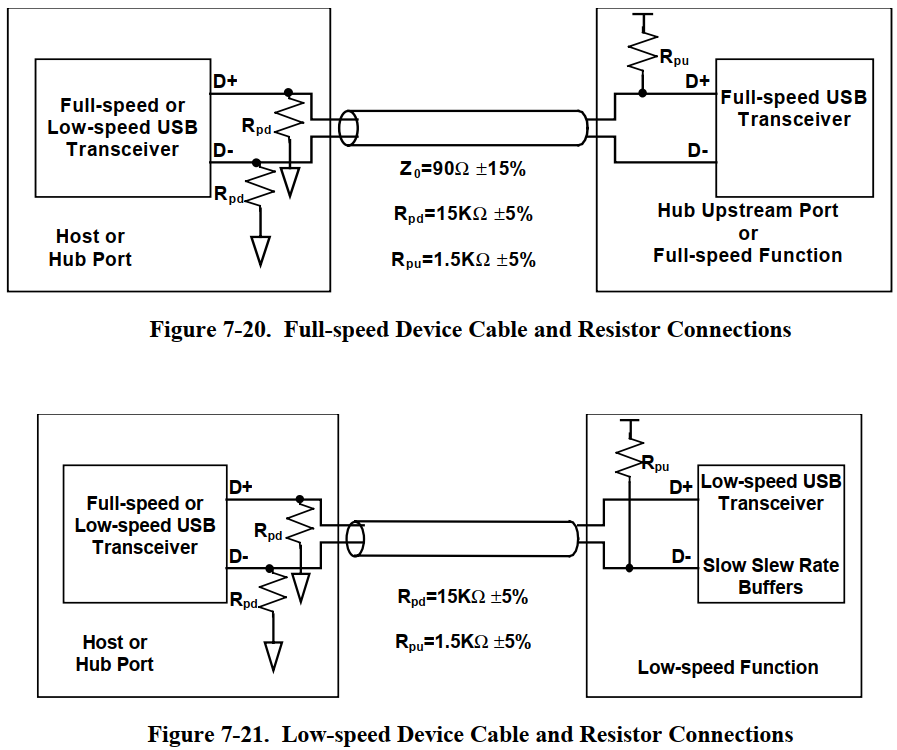

复位 从状态切换图上看,一个 USB 设备连接后,它将会被供电,然后被复位。当软件出错时,我们也可以发出复位信号重新驱动设备。 那么,USB Hub 端口或 USB 控制器端口如何发出复位信号?发出

2023-07-20 10:05:47 807

807

。 2. 外部复位:这种方式是通过外部信号触发,例如按下复位按钮,或者给RESET管脚输入一个低电平信号来触发复位。 3. 独立看门狗复位:通过独立看门狗电路计时到达一定时间而触发复位。 4. 监控电路复位:当单片机芯片内部几个重要信号无

2023-10-17 16:44:55 1424

1424 如果FPGA没有外部时钟源输入,可以通过调用STARTUP原语,来使用FPGA芯片内部的时钟和复位信号,Spartan-6系列内部时钟源是50MHz,Artix-7、Kintex-7等7系列FPGA是65MHz。

2023-10-27 11:26:56 973

973

通孔和盲孔对信号的差异影响有多大?应用的原则是什么? 在PCB设计中,通孔和盲孔的应用都极为广泛。然而两者在传输信号时,存在着一定的差异。那么通孔和盲孔之间到底有哪些不同之处?它们对信号的传输会有

2023-10-31 14:34:13 476

476 电子发烧友网站提供《数混合信号器件的一般接地原则.pdf》资料免费下载

2023-11-29 10:45:30 1

1 HT7044A 的复位原理,包括其工作原理、电路结构和操作方式。 HT7044A 的复位原理基于外部复位引脚(RESET)和内部复位逻辑电路。当 RESET 引脚接收到外部复位信号时,复位逻辑电路会检测到这个信号,并执行相应的复位操作,使系统中的各个模块和寄

2024-01-04 11:24:41 415

415 电源监测芯片复位电路:这是最常见的复位电路类型,使用专用的电源监测芯片来监测电源电压,并在电压低于或高于预设阈值时触发复位信号。

2024-01-16 16:04:14 445

445 复位方式具有精确控制的特点,因为复位信号与时钟信号同步工作,所以可以保证复位信号与时钟信号的相位精确匹配。同步复位的优势主要有以下几点: 1. 精确控制:同步复位可以确保复位信号和时钟信号的相位一致,避免由于信号

2024-01-16 16:25:52 202

202 复位信号存在亚稳态,有危险吗? 复位信号在电子设备中起着重要的作用,它用于使设备回到初始状态,以确保设备的正常运行。然而,我们有时会发现复位信号存在亚稳态,这意味着信号在一定时间内未能完全复位

2024-01-16 16:25:56 113

113 复位针脚是指在集成电路或者微控制器中用于复位电路的引脚。当该引脚接收到复位信号时,会使整个芯片回到初始状态,清除所有寄存器和内部状态,重新开始执行程序。

2024-01-20 09:57:06 337

337

电子发烧友App

电子发烧友App

评论