0 引言

随着航天技术的发展,空间任务日益复杂化、多样化,未来航天系统对处理器的性能要求越来越高。在一些航天设备如星载 ATP 等系统的电子模块设计中,基于 SRAM 的现场可编程门阵列(FPGA)得到了日益广泛的应用。空间环境中的电子系统设计,不仅要满足高性能,而且其数据处理、传输和控制的准确性和可靠性也必须得到保证。对于机载、星载、空间武器和其他空间应用电子系统,往往暴露在形形色色的电磁辐射环境中,如α粒子、宇宙射线、外太空强辐射等等恶劣环境,加之一些电子系统工作在地面的高电磁辐射环境中,这些辐射环境中充满了各种高能粒子,高能粒子撞击工作中的电子器件会引发辐射效应,如单粒子翻转(SEU)等,并导致器件发生故障,由辐射效应引起的软错误是导致空间环境中电子系统失效的重要原因之一[1]。

在提高系统可靠性与安全性方面,避错与容错技术是常用的两种关键技术。微电子抗辐射加固技术[2],通过对材料选取、工艺结构设计等方面进行加固设计,在物理层消除导致损伤的各类寄生参数, 能有效提高电子器件的抗辐射能力。但是仅在物理层上对系统进行故障防护不能满足恶劣环境中的系统可靠性要求,还需要从电路设计方面对系统功能进行保护。运用错误校正码(ECC)技术[3],在数据包的后端添加额外的校验数据位,来实现读取 / 写入数据的准确性,能在一定程度上对存储器进行检错和纠错。容错设计技术,如采用冗余设计来“屏蔽”或“隔离”故障,如信息冗余[4]、硬件冗余[5]等,进而在一定时期内将故障的影响掩盖起来,使发生故障的电子系统在一定时期内仍能正常工作,但这种方式并未排除故障,随着故障的累积和叠加,系统仍然可能失效,所以赋予系统故障自修复能力能有效减少故障累积,提高系统的可靠性。

本文从故障容错和故障自修复角度对系统进行芯片级的可靠性设计,提出了一种基于 SRAM 型 FPGA 的实时容错自修复系统结构,并将该设计结构在 Xilinx Virtex-6 FPGA 上进行了设计验证。

1 基于动态部分重构的模块修复

FPGA 的配置可分为静态配置和动态配置,静态配置通常对整个 FPGA 模块进行重新配置,系统功能在配置过程时中断,并在配置结束后改变系统功能。动态配置,又称为动态部分重构,能够在不干扰 FPGA 内部其他模块工作的同时动态地对部分区域的逻辑功能进行修改。其核心思想是将 FPGA 内部的逻辑资源从物理布局上划分为静态区域和若干个动态区域。每个动态区域可以对应有多个配置文件,以实现不同的功能,将这些配置文件事先存放在片外存储器中。在系统运行的不同时刻,根据系统的实际需求加载不同的配置文件到同一个动态区域来实现相应的逻辑功能。在某一动态区域进行功能切换时,不影响静态区域和其他动态区域的逻辑功能,系统依然处于连续运行状态。

动态部分重构技术能对 FPGA 的部分资源实现分时复用,使芯片能够在不同时刻实现不同的功能,提高了芯片资源的利用率,已广泛应用于工业系统设计中,如文献[6]中结合动态部分重构技术对工业传感器数据采集系统进行设计,针对不同的传感器切换不同的功能。该技术还可应用于可重构计算[7]、可进化硬件[8-9]、容错设计[10-14]等方面。将动态部分重构技术和冗余技术结合,即将冗余设计中各冗余模块分别置于一动态区域中,在故障发生时通过动态重构对故障模块进行修复,可以避免故障的累积和叠加,在容错的同时赋予系统故障自修复能力。

2 粗粒度和细粒度的三模冗余自修复结构

2.1 粗粒度的三模冗余设计结构

典型的模块冗余技术——N 模冗余设计:将功能模块复制为 N 份,N 个模块具有相同的输入,N 个模块的输出经过多数表决器表决输出。N 模冗余系统在工作过程中能同时容忍不超过半数的冗余模块发生故障而不影响最终的系统输出。随着冗余模块的数量增加,系统的容错能力提高,但同时系统的硬件资源开销和功耗增大,综合考虑容错能力和资源开销,三模冗余(TMR)技术具有最高的性能表现。

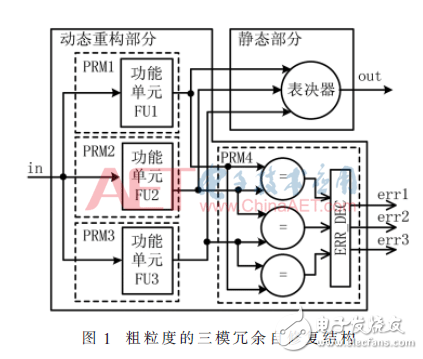

FPGA 的系统通常可以分为多个功能模块,粗粒度的三模冗余设计结构以整个功能模块为单位进行冗余设计,如图 1 所示,即将整个功能模块作为一个冗余单位,将整个功能模块复制三份,将每个功能单元模块 FU1~FU3 配置到单独的部分重构模块(PRM)中,使得每个冗余模块都可以独立被修复。表决器选择多数的输入结果进行输出。在粗粒度的三模冗余设计结构中,只要两个冗余模块的输出结果正确,就能保证整个模块输出正常,当其中任意模块发生故障时,通过系统的故障检测机制可进行故障定位,隔离故障区域并进行自修复操作。

2.2 细粒度的三模冗余设计结构

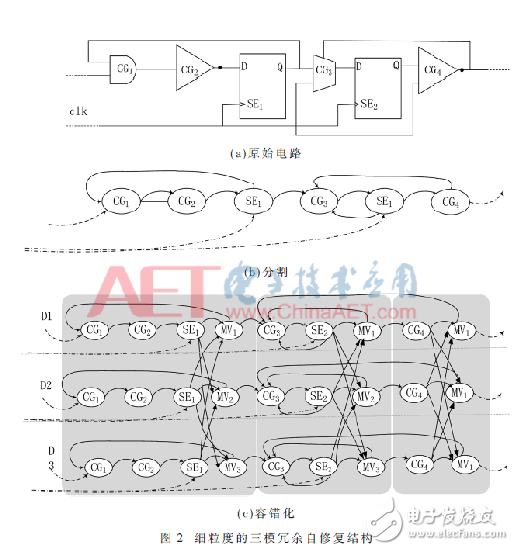

采用粗粒度设计结构能有效提高系统的可靠度,但其仍然存在一些不足,一是当多数表决器出现故障时整个自修复结构本身不可靠;二是由于模块粒度较大,一些不能导致模块功能失效的隐性故障持续累积,容易导致多个模块同时故障,使得防护结构失效。本文中细粒度的三模冗余设计结构能有效减少故障累积,该设计结构将一功能模块拆分为若干个独立的时序元件和组合逻辑部分,本文将该设计结构利用图形化表示来说明,将功能单元模块中的组合逻辑表示为 CG,时序元件表示为 SE,则利用有向图表示方法可以将图 2(a)电路表示为图 2(b)。

细粒度的三模冗余容错自修复结构建立在有向图表示方法基础之上,其核心思想是,将电路分割为逻辑电路和时序电路,在时序电路输出插入多数表决器,然后再对原始电路进行三模冗余设计,使得此自修复结构具有三个表决器,因此加强了此结构的故障容错能力,同时减轻了时序电路引起的错误累积,可以成功避免域交叉错误的出现。图 2(a)表示的原始电路,利用有向图表示方法将原始电路分割开来如图 2(b)所示,利用 TMR 三模冗余技术将其容错化如图 2(c)所示。MV 表示多数表决器(Multiple Voter)在电路时序元件输出之后插入,利用其三模冗余结构,增强了电路容错能力。当 D1 模块的组合、时序电路以及表决器出现故障时,D2 模块和 D3 模块通过多数表决器可以检测到此类故障,并经中断唤醒处理器进行部分动态重构处理,使得 D1 部分重构区域得以自修复。

细粒度的三模冗余容错自修复结构同时降低了时序电路引起的错误累积的概率,可以成功避免域交叉错误的产生。当 D1 模块的 SE2 电路和 D3 模块的 CG4 电路同时出现故障的时候,由于在时序电路的输出端用表决器成功地将 SE2 故障进行检测和隔离,不会传递积累影响下一级的 CG4 错误,因此可以成功避免域交叉错误的产生。

2.3 可靠度对比

功能模块在 FPGA 内部的实现可以用逻辑资源来表示,如查找表(LUTs)、触发器(Flip-Flops)、块存储器(BRAM)等。而各逻辑资源的连接和使用通过比特流文件配置来实现。比特流文件由若干个配置帧(frame)组成,配置帧又包含若干个表示配置信息的比特位。在辐射环境中,当 FPGA 中的电路模块发生单粒子翻转效应时,并不是模块任意比特位发生翻转就会导致模块功能失效,该模块功能往往由一些关键比特位所决定。考虑该粗粒度的三模冗余设计结构的容错能力,讨论马尔科夫模型下的三模冗余结构[15],假设功能模块在时间 t 内功能正常的可靠度随着时间的推移呈指数递减,其可靠度可以表示为:

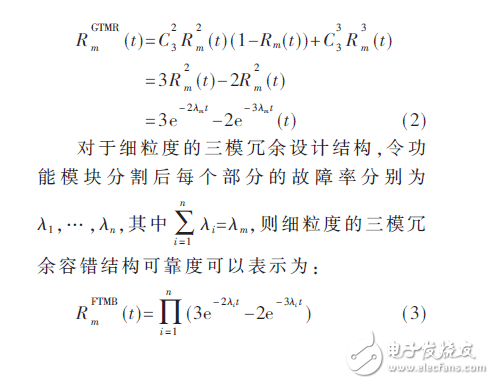

其中λm 表示功能模块 m 的故障率,其由比特位在单位时间内的翻转速率和模块对应的关键比特位数量所决定。对于一个三模冗余系统来说只有当两个或者两个以上的模块发生错误时系统防护功能才会失效,假设三模冗余系统表决逻辑功能正常,那么对于该粗粒度的三模冗余设计结构其可靠度可以表示为:

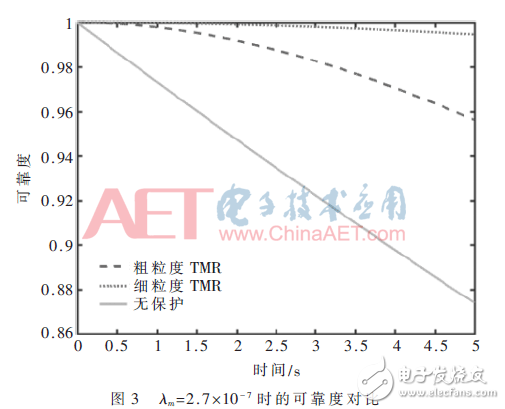

将提出的细粒度的三模冗余结构和粗粒度的三模冗余结构的可靠度进行比较,其可靠度示意图如图 3 所示。细粒度的三模冗余结构容错可靠度相对于粗粒度的可靠度有显著的提高,但同时细粒度的三模冗余结构会引入额外表决器和故障检测逻辑,导致额外资源开销的增加。细粒度的三模冗余结构更适用于对故障率高的电路模块进行防护。

3 实时故障自修复系统设计

3.1 实时故障自修复系统整体设计结构

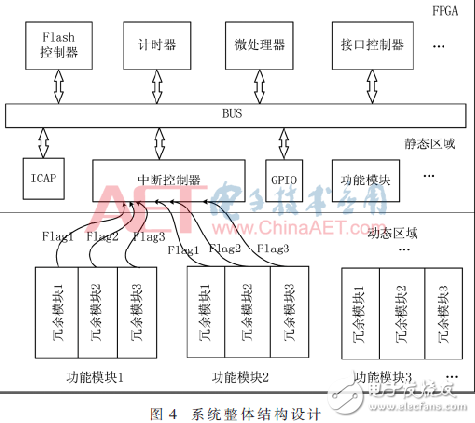

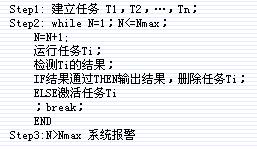

图 4 给出了一种基于 Xilinx FPGA 实现的故障自修复系统整体结构设计方案。整个系统实现基于 MicroBlaze 软核的片上微处理器系统,主要划分为两个部分:静态区域和动态部分重构区域。静态区域主要包括:软核 MicroBlaze、串口控制器、Flash 控制器等,这部分区域包括了整个关键处理模块不适于动态重构的模块,主要负责运行低优先级程序和检测动态重构区域的正常运行。动态部分重构区域是整个电子系统自修复的基础,所有的自修复操作都在其他模块监测、控制下有序地进行,保证整个电子系统不间断正常的工作,其中各个冗余模块的标准配置文件存放于片外 Flash 中。当系统收到重构请求时,由 Flash 控制器读取片外存储器中对应模块的比特流文件并通过内部配置访问端口(ICAP)写入重构区域。动态部分重构区域结合上文提出的容错方案进行容错设计,同时 MicroBlaze 负责控制和监测每个动态重构单元的工作情况:比如当设计动态重构单元为三模冗余故障容错模块时,当此模块内部故障检测单元检测到发生故障时,通过中断的形式将信息发送到 MicroBlaze 中,MicroBlaze 读取此模块的状态寄存器以判明故障类型和区域,根据应用场合不同选择不同的故障自修复策略将此模块进行有序的自重构,实现故障自修复的同时并不影响系统正常运行。

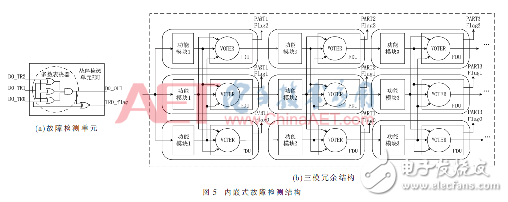

3.2 内嵌式故障检测结构

采用一内嵌式故障检测结构对冗余模块进行故障检测,该方案将故障检测单元嵌入到冗余模块中。图 5(a)所示为三模冗余容错自修复结构中以逻辑门描述的故障检测单元示意图,该故障检测单元由多数表决器和异或非门构成,将多数表决器的输出和检测的冗余模块的输出接到异或非门的输入端,多数表决器的输出作为错误标志信号 FLAG。当检测的冗余模块的输出和表决器的输出相同,则异或门输出为逻辑 1,表示该检测的冗余模块无故障发生,若异或门输出逻辑为 0,则表明检测的冗余模块发生故障或故障检测单元自身发生故障。具有该故障检测单元的三模冗余结构如图 5(b)所示。

功能模块在 FPGA 内部的实现可以用逻辑资源来表示,如查找表(LUTs)、触发器(Flip-Flops)、块存储器(BRAM)等。而各逻辑资源的连接和使用通过比特流文件(Bitstream)配置来实现。比特流文件由若干个配置帧(frame)组成,功能模块大小也可通过配置帧的数量来表示。

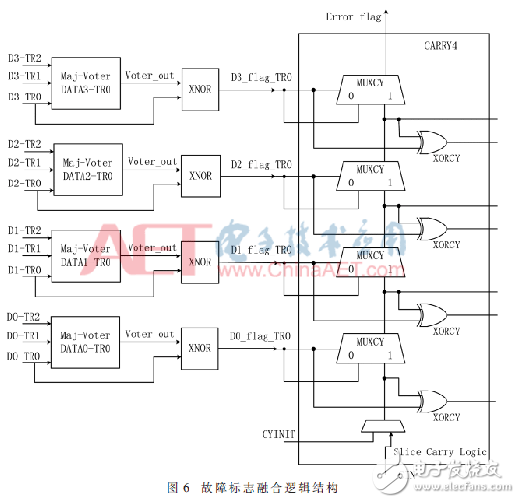

该检测单元从细粒度的角度对电路输出的每一位进行比较,也就是说对于一个输出信号为 N 位的功能模块来说,采用该故障检测单元会对每一个冗余模块会产生 N 个故障标志信号。然而对于一个冗余模块来说只需要一个标志信号来表明该模块是否发生故障。对此提出了一种将标志信号进行融合的逻辑结构,该融合逻辑结构采用 FPGA 片内进位链逻辑来实现。如图 6 所示,以 4 位的输出信号为例,故障检测单元对 TR1 模块的输出位进行检测,将故障标志信号分别接入进位链的 C0~C3 端口。进位链 CIN 端口输入逻辑 1,当无故障发生时进位链输出逻辑 1,当其中一位或者多位错误发生时,进位链中的二选一选择器选择故障标志信号进行传递,进位链输出逻辑 0,表示 TR1 模块发生故障。对于模块输出信号位数少于 4 位的情况,可以将进位链空闲的输入端输入逻辑 1 即可。对于模块输出信号位数大于 4 位的情况,可以将前一进位链的标志输出 FLAG 接入后一进位链的 CIN 输入端,将进位链串行连接。

4 实验设计与分析

本节中将上文提出的故障自修系统在 Xilinx XC6VLX240T-1FF1156 FPGA 上进行设计实现,实验中静态区域包含了一基于 MicroBlaze 核的片上微处理器系统,该微处理器系统主要负责与上位机进行交互、响应重构请求、控制片外存储器读取比特文件数据和控制内部配置访问端口(ICAP)对重构区域进行重配置等任务。动态区域中将 ITC99 benchmark 电路中 8 个不同粒度的标准电路进行冗余设计,以分析不同粒度模块的故障自修复时间。

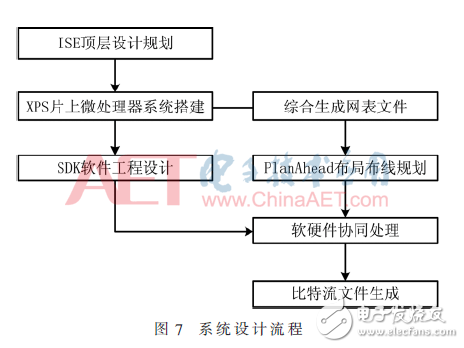

4.1 FPGA 系统设计流程

实验中对系统进行设计实现采用的是基于 Xilinx ISE 开发工具的设计流程,设计流程如图 7 所示。在 ISE 顶层设计规划中对系统各模块进行划分,定义系统中的各静态模块和动态模块,并对动态模块进行冗余保护设计。片上微处理器系统在 Xilinx 的 XPS 设计工具中进行设计搭建,并在 SDK 设计工具中对微处理器系统进行软件功能编译,PlanAhead 设计工具可通过图形界面(GUI)对 FPGA 进行早期分析和布局规划功能,施加物理约束,分析布线和时序的结果。实验中各动态模块的区域划分在 PlanAhead 中进行设计。PlanAhead 中比特流文件生成完成后,需要进行软硬件协同处理,即将 XPS 生成的块存储器映射文件(*.bmm)、SDK 生成的可执行文件(*.elf)和 PlanAhead 生成的全局比特流文件合为一个新的比特流文件,借助 Xilinx 命令行工具 ISE Design Suite Command Prompt,通过命令指令合成最终的比特流文件。

4.2 实验结果分析

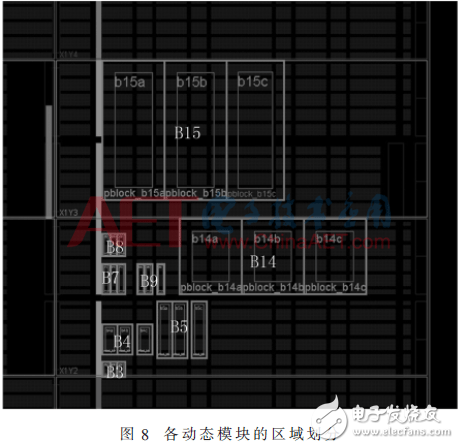

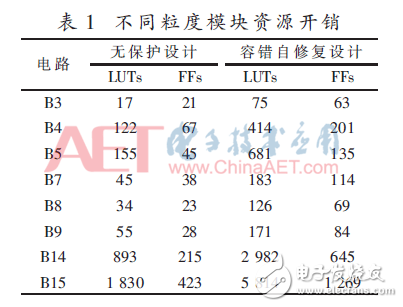

实验中各动态模块的区域划分如图 8 所示,动态区域内的逻辑资源能够满足各模块功能实现。各动态模块的资源开销如表 1 所示,由实验结果可知,模块粒度越小其冗余设计中表决器和故障检测结构所占的资源比例则越大,即系统模块粒度划分越小、重构区域划分越多,则容错自修复设计所带来的额外资源开销越大。

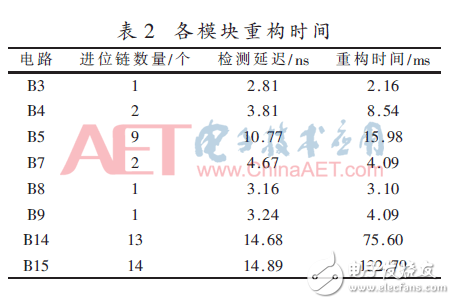

各动态模块重构时间花费表 2 所示。实验中所采取的故障注入方式同样采取动态重构方式,即通过 FPGA 的内部配置访问通道(ICAP)动态地对各模块进行错误配置来实现。实验中故障检测方案采用上文所提出的内嵌式故障检测结构,其故障检测延迟与信号在进位链中的传播延迟相关,即和进位链的串联个数相关,而进位链中信号传播延迟为纳秒级,远小于模块重构时间,可认为模块的自修复时间近似于模块的重构时间。由实验结果可看出模块重构时间与模块占用资源数和模块重构区域大小成正比,即模块占用资源数越多,其划分的最小重构区域则越大,模块重构时间花费越大。而同时,功能模块划分越小,其进行冗余设计时所带来的额外资源开销比例则越大。故在系统设计时,需要综合考虑资源分配情况和故障修复时间要求,合理地进行模块粒度划分,实现粗粒度和细粒度的灵活组合。

5 结论

本文提出了一种基于 SRAM 型 FPGA 的实时容错自修复系统结构和设计方法。该设计方法将系统分为若干功能模块,采用粗粒度三模冗余结构和细粒度三模冗余结构并结合动态重构对系统进行容错自修复设计,实验结果表明该设计结构下故障修复时间短,系统的可靠性得到有效提高。在系统设计时,可以综合考虑资源分配情况和故障修复时间要求,合理进行模块粒度划分,实现粗粒度和细粒度的灵活组合。

电子发烧友App

电子发烧友App

评论