0 引言

随着现代检测技术和科技水平的高速发展,信号采集技术的应用范围越来越广泛[1]。与此同时,对信号采集系统的采集精度、采样率以及便携性等设计需求提出了更高的要求。现场可编程门阵列(FPGA)具有逻辑门充足、时钟频率高、速度快、效率高和IP核丰富等特点,使其成为高速信号采集系统设计的一个有效手段[2-3]。针对当前信号采集系统的设计需求,本文主要介绍如何提高信号采集系统的采样率和便携性。

目前,信号便携式信号采集系统采样率低主要受限于信号采集系统的传输速度和处理速度不足。查阅近几年的相关文献,基于FPGA的信号采集系统主要有以下两种设计方案:方案一,采用FPGA作为逻辑控制模块,搭配ADC采集模块和USB2.0传输模块[4];方案二,同样采用FPGA作为逻辑控制模块,搭配DDR2/DDR3模块对ADC模块采集的数据进行高速缓存[5-6]。方案一受限于USB的传输速度其采样率较低[7-8];方案二虽然可以达到较高的采样率,但是具有数据易失、存储容量小的问题,便携性不足[9]。

针对以上问题,本文结合目前NAND Flash高速存储的特性,提出了便携式高速信号采集系统的设计方案。该设计的关键在于利用存储芯片写入速度快、数据总线可复用等特点,使ADC采集到的信号采用DMA方式存入存储芯片中。其次,该设计配置LCD显示屏,用于信号的实地查看,减少了上位机的配置。系统满足长时间、多批次的信号采集。

1 系统总体设计方案

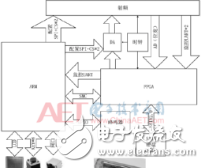

根据功能和原理,该系统分为4个模块:基于FPGA芯片的逻辑控制模块、以ADC芯片为主的数据转换模块、以NAND_Flash芯片为核心的高速数据存储模块以及LCD触摸显示屏模块,如图1所示。

系统基本工作原理:首先,模数转换模块在接收到模拟信号后,将信号转换为数字信号并发送到FPGA逻辑控制模块中的FIFO中;其次,FPGA逻辑控制模块采用直接存储器存储(Direct Memory Access,DMA)模式将数据从FIFO中传递到NAND_Flash数据存储模块;然后,NAND_Flash模块结合其相应的内部结构以同步的方式进行高速数据存储;最后,将由LCD模块发送相应的指令,以一定速度读取数据,经过FPGA进行一定的信号处理,在LCD显示屏中显示。

2.1 FPGA逻辑控制模块

FPGA逻辑控制模块由ALTERA公司的EP4CE40F29C8N、EPCS64SI16以及海力士公司的H27U1G8F2B芯片组成。其中EP4CE40F29C8N为Cyclone IV系列FPGA芯片,该芯片最大时钟频率为472 MHz,具有533个IO接口,满足系统设计所需的最大时钟频率以及外设连接接口。逻辑控制模块由顶层设计部分、系统时钟与复位部分、采集控制部分、存储控制部分、LCD显示控制部分以及NISO II部分构成,其中顶层设计部分负责各个部分的连接以及逻辑控制模块与其他模块的接口。FPGA顶层原理图如图2所示。

在系统时钟与复位部分,由FPGA芯片系统时钟接口通过连接25 MHz无源晶振获得25 MHz时钟信号,通过“PLL”IP核将25 MHz时钟信号倍频为33 MHz、50 MHz、100 MHz以及200 MHz,以此作为系统的时钟电路。其次,产生异步复位同步释放的系统复位信号。

LCD显示控制部分由波形模块、数据缓存模块、LCD显示驱动模块和触摸屏指令接收模块组成。该部分提供接口将QSYS中的显示数据输出到DDR2缓存模块中;并为DDR2芯片和LCD显示芯片建立DMA通信机制,实现显示数据的输出。

通过QSYS系统集成开发工具建立NIOS II片上嵌入式处理系统,负责信号采集系统指令接收和程序执行控制。NIOS II系统完成以下工作:(1)系统初始化程序执行,监听LCD指令输入;(2)实现配置Flash芯片(H27U1G8F2B)的读写操作,配置Flash芯片中存放显示模块中的背景图片、字体库以及采集过程中采集批次编号和采集数据存储的起止位置信息;(3)实现采集数据读取操作,并将采集的信号数据转为波形显示数据;(4)负责系统各个外设驱动指令的输出。

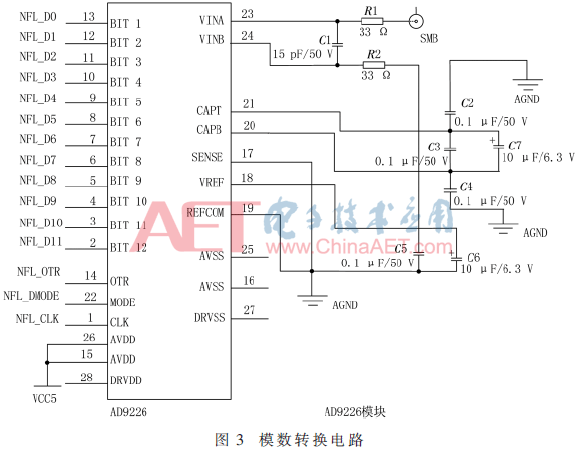

2.2 模数转换模块

模数转换电路采用AD9226作为转换芯片,该芯片是一款低功耗(475 mW)、高精度(12 bit)的高速模数转换芯片,其最高转换速率为65 MSPS,并且具有良好的信噪比(70 dB)。本设计中,信号输入范围为1 V~3 V。该模块的采样时钟由FPGA逻辑模块提供,以达到对采样率的控制,本文中所有测试内容中采样率均为50 MHz,模数转换模块电路图如图3所示。

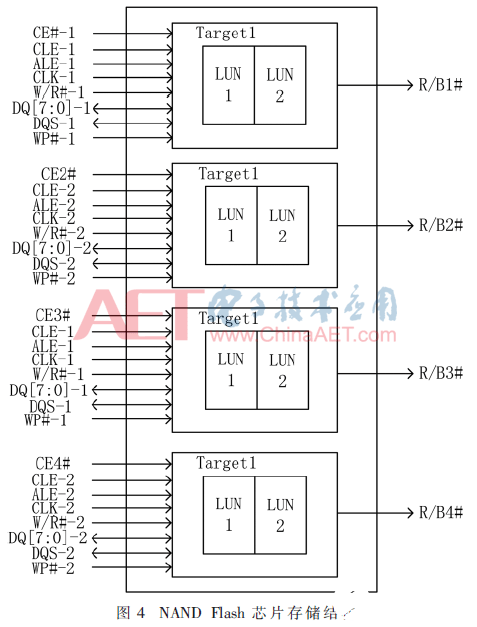

2.3 高速数据存储模块

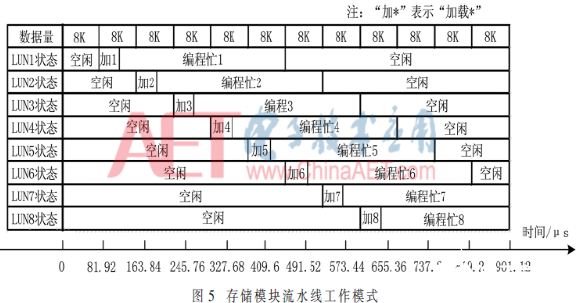

为了匹配高速采样率,高速数据存储模块选取SLC颗粒的NAND Flash芯片[10]。本设计选择Micron公司的MT29F256G08AUCABH3芯片,该芯片在同步状态下,引脚读写速度可以达到200 MT/s,并且在数据写入过程中采用DDR模式,即在时钟的上升沿和下升沿均有数据写入。通过对其数据手册的分析,由于NAND Flash需要进行PROGRAM PAGE 操作,因此该芯片写入1页数据(8 KB)大约需要400 μs。在该时间段内,AD信号采集模块采集数据4×104 B,远大于NAND Flash存储数据,无法满足系统的设计需求。考虑到NAND Flash芯片在同步写入过程中加载8 KB数据需要40.96 μs,模数转换模块采集8 KB数据需要81.92 μs。影响系统存储时间的主要因素是NAND Flash的编程时间(350 μs)。

针对这一问题,本设计结合MT29F256G08AUCABH3的存储结构特点,如图4所示。该芯片内部具有8个LUN结构,且当一个LUN处于编程状态时,其他LUN可以进行读写以及编程。根据这一特性,本设计将其内部的8个LUN芯片采用流水线方式排列,依次进行数据的存储操作,如图5所示。当采集数据达到8 KB,处于写准备状态的LUN开始以DDR方式进行数据写入。完成1页数据(8 KB)的写入后,后一LUN进入写准备状态,等待未存储数据再次达到8 KB。以此方式进行循环,当第8个LUN完成写操作时,第一个LUN完成编程过程,处于空闲状态可以进行写操作,图5所示为存储芯片流水线工作模式。

2.4 显示模块

在系统的显示模块,选用一款具有800×480分辨率和数字接口驱动的7英寸LCD液晶显示屏。显示屏的输出色彩信号通过565的RGB并口数字信号传输,搭配容量为512 MB的DDR2 SDRAM芯片用于缓存显示数据。系统显示模块的时钟频率为33 MHz。

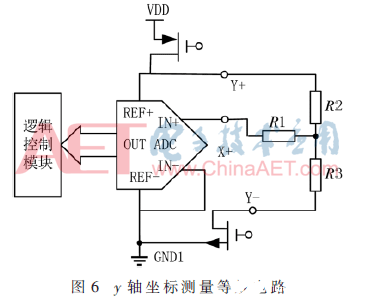

除显示功能外,该模块同时肩负人机交互功能。利用触摸屏的特性,完成对整个系统的操作控制,减少键盘模块,使操作更加简单。本设计采用电阻式触摸屏,屏幕的x轴和y轴各有两条信号线连接到触摸屏专用AD芯片上(本设计选择AW2083芯片),每次按触摸屏时,会在对应的x轴和y轴产生一个阻值。在两条坐标轴的正负极之间加参考电压,当其中一条坐标轴的某一位置被触按,则这个位置和对应坐标轴的正负极之间的电阻会通过电压的形式反馈给ADC的输入端,产生12 bit的AD量化值,AD芯片采集到的坐标数据与实际坐标值成正比,且为线性关系。图6所示为y轴坐标测量等效电路图。

3 系统程序逻辑设计

当系统上电后,系统进行初始化操作。FPGA读取配置NAND Flash芯片中系统的配置信息。获取显示模块的初始化界面并进行输出和显示,同时从配置芯片中获取存储模块下一存储地址。系统初始化完毕后,系统进入待机状态,并监听LCD显示模块的指令输入。

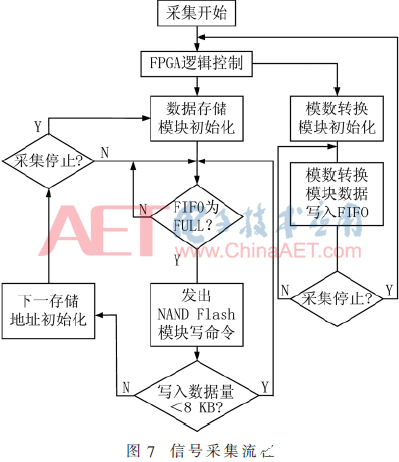

3.1 信号采集流程

通过点击LCD模块中的“开始采集”按钮,触发信号采集程序。逻辑控制模块监听到信号采集开始指令,系统进入信号采集流程。

信号采集流程:

(1)高速存储模块初始化,对上一批次结束的所在LUN的下一个LUN进行存储状态激活。

(2)逻辑控制模块发送模式转换模块使能信号,同时向模数转换模块输入50 MHz时钟信号。

(3)模数转换模块开始工作,将输入的模拟信号以50 MS/s的转换率转换为12 bit的数字信号,并输出到逻辑控制模块。

(4)逻辑控制模块接收到12 bit后,将其左移4位与当前采集批次的4 bit二进制值相加产生一个16 bit存入FIFO中。FIFO设置为输入信号16 bit,频率50 MHz;输出信号为8 bit,输出信号频率为400 MHz;深度为4 096 words。

(5)当FIFO状态为“FULL”时,逻辑控制模块向高速数据存储模块发生写指令,向FIFO发送读指令,系统开始以DMA的方式将数据从FIFO中发送到高速数据存储模块。

(6)当完成page数据的存储后,逻辑控制模块关闭FIFO读使能。高速数据存储模块激活下一个LUN的存储状态,重复步骤(5)~(6)。信号采集流程图如图7所示。

3.2 信号采集停止流程

LCD显示模块中的“采集停止”按钮被触发,逻辑控制模块等待数据采集流程中步骤(6)执行时,关闭高速数据存储模块、模数转换模块使能,将当前采集批次编号和对应数据存储的起止位置存入配置信息存储Flash中。系统进入待机状态,监听LCD显示模块的指令输入,同时LCD显示模块初始化界面。

3.3 波形显示流程

LCD波形显示按钮触发后,界面切换到采集批次选择界面,通过点击选择对应批次的波形显示,进入波形显示操作流程。

波形显示流程:

(1)逻辑控制模块从配置Flash中读取相应批次数据采集的存储起止位置。

(2)读取高速存储模块中对应地址的数据,写入波形控制IP核中。波形控制模块负责控制LCD波形窗口控制,并将采集数据值锁存到双口RAM中,同时负责输出波形点显示坐标位置和波形显示时钟频率。

(3)将波形控制模块中的数据输入到LCD显示模块中的DDR2芯片中。

(4)LCD显示屏中,读取DDR2中的数据,进行显示。

(5)当对应批次的所有数据读取完毕后,波形显示流程结束。

3.4 高速数据存储控制流程

高速数据存储控制程序主要分为采集数据写流程和显示数据读流程。本设计中,采集数据写流程采用同步写入方式,工作频率为200 MHz;显示数据读流程采用异步读取方式,工作频率为50 MHz。

(1)高速数据写流程:①NAND Flash芯片激活同步读写状态;②从逻辑控制模块获取写入页地址;③向NAND Flash发送写操作命令;④向NAND Flash写入写操作地址;⑤NAND Flash等待数据写入使能;⑥接收到逻辑控制模块发送的写使能,开始写入数据;⑦当数据写满一页时,该LUN进入编程状态,同时从逻辑控制模块获取下一个LUN的存储地址,重复步骤③~⑦。

(2)高速数据读流程:①NAND Flash芯片激活异步读写状态;②从逻辑控制模块获取读取页地址;③向NAND Flash芯片发送读操作命令;④向NAND Flash写入多操作操作地址;⑤读取NAND Flash数据发送到逻辑控制模块中;⑥当数据读完一页后,重复步骤②~⑥。

4 实验测试

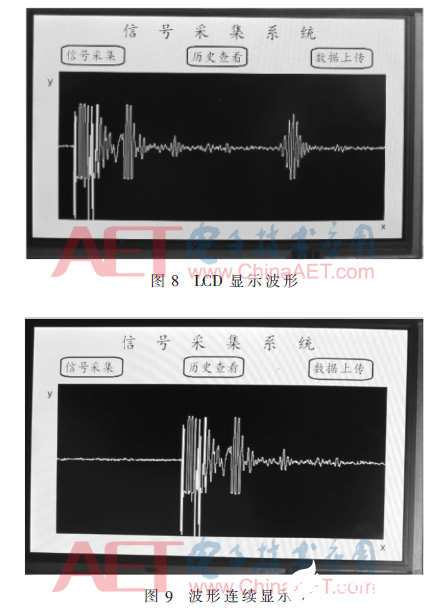

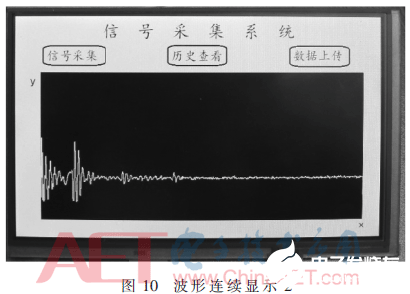

测试平台由超声发射电路、超声接收电路、超声探头和有焊缝的金属薄板构成。超声探头发射2.5 MHz的超声信号到金属薄板。当超声信号到达焊缝部位时,信号发生部分或全部反射,产生回波信号。信号采集系统通过超声接收电路采集回波信号,经过逻辑控制模块处理后,写入存储模块。同时,经过处理的数据通过LCD显示屏进行显示。图8为信号检测系统输出波形。对比两个波形发现,系统能够以50 MHz的采样率进行良好的采样。图9和图10为连续采样数据波形输出,实现了连续多批次信号采集。

5 结束语

本系统通过AD9226高速模数转换模块,将采集到的模拟信号转换为数字信号,经过FPGA存储到大容量NAND Flash中,并在LCD显示屏中显示波形。在实际应用中,该系统能够进行持续长时间的多批次高速信号采集,并具有小型化、易于携带的特点。

参考文献

[1] 张晓威,苏淑靖。基于FPGA的高速高精度数据采集系统的设计[J]。仪表技术与传感器,2016(1):70-72.

[2] BAO S,YAN H,CHI Q,et al.FPGA-based reconfigurable data acquisition system for industrial sensors[J].IEEE Transactions on Industrial Informatics,2017,13(4):1503-1512.

[3] 杨海钢,孙嘉斌,王慰.FPGA器件设计技术发展综述[J]。电子与信息学报,2010,32(3):714-727.

[4] XU Z,ZHU L,SHAN J F,et al.A new high-speed data acquisition system[J].Journal of Fusion Energy,2015,34(3):1-4.

[5] 黄远望,严济鸿,周伟。基于FPGA的数据采集测试系统设计[J]。现代雷达,2015,37(4):73-76.

[6] KHEDKAR A A,KHADE R H.High speed FPGA-based data acquisition system[J].Microprocessors & Microsystems,2016,49:87-94.

[7] 李茂,杨录,张艳花。基于FPGA和USB的多通道超声检测系统设计[J]。仪表技术与传感器,2017(8):82-84.

[8] 孟晓东。基于FPGA的DDR3控制器设计与验证[D]。长沙:国防科学技术大学,2012.

[9] LIU D,WANG Y,QIN Z,et al.A space reuse strategy for Flash translation layers in SLC NAND Flash memory storage systems[J].IEEE Transactions on Very Large Scale Integration Systems,2012,20(6):1094-1107.

[10] 肖佳。基于NANDFLASH的大数据高速存储系统的设计与实现[D]。西安:西安电子科技大学,2014.

电子发烧友App

电子发烧友App

评论