采用基于IP复用技术进行设计是减小这一差距惟一有效的途径,IP复用技术包括两个方面的内容:IP核生成和IP核复用。文中采用IP核复用方法和SOC技术基于AVR 8位微处理器AT90S1200IP Core设计专

2012-01-12 14:22:47 1825

1825

MIL-STD-1553B标准,针对电气参数测试、协议兼容性测试、噪声抑制测试三大方面,制定了包括测试目的、连接结构、测试内容和通过准则等内容的测试细则,可有效而全面地解决1553B总线产品设计定型前

2014-01-20 16:01:40

IP 核可交付成果 当一家公司购买 IP 核的许可时,它通常会收到在自己的产品中设计、测试和使用该核所需的一切。IP核设计通常以硬件描述语言HDL提供,类似于计算机软件程序。还可以提供逻辑和测试

2022-02-18 21:51:20

想请教各位前辈,wishbone在工作中很常用吗?我最近在学关于这个的代码,感觉很难懂,而时间又感觉不大够用,需要重点攻击, 所以想知道是否值得投入大量的时间去研究它。望各位前辈不吝赐教

2014-03-02 23:37:04

由于桌面Windows绝大多数情况下运行于X86平台上,也就不存在不同平台的可移植性问题。然而Windows CE运行在四大架构(X86,SHx,MIPS,ARM)的CPU上,编写应用程序时就需要考虑它的移植。

2020-03-05 06:57:17

有效地址是什么?形式地址又是什么?有何区别?补码加减法是指什么?

2021-07-16 11:33:33

协议的正确执行,具体来说,就是把TCP/IP协议的处理工作放到主程序中对网络接口的控制芯片采用循环查询方式,在其他中断任务的执行间隙处理TCP/IP协议,以牺牲系统的响应时间换取系统的可靠性,再者由于

2019-04-28 09:57:18

的数据包,该ARP请求就是因为要发送这个包而发送的。这种方法在假设上层会重发被覆盖的数据时采用。每隔十秒钟,表就会刷新一次,旧的记录被丢弃,在嵌入式TCP/IP协议栈中,记录的有效时间为1秒。 2.2.2

2019-04-23 07:00:10

IP核来实现PCI接口,利用基于PCI协议的IP核来实现PCI接口,这种设计开发速度较快,灵活性较好,但是IP核价格昂贵。采用FPGA实现PCI总线协议。采用CPLD/FPGA等可编程逻辑器件实现PCI

2019-05-30 05:00:02

定义的DSP扩展总线,电平转换电路用来使DSP的3.3V电平与外部5V电子协调。而另外一个组件--仿真接头用来接上普通PC机,以进行仿真调试。3可移植性基本设计 在设计DSP小系统总线时充分考虑了

2018-11-26 11:21:21

FPGA详细教程_IP复用

2012-08-16 20:36:05

针对GPS测量系统数据传输过程中的安全问题,采用FPGA技术设计了GPS数据加密系统。系统移植MD5算法到NIOS中对系统口令加密,并设计DES IP对GPS数据加密。实验表明,该设计可有效防止GPS数据被非法窃取,具有安全性强、速度快、操作简便等特点。

2019-08-22 06:03:00

划分为几个主要模块,分别介绍各个模块的功能,用VHDL语言对其进行描述,用FPGA实现并通过了仿真验证。该IP核具有良好的移植性,可驱动不同规模的LCD电路。 关键词:LCD;驱动电路;IP 引言

2012-08-12 12:28:42

我想在 MPC5644A 的 ADC0 上连续扫描 24 个通道(外部复用)。是否可以将 6 个 CFIFO 配置为好像它们在一个大型命令 FIFO 中一样,然后在最后一次转换时获得 EOQ 中断并自动从通道 0 重新开始?如果不是,那么在没有DMA 的情况下有效地进行这种转换的推荐方法是什么?

2023-04-03 06:36:15

本IP模块具有很强的通用性和可移植性,能提高设计效率,降低产品成本。【关键词】:现场可编程门阵列;;串行数据接口;;SDI;;IP模块【DOI】:CNKI:SUN:DSJS.0.2010-02-007

2010-04-22 11:54:44

针对上篇文章对于程序可移植性不强的问题进行优化,基本思路是首先搭建好IIC底层驱动程序,该程序可用于任何IIC通讯设备,然后针对不同的IIC设备单独编写应用程序,本篇文章仍以SHT30为例。一

2022-02-21 06:19:19

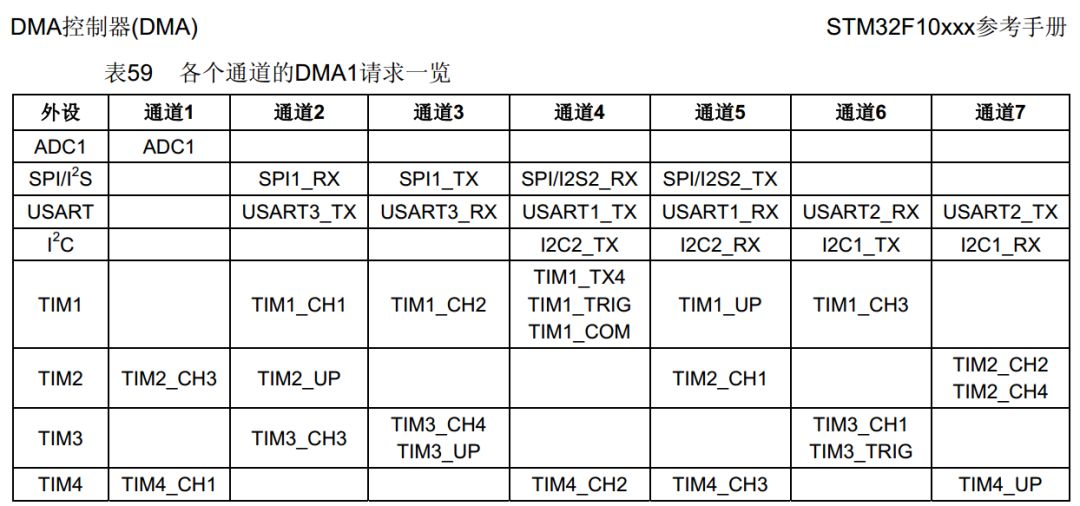

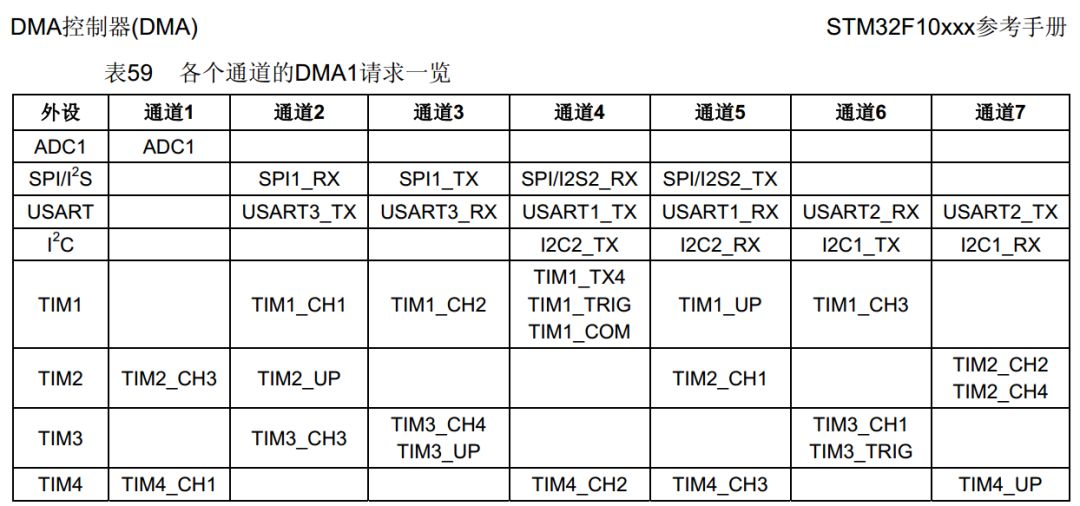

STM32如何有效地接收数据呢?

2021-12-03 07:32:27

嵌入式操作系统的可移植性创易电子整理出品,创易更懂电子, http://52edk.taobao.com/ 全系列阻容感一本全掌控。许多操作系统夸耀自己的可移植性时,爱这样说

2010-03-16 22:11:07

:一线研发之声:嵌入式C编程经验 之 请写可移植性高的模块* Author:SedateFire E-mail:SedateFire@126.com* Version:1.000 Time

2012-07-22 14:44:18

stm32如何有效地接收数据?

2021-12-06 07:32:17

μC/OS-II操作系统是一种抢占式多任务、单内存空间、微小内核的嵌入式操作系统,具有高效紧凑的特点。它执行效率高,占用空间小,可移植性强,实时性能良好且可扩展性强。采用μC/OS-II实时操作系统

2019-10-14 07:31:48

:一线研发之声:嵌入式C编程经验 之 请写可移植性高的模块* Author:SedateFire E-mail:SedateFire@126.com* Version:1.000 Time

2012-02-05 21:31:07

。随着IC产业的迅速发展,传统的、基于标准单元的数字IC设计方法已经发展到基于IP(知识产权)复用的SoC设计方法,根据实现的硬件描述级的不同,IP核分为软核、硬核和固核。其中,软核是采用可综合的HDL

2018-12-04 10:35:21

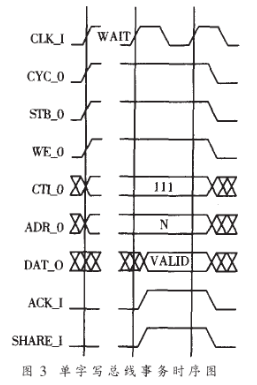

引言随着半导体技术的发展,深亚微米工艺加工技术允许开发上百万门级的单芯片,已能够将系统级设计集成到单个芯片中即实现片上系统SoC。IP核的复用是SoC设计的关键,但困难在于缺乏IP核与系统的接口标准

2019-06-11 05:00:07

WISHBONE总线,所以本设计的接口具有可移植性。 Am29LV160D芯片特点Am29LV160D是一种仅需采用3.0V电源进行读写的闪存。该器件提供了70ns、90ns、120ns读取时间,无需高速微处理器

2018-12-05 10:35:32

的IT标准,可以集成到现场总线系统中• PROFINET被IEC规范IEC 61158和IEC 61784标准化拥有低资源消耗、可用和不用操作系统、高度可移植性• 提供最好的条件用于PNO一致性测试• 提供嵌入式μIP UDP/IP栈• 支持几乎所有TCP/IP栈,通过通用和原生UDP socket连接

2023-09-07 07:10:15

引言 实时操作系统的使用,能够简化嵌入式系统的应用开发,有效地确保稳定性和可靠性,便于维护和二次开发。 μC/OS-II是一个基于抢占式的实时多任务内核,可固化、可剪裁、具有高稳定性和可靠性

2019-07-02 07:51:57

和现代化程度的要求也逐步提高,文中针对机载信息采集系统的可靠性、数据管理的高效性以及硬件成本的需求。设计实现了与Wishbone总线SDX总线的接口转化,完成了数据采集功能模块与SDX总线协议之间

2019-05-31 05:00:07

盖世汽配加油站四--如何有效地把握采购机遇背景 : 在全球性的金融危机蔓延的当下,您是否在为打开国际、国内配套之门而呕心沥血?配套采购的未来发展趋势如何?机会何在?是否在为开拓国际售后市场而绞尽脑汁

2009-08-04 10:48:22

引言在使用stm32或者其他单片机的时候,会经常使用到串口通讯,那么如何有效地接收数据呢?假如这段数据是不定长的有如何高效接收呢?同学A:数据来了就会进入串口中断,在中断中读取数据就行了!中断就是

2022-02-21 06:12:00

;另一方面,已经分配或指配给现有很多无线业务的频谱却在时间和空间上存在不同程度的闲置。那么,如何有效地盘活那些闲置的频谱资源,解决这一制约无线通信发展的新瓶颈?美国科学家Joseph Mitola博士提出了认知无线电(CR)的概念。

2019-08-02 08:21:06

如何利用单片机有效地测量占空比

2015-08-15 12:00:02

在使用msp430芯片时,程序的移植变得尤为重要,可是本人的程序总是不能做到随意移植,想请各位大神请教一下,在编程中要注意哪些问题,可以提高自己程序的移植性呢?望大家不吝赐教,谢谢大家!

2014-07-20 10:51:47

如何更有效地使用可编程时钟器件?设计SERDES参考时钟源面临的挑战有哪些?如何去实现XAUI参考时钟源?

2021-04-20 06:03:53

我们已经介绍了应用单片机的外设功能的结构和使用方法。本期我们介绍更有效地应用单片机而必须的外设功能——“中断功能”。

2021-02-25 08:07:05

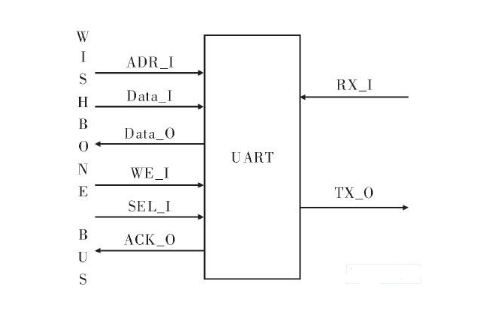

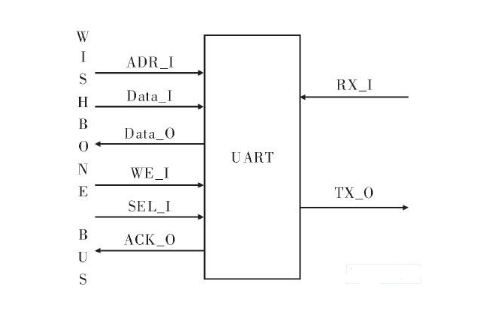

on Chip)是以嵌入式系统为核心,以IP复用技术为基础,集软、硬件于一体的设计方法。使用IP复用技术,将UART集成到FPGA器件上,可增加系统的可靠性,缩小PCB板面积;其次由于IP核的特点

2019-08-20 07:53:46

本文介绍了IP核的概念及其在SoC设计中的应用,讨论了为提高IP核的复用能力而采用的IP核与系统的接口技术。引言随着半导体技术的发展,深亚微米工艺加工技术允许开发上百万门级的单芯片,已能够将系统级

2018-12-11 11:07:21

不出来————小白 如果你存在按键Key和显示Led共用同一个IO时,需要分时复用的需求,则可以移植代码进行使用:代码所占code少于0.5K线程安全,中断安全可移植性高,配置容易注意:系统需要存在一个至少为1ms的时钟中断01 - PCB原理图例程 举2个Key和Led共用IO口的

2021-12-16 07:41:59

你好,我刚刚将ISE 11.1安装更新到11.3。当我尝试运行合成时,我立即收到以下错误消息:FATAL_ERROR:可移植性:PortDynamicLib.c:399:1.32- 由于Das

2018-11-14 10:32:35

,实现设计IP和测试目的的复用,能够显著减少其所消耗的时间成本。这篇文章就是讨论了如何通过前期的计划,针对自身公司的规模和设计需求使用PSS更加正确、有效的通过复用来加速验证过程。

2020-12-18 06:23:31

,导致了软件设计方法学在开放性、可移植性、面向等方面的深刻变革。如今的软件工程,已经成为一门博大精深的科学,有很多系统的方法值得芯片设计业学习和借鉴。根植于软件业面向设计模式的IP技术被认为是最有前途

2018-09-04 09:51:06

请问一下ASIC或FPGA为什么不考虑可移植性?

2021-04-29 06:37:35

,也可以优化多用户之间的调度问题。我们给出了几种在未来无线通信系统中可能采用的闭环MIMO方案,包括基于SVD分解和基于码本的预编码技术,分析并比较了它们的性能。仿真结果表明,闭环MIMO技术将有效地提高通信系统的性能。

2019-07-15 07:34:21

以 IP(Intellectual Property )核复用为基础的SoC(System on a Chip,简称SoC)设计是以软硬件协同设计为主要设计方法的芯片设计技术。本文从IP 核复用技术、软硬件协同设计技术两个方面

2009-08-10 08:32:17 18

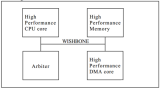

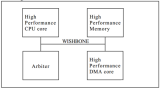

18 介绍了基于IP 的可重用的SOC 设计方法;选用MC8051 IP 核为核心控制器,自主开发了UART IP 核、I2C IP 核、USB IP 核,采用Wishbone 片上总线架构,集成了一个MCU 系统;同时设计了针对此MCU

2009-11-30 15:06:20 33

33 以 FPGA 技术为基础,以Verilog HDL 为载体,设计了遵守Wishbone 片上总线规范的IP 核接口,实现了片上系统的IP 核互联。

2010-01-13 15:09:14 13

13 在SOC设计日趋复杂化的今天,其发展的两大挑战是IP复用技术和IP互联技术,研究IP复用技术对于业界具有重要的现实意义。SPI接口技术是一种高速、全双工、同步的通信总线,

2010-10-20 16:21:54 47

47 如何在射频设计中有效地使用S参数

S参数测量是

2008-07-23 11:36:09 2425

2425 基于CPLD的非多路复用与多路复用总线转换桥的设计与实现

微处理器对外并行总线接口方式一般分为两种,一种为多路复用方式,数据与地址采用共用引脚,分时传输;另一

2009-03-28 15:08:27 753

753

非多路复用与多路复用总线转换桥的设计与实现

提出了一种新颖的非多路复用总线与多路复用总线的转换接口电路。以两种总线的典型代表芯片TMS

2009-03-28 15:14:29 798

798

摘要:提出了一种新颖的非多路复用总线与多路复用总线的转换接口电路。以两种总线的典型代表芯片TMS320F206与SJA1000为例,分

2009-06-20 13:20:32 659

659

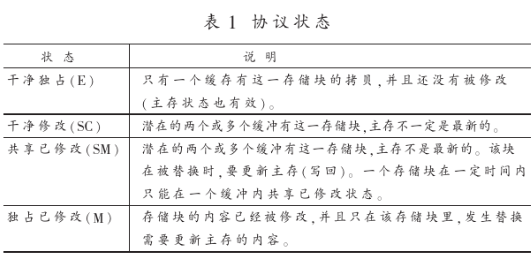

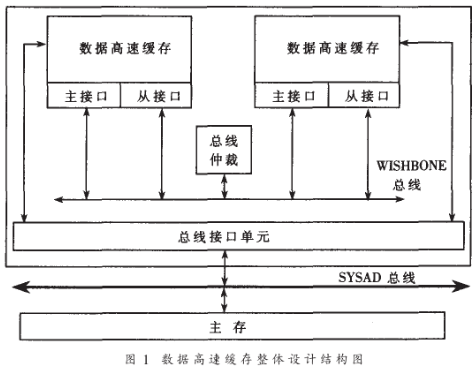

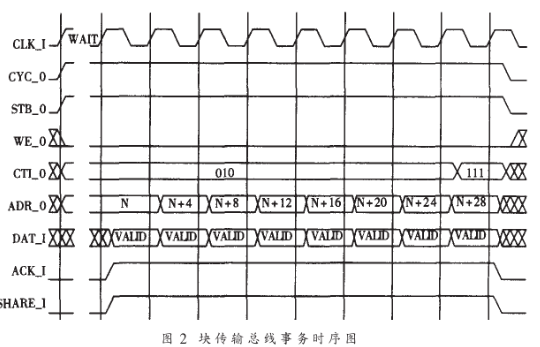

摘要:基于IP可重用的设计方法,利用WISHBONE总线协议,把两个已成功开发出的具有自主知识产权的THUMP内核在一个芯片上,实现了片上多处理器FPGA。开发重点是实

2009-06-20 15:29:35 656

656

移轴镜头实拍技巧4 对纵深的被摄体更有效地合焦

2010-02-01 11:19:00 2479

2479 基于IP复用设计的微处理器FSPLCSOC模块

1 引言

文中采用IP核复用方法和SOC技术基于AVR 8位微处理器AT90S1200IP Core设计专用PLC微处理器FSPLCSOC模块。

随

2010-05-17 08:41:09 1271

1271

由于桌面Windows绝大多数情况下运行于X86平台上,也就不存在不同平台的可移植性问题,以下通过在WinCE系统下访问物理地址,来看看如何编写可移植性较好的应用程序

2011-03-17 11:10:02 1714

1714

本文介绍的基于Wishbone总线的UART IP核的设计方法,通过验证表明了各项功能达到预期要求,为IP核接口的标准化设计提供了依据。此外,该IP核代码全部采用模块化的Verilog-HDL语言编写,

2011-06-10 11:47:37 3479

3479

本文简要介绍了AMD 公司Am29LV160D 芯片的特点,并对WISHBONE总线作了简单的介绍,详细说明了FLASH memory 与WISHBONE 总线的硬件接口设计及部分Verilog HDL 程序源代码。

2011-06-23 16:32:40 18

18 文章采用TOP-DOWN 的方法设计了 AMBA 总线IP 核!它包括AHB 和APB两个子IP 核 所有AMBA结构模块均实现了RTL级建模

2011-07-25 18:10:52 91

91 通用IO接口是Soc系统中非常重要的一种外围端口.本文完成了一种基于WISHBONE总线的GPIO_W B拉制器的逻拜设计和物理实现.文中较其体地介绍了GPIO_W B核的体系结构以及WISHBONE接Q和DMA传偷方式

2011-09-21 16:57:22 32

32 该设计采用了自顶向下的模块化划分和有限状态机相结合的方法,由于其应用了标准的Wishbone总线接口,从而使微机系统与串行设备之间的通信更加灵活方便。验证结果表明,这种新的架构

2011-10-19 15:01:54 27

27 介绍了基于硬件描述语言Verilog HDL设计的SDX总线与Wishbone总线接口转化的设计与实现,并通过Modelsim进行功能仿真,在QuartusⅡ软件平台上综合,最终在Altera公司的CycloneⅢ系列FPGA上调试。实验

2012-01-11 10:21:21 25

25 2013-05-07 16:21:09 4

4 如何有效地管理FPGA设计中的时序问题

2017-01-14 12:49:02 14

14 基于AMBA与WISHBONE的SoC总线桥KBar控制器的设计_陈俊锐

2017-03-19 11:31:31 0

0 由于桌面Windows绝大多数情况下运行于X86平台上,也就不存在不同平台的可移植性问题。然而Windows CE运行在四大架构(X86,SHx,MIPS,ARM)的CPU上,编写应用程序时就需要

2017-10-30 16:05:38 0

0 在众多嵌入式操作系统中,Linux目前发展最快、应用最为广泛。性能优良、源码开放的Linux具有体积小、内核可裁减、网络功能完善、可移植性强等诸多优点,非常适合作为嵌入式操作系统。一个最基本的Linux操作系统应该包括:引导程序、内核与根文件系统三部分。

2017-11-03 12:59:13 2215

2215

引言 随着深亚微米工艺技术日益成熟,集成电路芯片的规模越来越大。数字IC从基于时序驱动的设计方法,发展到基于IP复用的设计方法,并在SOC设计中得到了广泛应用。在基于IP复用的SoC设计中,片上总线

2017-11-30 09:56:51 902

902

由于桌面Windows绝大多数情况下运行于X86平台上,也就不存在不同平台的可移植性问题。然而Windows CE运行在四大架构(X86,SHx,MIPS,ARM)的CPU上,编写应用程序时就需要

2017-12-01 17:10:01 284

284 当用户从PlC32单片机的一种版本迁移至另一版本时,或者在两种不同的PlC32单片机系列之间进行迁移时,使用某些编程技巧将最大化软件的可移植性,本文将论述这些编程技巧。针对如何提高老软件运行在将来

2018-04-20 14:56:20 0

0 本文主要介绍了32位单片机的应用可移植性.

2018-06-28 03:25:00 0

0

当用户从 PIC32 单片机的一种版本迁移至另一版本时,或者在两种不同的 PIC32 单片机系列之间进行迁移时,使用某些编程技巧将最大化软件的可移植性,本文将论述这些编程技巧。针对如何提高老软件

2018-06-21 07:26:00 15

15 支持用户定义的标签。这些标签可以用于为地址、数据总线提供额外的信息如奇偶校验,为总线周期提供额外的信息如中断向量、缓存控制操作的类型等。Wishbone规范只定义标签的时序,而标签的具体含义用户可自行定义。支持用户定义的标签是Wishbone规范区别与其他片上总线规范的重要特征之一;

2018-07-06 08:07:31 2713

2713

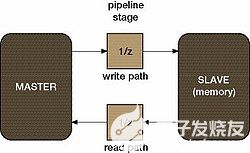

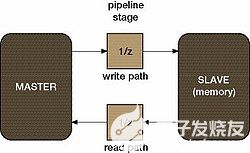

前文曾经指出,Wishbone总线规范是"轻量级(Lightweight)"规范,它实现起来非常简单紧凑,接口需要的互联逻辑非常少。这里给出一个Wishbone从设备的一个例子,如图21所示

2018-07-31 09:11:30 4148

4148

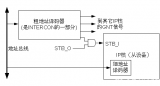

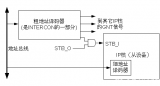

Wishbone部分地址译码的实现如图26所示。对于图中所示IP核,我们假设其只有4个地址,对应4组寄存器。地址译码器首先译码出其地址并给出选择信号,该选择信号与共享总线的STB_O相与输入到IP核的STB_I。而地址总线的最低2位被直接连接到IP核,IP核再根据这两位译码出当前操作选中的是具体哪个寄存器。

2018-08-05 08:44:59 3423

3423

在以上介绍的三种总线中,CoreConnect虽免费不过需要IBM 公司许可,ARM 没有明确的正式说法,可能也会免费,而Wishbone 是绝对免费的。三种总线都是同步的总线,使用时钟上升沿驱图7 8-bit SLAVE输出端口动和采样信号。

2018-08-11 09:14:22 4391

4391

1.6 SimpleLink MCU平台SDK代码可移植性

2019-04-28 06:20:00 3180

3180

用于便携式IP核的WISHBONE1片上系统(SoC)互连结构是一种灵活的设计方法,可用于半导体IP核。其目的是通过缓解片上系统集成问题来促进设计重用。这是通过在IP核之间创建一个公共接口来实现的。这提高了系统的可移植性和可靠性,并缩短了最终用户的上市时间。

2021-01-19 15:23:59 21

21 依据纸吸管机运用越来越普遍,如何有效地搞好日常的维修保养工作上,是一个十分重要的难点。

2021-03-11 09:39:21 602

602 AN-669: 有效地使用AD628精密增益模块

2021-03-19 05:45:25 8

8 的方式来实现。近一段时间,由于芯片的短缺,不得不使用国产非主流单片机来进行项目开发,一个项目需要采用3-4款单片机才能满足量的需求,为了增强程序的可移植性,写了一个通用的呼吸灯实现程序,程序参看第2小节

2021-12-31 18:50:42 7

7 本系列是开源书C++ Best Practises[1]的中文版,全书从工具、代码风格、安全性、可维护性、可移植性、多线程、性能、正确性等角度全面介绍了现代C++项目的最佳实践。本文是该系列的第五篇。

2022-10-10 10:26:54 688

688 可移植性与我们平时所说的跨平台能力比较相近,而软件复用则是一种通过已有软件子件来构建新产品软件的能力。

2022-11-10 09:06:00 832

832 Wishbone B.3总线。以类似的方式,Altera引入了自己的互连方案,称为Avalon Bus,SOPC Builder和Nios(II)系统就是围绕该方案制造的。Xilinx 还推出了自己的总线,称为片上外设总线与处理器本地总线 相结合。

2022-11-14 15:38:55 790

790

在使用stm32或者其他单片机的时候,会经常使用到串口通讯,那么如何有效地接收数据呢?假如这段数据是不定长的有如何高效接收呢?

2023-02-14 09:50:18 2057

2057

为什么CoWoS技术采用了无源硅中介层作为通信层可以有效地减少信号干扰和噪声? CoWoS(Chip-on-Wafer-on-Substrate)技术是一种在集成电路封装中采用的先进技术,它采用

2023-12-07 10:53:38 193

193

电子发烧友App

电子发烧友App

评论