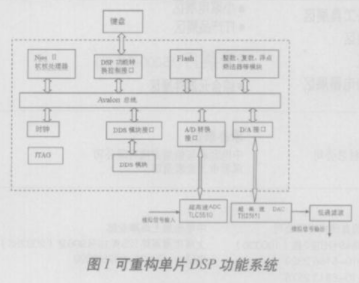

本文主要搭建一个多生理参数测量系统的数据处理平台,在FPGA中嵌入一个32位Nios II软核处理器,用于控制数据的传输、存储及显示。主要完成了此数据处理平台硬件系统的定

2010-08-18 12:10:44 933

933

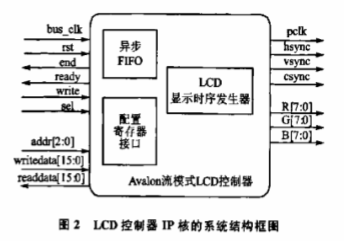

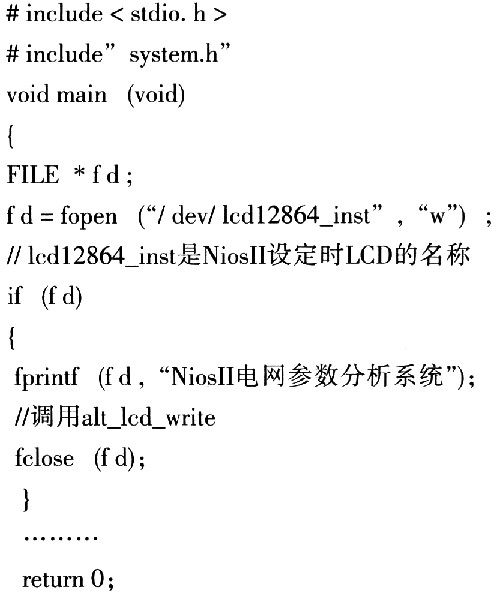

本文介绍了一种基于NIOS II软核处理器实现对LCD-LQ057Q3DC02控制的新方法。在设计中利用FPGA的Altera的SOPC Builder定制NIOS II软核处理器及其与显示功能相关的“软” 硬件模块来协同实现显示控

2011-11-09 11:30:07 2000

2000

仪器、仪表和低功耗电子产品中。本文介绍一种基于NIOSⅡ的LCD的控制方法。利用SoPC技术,在NIOSⅡ系统中添加相应的I/O端口实现对液晶显示器的控制。

2018-10-31 08:04:00 3719

3719

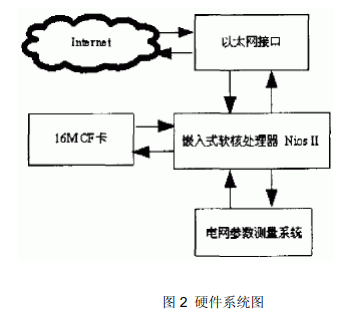

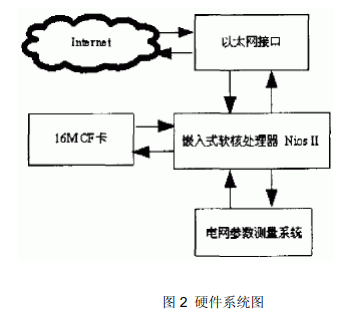

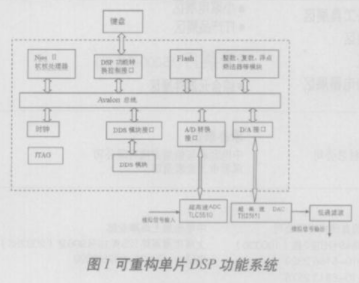

系统的硬件结构如图2所示。硬件系统的核心是构建于Ahera Cyclone FPGA中的Nios II嵌入式软核处理器。Nios II系列嵌入式处理器是一款通用的RISC结构的CPU,它定位于广泛

2020-06-28 14:49:45 540

540

基于μC/OS-II实时操作系统实现多任务管理运行模式,采用Nios II 32位处理器作为LED显示屏控制系统的核心,控制单屏幕多窗口任意显示。整个控制系统在一片FPGA上实现,使用SOPC Builder软

2011-10-02 16:00:21 2366

2366 。 基于NIOSⅡ的矩阵键盘和液晶显示外设组件的设计 本文提出了一种针对LCD控制器和矩阵键盘的IP核的设计方法。该方法利用SOPC Builder中元件编辑器Create New

2015-01-16 22:10:42

,国际上只有I-Shou大学的Yu-Jung Huang等人设计了可驱动不同规模LCD的驱动电路IP核,通过在系统中植入嵌入式微处理器来实现这一功能。但是,这种嵌入式微处理器使系统更复杂,而且成本更高

2012-08-12 12:28:42

NIOS II 软核中EPCS配置芯片的存储操作 最近用CYCLONE FPGA做的视频图像叠加板需要存储一些用户配置信息,而EPCS4配置芯片除了存储FPGA配置信息和NIOS II程序外,还有

2018-07-05 05:58:25

表1 Nios II处理器系统的最大时钟频率(tMAX)(MHz)表2 Nios II处理器系统的MIPS(每秒钟一百万个指令) 表3 在不同设备家族上的Nios II处理器系统的MIPS/MHz比

2018-07-03 02:30:47

问一个问题,为什么配置的PLL的IP核,如图,红框的那个接了输入,在NIOS II中就会出现 [Target Connection]: Connected system ID hash

2016-10-04 21:05:25

,浪费生命。NIOS内核的裁剪问题,编译出来的文件过大,导致Quartus_II软件构造好的on chip memory下载不进去,显示下载elf文件失败elf文件下载失败还有可能与你使用的IP核有关

2017-05-30 14:03:44

个最小系统仅仅需要:1、NIOS II f 或者s 处理器,带硬件乘法器(建议使用NIOS II /f,使用NIOS II/s很慢)2、最小8M的SDRAM3、一个全功能的定时器4、JTAG/UART

2012-02-21 15:55:21

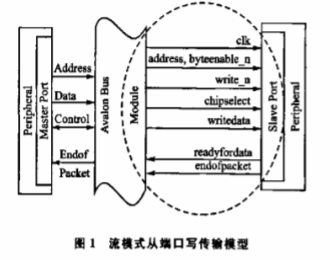

如何与AD采集融合。 查询了一下,发现可以使用Avalon总线,将AD的verilog功能描述封装成一个IP核,挂到Avalon总线,实现verilog与NIOS II的通讯。 但是不知道这种方法速度够不够

2017-11-21 10:11:22

nios ii双核例子nios ii双核例子NIOS II 双核构建的简单例子,希望对大家有所帮助。 1、 实现简易功能 Cpu_0控制pio_cpu_0(输出),令其输出为1。此输出和cpu_1

2012-08-12 15:18:48

可以移植到不同的半导体工艺中去生产集成电路芯片。随着CPLD/FPGA的规模越来越大,设计越来越复杂,使用IP核是一个趋势。 本文研究了ATM流量控制的原理,并给出了一种IP核的实现方法,该IP核不仅可以用于独立芯片,还可以作为系统的一个子模块直接调用。

2011-09-27 11:54:25

用Quartus II 调用IP核时,在哪可以查看IP核的例程

2014-07-27 20:28:04

CAN控制器IP核(可直接在Nios II中使用)

2016-08-24 16:54:21

在其业内领先的低成本Cyclone TM FPGA系列和Nios软核嵌入式处理器成功的基础上,Altera现在推出了第二代产品系列。Cyclone II器件为用户提供更高的逻辑密度和新增硬件性能,比

2019-07-18 07:43:25

FPGA是现场可编程门阵列,是可编程逻辑器件(PLD)的一种。 NIOS II是一种知识产权核(IP Core),是嵌在FPGA内部的处理器软核,相当于在FPGA内部设计了一个微处理器

2018-08-17 09:59:27

的SOPC系统中设计了LCD显示驱动IP核,并下载到Cyclone系列的FPGA中,实现了对LCD的显示驱动。

2019-08-06 08:29:14

很多人都说QUARYUSII中的IP核是收费的,不可以直接用的,其实不然,下面我以FIR滤波器的核的使用来给大家介绍IP核的使用,希望对大家有点帮助。 1.使用 (1)首先建立工程,这个就不

2019-06-03 09:09:51

如题:我之前用Quartus ii 13创建的工程。现在改用17了。想编辑以前的IP核但是找不到MegaWizard Plug-In Manager 了

2017-09-24 21:06:09

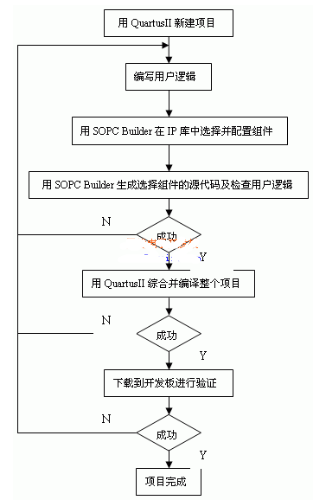

关于QuartusⅡ10.1中NIOS2软核的构建、软件编译及程序固化 一、硬件开发1、构建CPU模块2、构建EPCS控制器,SYSTEM ID模块,JTAG UART模块3、构建RAM模块(1

2022-01-25 07:58:08

LCD上显示,并可通过USB接口将信息拷贝,或通过RS-232接口将信息上传给PC机,也可以通过GPRS将获得的信息方便快捷地发往数据中心作验证。 整个系统的核心部分是内嵌Nios II软核

2018-10-31 16:54:52

用户是可自定制的,具有灵活性和可裁减性等优点。结合内河航道航标管理的实际情况,介绍了一种新的基于Nios II软核的航标监控系统的设计方案。根据系统的运行结果显示,设计实现了系统预期功能,为监控中心能

2015-01-30 11:05:50

基于Qsys + Nios II SBT开发的Nios II教程,内容详细,学习NiosII的同学可以关注下~点击下载

2014-10-13 18:17:58

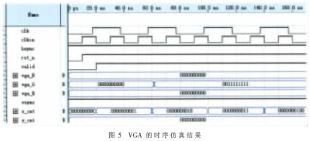

24M的时钟信号,供640*480分辨率的VGA驱动电路使用。NIOS II CPU:实现系统的控制以及显示内容的处理。SDRAM:NIOS II CPU运行内存和TFT显示图像帧缓存

2020-02-26 19:37:23

SPI、定时器、UART串口等IP核,只要在Qsys中添加好这些IP,然后在NIOS II的开发环境(定制版Eclipse)中编写驱动程序和应用程序即可完成该控制器的使用。当然,为了让这些IP用起来

2020-02-24 19:27:02

`附件为小梅哥SOPC公开课第二课NIOS II自定义IP的设计与使用的建随堂工程。小梅哥SOPC公开课第二课主要讲解如何使用Verilog自己编写一个符合NIOS II Avalon MM接口总线

2016-08-13 11:04:32

内部中断需要具备以下几个条件:(1)Status控制寄存器中的PIE位为1; (2)某个中断请求irqn有效;(3)在ienable寄存器中,该中断源相应位为1 当内部中断发生后,Nios II处理器会

2016-10-21 18:31:59

,近期主要深入学习了Qsys系统的硬件部分和软件部分,首先学习了Nios II的硬件框架结构,收获颇丰。 下图是Qsys的系统结构框图: 图中主要包括Nios II软核处理器和UART、SPI、定制外设

2016-10-21 16:47:44

FPGA学习嵌入式硬件最小系统搭建(一)(NIOS II处理器设置)本期学习目的:利用NIOS II系统点亮LCD1602屏及5.7寸LCD(8080接口)。前言概述上篇文章介绍了嵌入式硬件系统概述

2021-12-20 07:02:02

收到远端的信号,进行解调解扩并传给网络,完成接收部分。其中一个NIOS II 核完成无线收发机接收和发送的信号处理和运算,另一个核运行操作系统,完成以太网传输和其他相关控制。之所以选择使用NIOS

2009-10-06 15:05:24

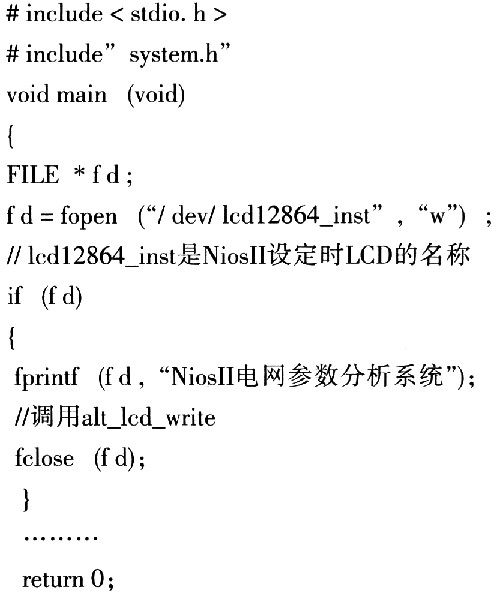

的程序设计在NiosⅡ和LCD的接口中,一方面可以通过在NiosⅡ系统中添加相应I/O口的方式来实现对液晶显示屏LCD的间接控制,另一方面也可以利用构建IP核来直接进行控制。第一种是将LCD接口当作普通

2018-12-11 11:08:10

II软核来完成,Nios II处理器将片上存储器中的数据逐一读取并进行处理之后显示在LCD上,Avalon总线负责各个控制器模块的数据传输。FPGA选用Altera公司的EP3C5E144C8。1.2

2019-06-03 05:00:06

II CPU如图4所示。4 系统实现启动Nios II IDE环境下,创建系统软件控制部分后,运行程序即可采集指纹图像,本系统环境下采集的指纹图像5所示。图6为作参考比较的光学采集指纹图像,指纹图

2019-04-29 07:00:08

、NiosII实现hello world1.1硬件设计芯片选择如下设置系统时钟,Tools -> Qsys添加Nios II Processor在搜索框中,输入nio,找到Nios II Processor,点击Add,最后保存即可添加On_Chip Memory在搜索框中,输入on_ch

2021-12-27 08:13:55

基于NioslI的SOPC系统中设计了LCD显示驱动IP核,并下载到Cyclone系列的FPGA中,实现了对LCD的显示驱动。

2019-11-04 08:18:58

信息显示在LCD液晶显示屏上。各硬件模块之间的协调工作通过嵌入式软核处理器NiosⅡ用编程实现控制。本设计所搭建的LCD12864控制器是通过编程实现的IP核。关键词:DDS;FPGA技术;顺序存储;NiosⅡ;IP核

2019-06-21 07:10:53

任务需求来定制显示控制功能,可以增强系统可靠性和设计灵活性,降低了成本。目前针对LCD 显示屏设计的控制器IP 核文章较多[1-2],但对于TFT-LCD 触控屏设计的控制器IP 核文章较少[3],而且

2018-11-07 15:59:27

实例精炼》第四章_VHDL的数据类型.avihttp://115.com/file/e7wpz111#《基于VHDL的FPGA与NIOS_II实例精炼》第十四章_字符型LCD的显示控制.avihttp

2012-02-06 11:22:55

验证的IP模块。参考演示包括将系统编程为具有墙壁和边缘避免以及同步运动的自主车辆。简单的PID控制将用于影响直流电机的速度和位置。步进电机将基于全步,半步和微步模式进行控制。附录中包含最终演示,用于监控电池系统中剩余的电量并在LCD上显示该值

2020-05-19 09:30:50

,LCD液晶显示器凭借功耗低、体积小、轻薄及控制驱动简单等特点,在智能仪器、仪表和低功耗电子产品中得到了广泛应用。以深圳秋田视佳实业有限公司的液晶显示模块CBGl28064为例,告诉大家, 如何在SOPC的NiosII中设计LCD显示驱动IP核?实现了对LCD的显示驱动。

2019-08-05 07:56:59

时,Builder开发工具中没有提供现成的数码管显示IP核,这使设计者工作量增加。这里把数码管控制器设计为一个共阴极(或共阳极)7段数码管动态显示IP核,并给出此核的一个参考驱动程序。

2019-08-09 06:09:05

Altera公司的FPGA作为全定制芯片的一个代表正在得到日益广泛的应用。为了用户使用方便,Altera公司推出嵌入式软核NiosⅡ可以便利地使用工具生成并放人FPGA芯片中。NiosⅡ软核可以在用

2019-10-25 07:25:38

怎么实现基于Nios II DTMB单频网适配器的设计?

2021-05-31 07:01:29

介绍如何在Altera开发平台上,使用Nios软核CPU来构建嵌入式Internet系统;并结合以太网远程数据采集系统的实例,介绍此类系统硬件,软件的设计方法。

2021-06-04 07:05:47

本文以 640*480的数字输入的 TFT-LCD显示屏为例,介绍了一种基于 NiosⅡ软核处理器实现对 TFT-LCD接口的方法。解决了通常情况下必须使用LCD 控制专用芯片才能解决 LCD显示的问题。

2021-06-08 06:46:33

是不是所有的cyclone IV系列的芯片都支持nios II软核

2014-08-13 10:34:55

本文设计了一种在多处理器系统中的Nios II软核处理器的启动方案,这个方案在外部处理器向Nios II的程序存储器和数据存储器加载数据时,可以控制Nios II处理器的启动。

2021-04-27 06:52:42

求大神给几个VHDL写的基于NIOS IIIP核源码,简单的就行,比如IIC AD什么的,多谢

2016-04-11 21:19:33

建立NIOS_Helloworld工程,进行IP核连线的时候,NIOS的jtag_reset信号如何与jtag_uart进行连接?

在原子哥的文档中对这步的操作在下面,

上面是文档中对连接方法的描述,但是我的qsys中在IRQ栏好像没有进行连接的按钮

请问软件是如何操作的?

2019-05-15 06:35:26

片上Nios Ⅱ嵌入式软核多处理器系统具有哪些优势?如何实现片上嵌入式Nios Ⅱ软核六处理器系统的设计?

2021-04-19 08:17:09

请问怎么去控制qsys搭建的SDRAM这个ip核,因为想把一个ram核当作一个外部AD数据的存储器,将外部数据存储起来,再用nios通过API函数读出来作显示,现在就是不知道怎么去去操作这个IP核

2019-08-25 17:35:20

、编译和调试程序。Nios II IDE提供了一个统一的开发平台,用于所有Nios II处理器系统。仅仅通过一台PC机、一片Altera的FPGA以及一根JTAG下载电缆,软件开发人员就能够往Nios

2015-09-08 22:35:45

II软核,可以直接放在FPGA中,它体现了把实现产品的全部单元电路集成到一个芯片之内的片上系统SOPC的思想。作为一种具有竞争力的技术,在国外已经有大量的产品使用了这种技术,在国内使用Nios II

2019-05-29 05:00:04

4为UPFC控制器IP核输出的实际波形图。4 结束语本UPFC控制器IP能使输出正弦波频率跟电网频率保持一致,且输出正弦波的幅值和相位可根据需要进行调节;输出的三角载波的频率、幅值和相位保持不变。同时,将UPFC控制器IP核和Nios II相结合还可提高系统的抗干扰能力。

2019-06-03 05:00:05

Nios II 软件开发参考手册

Nios II 软件开发参考手册

Nios II 软件开发参考手册

2007-06-05 18:56:43 120

120 首先介绍嵌入式实时操作系统μC/OS-II 和Nios 嵌入式处理器, 分析μC/OS-II 移植对目标处理器的要求, 重点介绍μC/OS-II 在Nios 处理器上的移植过程,最后在Nios 开发板上对移植工

2011-03-08 09:31:38 90

90 首先介绍嵌入式实时操作系统μC/OS-II 和Nios 嵌入式处理器, 分析μC/OS-II 移植对目标处理器的要求, 重点介绍μC/OS-II 在Nios 处理器上的移植过程,最后在Nios 开发板上对移植工作进行

2009-05-16 14:32:43 28

28 基于Nios II的自动指纹识别系统设计:介绍基于Nios II处理器的嵌入式自动指纹识别系统的实现方法;具体说明自动指纹识别系统的基本原理、系统总体结构、硬件结构设计、用户自定

2009-06-25 08:16:23 22

22 介绍了基于NIOS II 软核处理器的SOPC 技术,分析了传统方法和基于SOPC 技术的方法实现扩频收发机的优劣,详细说明了嵌有双NIOS II 的SOPC 技术的方案设计。该设计增强了系统功能,改善

2009-07-22 15:35:35 0

0 介绍了一种新的基于NIOS II的导航系统的设计方案. NIOS是建立在FPGA 上的嵌入式微处理器软核, 由于它硬件设计上的灵活性和可裁减性,使得软件设计上“平台”的概念延伸到硬件设计

2009-08-05 11:05:00 20

20 本文以Nios II 嵌入式软处理器为核心,利用USB 控制芯片CH372,设计了基于Nios II 嵌入式软处理器的USB 通信接口。本文重点介绍了USB 接口的硬件实现方案,分析了CH372 的通信流程,并

2009-08-28 11:34:28 33

33 介绍了基于NIOS II 软核处理器的SOPC 技术,分析了传统方法和基于SOPC 技术的方法实现扩频收发机的优劣,详细说明了嵌有双NIOS II 的SOPC 技术的方案设计。该设计增强了系统功能,改善

2009-11-27 14:23:43 15

15 为了提高传统指纹识别系统处理速度和安全问题,研究一种基于NIOS II 处理器的高速嵌入式指纹识别系统。利用NIOS II 的定制指令,FPGA 实现算法的硬件设计,同时结合先进的射频识

2009-11-30 14:18:01 28

28 在NIOS-II 系统中A/D 数据采集接口的设计与实现摘要:进行 SOPC 开发,很有必要学习一下定制NIOS 外设的方法和技巧。本文就是基于这种目的,详细的论述了在NIOS 系统中A/D 数据

2010-02-08 09:55:43 23

23 NIOS II软核处理器是Altera公司推出的一款灵活高效的嵌入式处理器。该处理器的应用常见于控制和通信领域。本文描述了在NIOS II系统上实现平台直方图均衡算法(Plateau Equalization ,PE)

2010-08-06 15:48:40 24

24 基于Nios-II设计和实现了支持PSTN网络、Internet网络的双网传真机系统,利用FPGA实现了传真机系统的多个电路模块,包括A/D采样控制逻辑、二值化图像处理模块、MH编码模块、MH译码模

2010-09-30 16:33:21 31

31 提出了将Altera公司的Nios II软核嵌入到FPGA器件内部来控制高性能直接数字频率合成器AD9858的方法,在简要介绍Nios II和AD9858的特性的基础上,详细说明了系统设计电路结构和软件设计

2010-12-09 16:23:28 31

31 NIOS II的特性及开发设计流程

NIOS的主要特点NIOS II是一个用户可配置的通用RISC嵌入式处理器。Altera推出的NIOS II系列嵌入式处理器扩展了目前

2010-02-08 14:47:31 1430

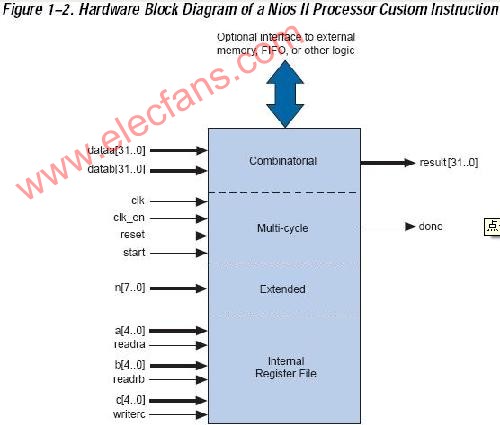

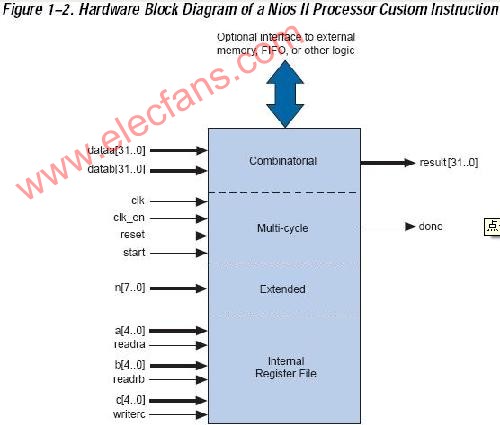

1430 NIOS II前哨计划step by step 1(NIOS II用户指令)

可编程软核处理器最大的特点是灵活,灵活到我们可以方便的增加指令,这在其他SOC系统中做不到的,增加用户指令可以把

2010-03-27 09:52:23 1040

1040

基于Nios-II设计和实现了支持PSTN网络、Internet网络的双网传真机系统,利用FPGA实现了传真机系统的多个电路模块,包括A/D采样控制逻辑、二值化图像处理模块、MH编码模块、MH译码模

2010-06-23 11:13:10 1795

1795

0 引言

NIOSⅡ是Altera公司推出的第二代IP软核处理器。它与其他IP核可构成SOPC系统的主要部分。Altera SOPC Builder提供有NiosⅡ处理器及一些常用外设接口,因此,对于一

2010-08-16 09:44:23 1476

1476

基于Nios II/

2011-01-09 20:59:04 29

29 摘要! 主要阐述了以FPGA为核心的基于NIOS II软核的嵌入式LCD图形显示设计 方法$ 从系统的角度提出在LCD上显示图形的设计过程#给出搭建NIOS II软核的系统整体结构图#并 最终实现了图形以及汉字在LCD上的显示最后总结出利FPGA技术实现LCD 图形显示的优势$

2011-02-11 14:17:40 42

42 Nios II内核详细实现

2012-10-17 13:59:49 83

83 Nios II 系列处理器配置选项:This chapter describes the Nios II Processor parameter editor in Qsys and SOPC

2012-10-17 14:08:42 17

17 Nios II定制指令用户指南:With the Altera Nios II embedded processor, you as the system designer can

2012-10-17 14:18:49 37

37 使用Nios II紧耦合存储器教程 Chapter 1. Using Tightly Coupled Memory with the Nios II Processor Reasons

2012-10-17 14:43:25 48

48 怎样使用Nios II处理器来构建多处理器系统 Chapter 1. Creating Multiprocessor Nios II Systems Introduction to Nios II

2012-10-17 14:51:06 19

19 电子发烧友网核心提示 :当您采用Nios II 嵌入式处理器进行设计时,您所使用的将是由Altera及其合作伙伴提供的可靠的软件开发工具和软件组件。 Nios II 嵌入式设计包 Nios II嵌入式设计

2012-10-17 15:31:13 1704

1704

为了实现对嵌入式系统中大量数据存储的需求,提出了一种基于NIOS II的SD卡存储系统设计方案,并完成系统的软硬件设计。该存储系统使用SPI模式对SD卡进行读写访问,SPI时序由NIOS II的

2013-07-25 16:19:49 66

66 NIOS II 常见问题总结,如果你想要Altera的FPGA做嵌入式设计,肯定要涉及到NIOS II的使用,本文总结了一些NIOS II的常见问题与解决方法

2015-12-01 15:43:34 14

14 在 Nios II 中根据需求定制基于 Avalon 总线的 IP 核模块,并使用定制的模

块实现对数码管的控制。通过本章,你能学到

(1)在 Nios II 中定制基于 Avalon 总线的 IP 核模块。

(2)在 Nios II 中控制数码管。

2015-12-14 15:39:39 3

3 NIOS_II各种性能表格对NIOS_II内核在各种型号的FPGA上的实现的性能说明

2015-12-21 17:19:15 22

22 介绍Modular Scatter-Gather DMA IP及如何与 Nios II 处理器搭配使用

2018-06-22 09:38:00 3030

3030

本文档的主要内容详细介绍的是如何制作一个方便在Quartus II和Nios II中使用的简单IP。

2019-07-09 17:40:00 2

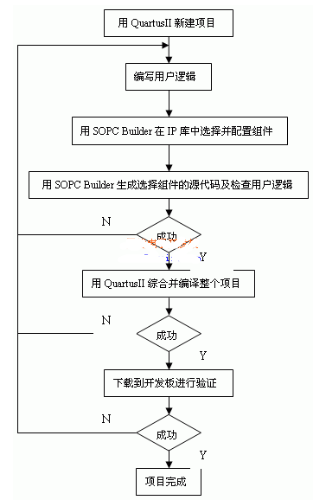

2 随着电路规模越来越大,片上系统(SoC)已经成为IC设计的发展趋势,相应地也有了更加灵活的片上可编程系统(SOPC)。Nios II CPU是一个基于流水线设计的通用RISC微处理器,拥有五级流水线

2020-04-11 17:01:12 1353

1353

本文论述了一种基于Nios II的可重构DSP系统设计。

2021-05-05 03:03:00 982

982

电子发烧友网站提供《基于NIOS II的SD卡读写控制设计.pdf》资料免费下载

2023-11-06 10:06:43 1

1

正在加载...

电子发烧友App

电子发烧友App

评论