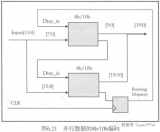

为了在USB 3.0中实现数据的8 b/10 b编解码,把8b/10b编解码分解成5 b/6 b编解码和3 b/4 b编解码,然后在FPGA上实现了具体的硬件电路。

2011-11-30 11:38:18 2803

2803

以下是笔者一些关于FPGA功耗估计和如何进行低功耗设计的知识。##关于FPGA低功耗设计,可从两方面着手:1)算法优化;2)FPGA资源使用效率优化。

2014-12-17 09:27:28 9177

9177 随着系统带宽不断增加至多吉比特范围,并行接口已经被高速串行链接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是独立的ASSP 或ASIC 器件。在过去几年中已经看到有内置SERDES 的FPGA 器件系列,但多见于高端FPGA芯片中,而且价格昂贵。

2015-02-02 17:32:52 2204

2204

这里将介绍SERDES的基本概念,并介绍SERDES相关的专有名词:眼图(Eye-diagram)、眼图模板、抖动(Jitter)、容忍度(tolerance)、功耗(Power Consumption)、预加重(Pre-emphasis)、均衡(Equalization)、8B/10B编码等。

2018-01-30 08:55:54 22436

22436

接口下,MAC芯片在将数据发给PHY芯片之前进行了8B/10B变换(8B/10B变换本是在PHY芯片中完成的,前面已经说过了)。 大多数芯片的TBI接口和GMII接口兼容。在用作TBI接口

2023-03-29 15:19:28 4316

4316 8b/10b编码用的控制字是K28.5,但是解码时用非K28.5的控制字能把数据解码出来吗?

2019-01-02 14:47:15

串行接口常用于芯片至芯片和电路板至电路板之间的数据传输。随着系统带宽不断增加至多吉比特范围,并行接口已经被高速串行链接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是独立

2019-10-23 07:16:35

FPGA的功耗高度依赖于用户的设计,没有哪种单一的方法能够实现这种功耗的降低,如同其它多数事物一样,降低功耗的设计就是一种协调和平衡艺术,在进行低功耗器件的设计时,人们必须仔细权衡性能、易用性、成本

2015-02-09 14:58:01

FPGA的功耗高度依赖于用户的设计,没有哪种单一的方法能够实现这种功耗的降低,如同其它多数事物一样,降低功耗的设计就是一种协调和平衡艺术,在进行低功耗器件的设计时,人们必须仔细权衡性能、易用性、成本、密度以及功率等诸多指标。

2019-11-05 07:54:43

FPGA的功耗高度依赖于用户的设计,没有哪种单一的方法能够实现这种功耗的降低,在进行低功耗器件的设计时,人们必须仔细权衡性能、易用性、成本、密度以及功率等诸多指标。

2019-08-29 07:52:29

目前许多终端市场对可编程逻辑器件设计的低功耗要求越来越苛刻。工程师们在设计如路由器、交换机、基站及存储服务器等通信产品时,需要密度更大、性能更好的FPGA,但满足功耗要求已成为非常紧迫的任务。而在

2019-07-15 08:16:56

到至少4个无错误的连续/K28.5/符号时,RX同步,然后将SYNC~引脚拉高。d、RX必须接收到至少4个无错误8B/10B字符,否则同步将失败,链路留在CGS阶段。e、CGS阶段结束,ILAS阶段开始

2019-12-03 17:32:13

接收到至少4个无错误8B/10B字符,否则同步将失败,链路留在CGS阶段。e、CGS阶段结束,ILAS阶段开始。注意:a、串行数据传输没有接口时钟,因此RX必须将其数位及字边界与TX串行输出对齐。RX

2019-12-04 10:11:26

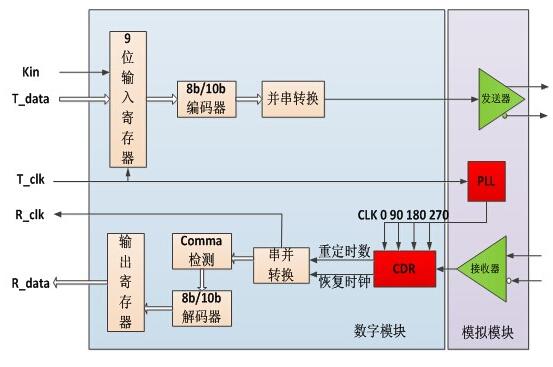

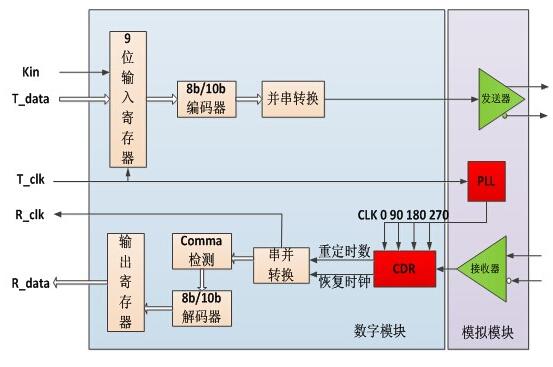

通信,该SERDES接口方案具有成本低、灵活性高、研发周期短等特点。 1 硬件接口: 硬件的接口如上图所示,主要包括发送与接收模块。 发送模块包括8b/10b编码器,并串转换器,锁相环(PLL

2019-05-29 17:52:03

低功耗蓝牙透传解析

2014-05-15 15:33:05

低功耗设计

2020-12-31 06:09:30

置顶/星标公众号,不错过每一条消息!在后台陆续收到一些关于STM8S低功耗的问题,今天就写一下低功耗相关的内容。1STM8S功耗来源STM8S功耗分静态功耗和动态...

2021-12-27 07:29:51

小弟最近在调用Aurora 8b/10b IP模块时,在用modelsim功能仿真时,一切正常。 但是直接使用了例化后的example,并将Tx和Rx形成了回路下到FPGA板子上

2015-03-09 10:58:03

什么是8b/10b编码,为什么JESD204B接口需使用这种编码?怎么消除影响JESD204B链路传输的因素?JESD204B中的确定延迟到底是什么? 它是否就是转换器的总延迟?JESD204B如何使用结束位?结束位存在的意义是什么?如何计算转换器的通道速率?什么是应用层,它能做什么?

2021-04-13 06:39:06

问:什么是8b/10b编码,为什么JESD204B接口需使用这种编码?

答:无法确保差分通道上的直流平衡信号不受随机非编码串行数据干扰,因为很有可能会传输大量相反的1或0数据。通过串行链路传输

2024-01-03 06:35:04

你好微芯片的工作人员!我正在从以下链接阅读关于降低功耗的一些技巧的文档:http://ww1.micro..com/...01146B_.%202.pdfOn TIP#3 Configuring

2020-04-30 09:25:33

中,都要保证每个Dword的正确性和完整性,否则将导致数据出错或原语流失。另外,目前高速数据传输接口或总线常用8B/10B编码来编码,其根本目的是实现直流平衡(DC Balance)。当高速串行流

2018-12-11 11:04:22

本文档是关于基于ARM® Cortex®-M3 内核的超低功耗32位单片机STM32L100x6/8/B-A的数据手册, 介绍了它的主要外设资源和电特性参数。特征:超低功率平台1.8V至3.6V电源

2022-11-28 07:55:36

【STM32L15xx6/8/B-】本文档是关于ARM® Cortex®-M3内核的超低功耗单片机STM32L151x6/8/B-A,STM32L152x6/8/B-A的数据手册。特征:超低功率平台

2022-11-28 08:06:54

大家好,我正在使用带有8B / 10B的Spartan-6 GTP传输32位数据,并使用光纤外部FPGA,当我将代码下载到芯片时,它是正确的,但在IPull输出光纤后立即插入电源(我称之为热插拔

2020-03-18 10:02:58

数进行权衡。支持 8b/10b 和 64b/66b 数据编码方案。64b/66b 编码支持前向纠错 (FEC),可改进误码率。此接口向后兼容 JESD204B 接收器。

无噪声孔径延迟调节

2024-01-31 15:22:55

,技术支持,价格最具优势!Y10-2VK2C23A/B概述:VK2C23A/B是一个点阵式存储映射的LCD驱动器,可支持最大224点(56SEGx4COM)或者最大416点(52SEGx8

2022-02-21 09:57:43

嗨,我试图在Zynq 7015中使用GTX来制作一个简单的传输仅使用8B10B编码的serdes。我有Vivado 2014.4,我在PicoZed SOM上测试。我有一个200Mhz LVDS信号

2020-07-31 09:10:30

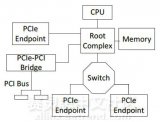

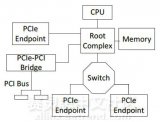

PCI Express increases data transport efficiency and data quality. It uses an 8b/10b encoding methodology to embed the clock signal ...

2019-09-23 11:01:40

JC-16接口技术委员会建立,目标是提供速率更高的串行接口、提升带宽并降低高速数据转换器和其他器件之间的数字输入和输出通道数。该标准的基础是IBM开发的8b/10b编码技术,它无需帧时钟和数据时钟,支持以

2019-05-29 05:00:04

位置?它是在最后,靠近物理引脚,还是,例如,在8B / 10B编码之前?我似乎无法在任何文档中找到答案。提前致谢!问候

2020-06-18 14:41:02

。此外,可通过8B/10B解码错误状态实时确定SERDES链路质量。伪随机位序列(PRBS)提供了一个测量高速链路中信号质量和抖动容差的有用资源。大部分FPGA 中的SERDES收发器都内置了PRBS

2018-10-16 06:02:44

数据的8b/10b编解码、高速串并转换,以及CPRI协议的成帧、解帧、同步、传输数据复/分解等操作。FPGA的控制作用主要是针对光接口模块和PHY模块。对于光接口模块,由于XFP提供一个两线的串行接口

2019-06-04 05:00:18

Gb/s传输给FPGA。在该数据流传输中,由于FPGA对数据进行8b/10b编解码,因此有效码率是10 Gb/s,能够满足本文的设计要求,可以实现10G以太网的数据流传输。时钟模块:时钟模块内采用

2019-05-31 05:00:06

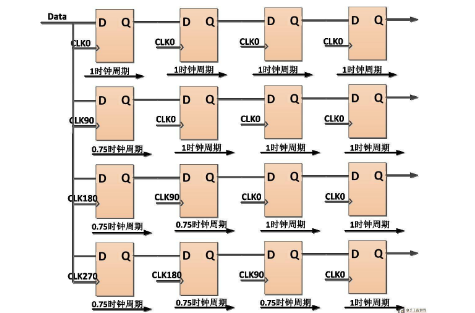

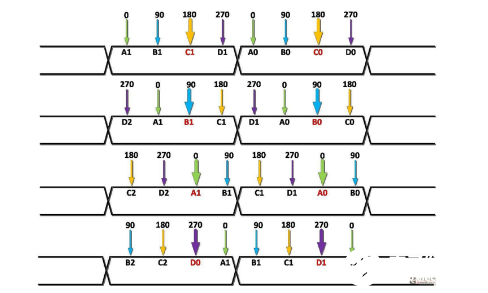

的协议会定义特殊的码型(常见的码型如8B/10B编码中的K28.5)用于字对齐处理。另一些带源同步时钟的LVDS接口,通常会利用低频的源同步时钟来携带字对齐信息,用于接收端的正确恢复。FPGA对上述两种

2019-07-29 07:03:50

高速LVDS数据传输方案和协议基于FPGA的高速LVDS数据传输本人在北京工作6年,从事FPGA外围接口设计,非常熟悉高速LVDS数据传输,8B/10B编码等,设计调试了多个FPGA与FPGA以及

2014-03-01 18:47:47

串行接口常用于芯片至芯片和电路板至电路板之间的数据传输。随着系统带宽不断增加至多吉比特范围,并行接口已经被高速串行链接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是独立的ASSP 或ASIC 器件。

2019-10-14 06:39:42

低成本、低功耗的设计解决方案,具有可重新编程、灵活和多功能的特点。这意味着电路板无需重新布局,并且可以实现更快的产品上市时间。因此,FPGA已成为一个备受关注的选择,可以满足紧凑的产品周期,以及7:1 LVDS、DVI和HDMI所需的高速接口和处理要求。

2019-06-05 05:00:17

你好,我正在尝试使用Aurora 8B / 10B建立仅传输(流媒体)。现在使用Vivado 2014.4进行模拟阶段。我知道GTXE2_COMMON原语需要在设计中使用以包含一个QUAD PLL

2020-08-14 08:49:13

如何利用Freeze技术的FPGA实现低功耗设计?

2021-04-29 06:27:52

Serdes向导中使用了不正确的设置吗?我在Comma Alignment上附上了Wizard页面的屏幕截图。作为附件。注意:我们在Serdes之外做8b / 10b,所以我们在没有解码的情况下查看原始数据。查克王尔德NEOTECH

2020-08-21 11:05:45

将使用逗号检测和对齐模块。但现在我有点困惑。如何在发送端发送逗号? 如果我只是使用GTP传输PRBS并接收PRBS,我是否必须使用逗号来对齐字节边界?我会在接收方做错误比较。我使用的GTP是16bit宽度接口,内部数据宽度为8bit。我不使用8b / 10b代码。 任何帮助将不胜感激!

2020-06-10 08:56:59

的模数转换器(ADC)和数模转换器(DAC)支持最新的JESD204B串行接口标准,出现了FPGA与这些模拟产品的最佳接口方式问题。FPGA一直支持千兆串行/解串(SERDES)收发器。然而在过去,大多数ADC

2021-04-06 09:46:23

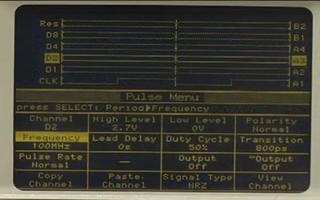

本方案是以CME最新的低功耗系列FPGA的HR03为平台,实现8/10b的SerDes接口,包括SERDES收发单元,通过完全数字化的方法实现SERDES的CDR(Clock Data

2019-10-21 07:09:44

如果不使用FPGA自带的SERDES,可否适用LVDS接口实现其功能?

2023-05-08 17:37:48

and other devices. The standard builds on 8b/10b encoding technology developed by IBM

2021-11-03 07:00:00

大家好,我使用的是Vivado 2016.4和Virtex 7 XC7VX485T FPGA。我需要知道是否有一个选项可以禁用Aurora IP Core 8B / 10B中的时钟补偿功能。我可以看到IP核心文件,但它们都是只读的。谢谢,马诺

2020-08-18 09:43:40

以及所针对的最终应用。并行数据通常将编码为标准编码方案(例如 8B/10B 编码),因而适用于串行化。原始应用数据可能包含病态模式、长期运行的 1 和 0,这会使串行解串器难以捕捉位跳变。对数据进行

2018-09-13 09:54:18

亲爱的先生,我正在使用Vivado 2015.4。我想在收发器向导中使用通道绑定,但CB在手册中是灰色的。另外,我找不到在收发器向导中启用8b / 10b编码器的方法。如果你能给我一些建议,我将不胜感激。问候,泰迪王

2020-08-04 08:32:57

问:什么是8b/10b编码,为什么JESD204B接口需使用这种编码?答:无法确保差分通道上的直流平衡信号不受随机非编码串行数据干扰,因为很有可能会传输大量相反的1或0数据。通过串行链路传输的随机数

2018-12-10 09:44:59

作者:黄刚上文说完了8B/10B之后,我们再来说说貌似更复杂的64B/66B编码。很多人可能在想,8B/10B编码主要作用的优化直流平衡,从8bit中插2个bit进去,这样的话最终效果能够使长0或者

2019-07-19 07:35:57

大家好,Vivado版本:15.2FPGA:Artix 7 xc7a50tAurora 8b / 10b IP v11.0(Rev 1) - 使用VHDL创建车道:1我最近一直面临着Aurora

2020-08-06 09:34:12

端口 - FPGA RX接口端口-----------------输出[15:0] gt0_rxdata_out,// ------- ---------接收端口 - RX 8B / 10B解码器端口

2020-08-10 10:11:17

如何利用FPGA设计技术降低功耗?

2021-04-13 06:16:21

关于ARM® Cortex®-M3超低功耗单片机STM32L15xx6/8/B的数据手册, 介绍了它的主要外设资源和电特性参数。特征:超低功率平台1.65V至3.6 V电源-40°C至85°C

2022-11-28 07:01:54

后,经过8B/10B编码,并/串变换等处理步骤,以串行差分信号的形式输出到光电转换子模块。为了保证PL4接口达到十路1Gbps的速率,PM3388的参考时钟引脚接160MHz时钟晶振,输入输出接口

2019-04-29 07:00:07

辅助数据。ISL34340中的DC平衡的8b/10b代码可以实现交流耦合,同时具有对地电位偏移的免疫性。对共模传输效果的改进有助于在更长距离的电缆上实现可靠的信号传输。ISL34340集成的发射器预

2019-05-08 07:00:01

(旁路)。 T M D S信号传输使用对本协议唯一的四个对齐的字符(不同于8B/10B方式)。串行器与SERDES的CDR传递10位的原始数据,FPGA进行字节对齐。 DVI/HDMI链路连接能以多个

2019-06-06 05:00:34

一、高速接口8B/10B的作用? 在数字通信中编码和加扰的作用是不同的。编码通常有信源编码和信道编码,8b/10b是信道编码,信道编码的作用是通过增加冗余(此外冗余为2b)以提高数据传输的可靠性。加

2022-01-18 06:16:43

作者:黄刚前面文章说过,在高速链路中导致接收端眼图闭合的原因,很大部分并不是由于高频的损耗太大了,而是由于高低频的损耗差异过大,导致码间干扰严重,因此不能张开眼睛。针对这种情况,前面有讲过可以通过CTLE和FFE(包括DFE)均衡进行解决,原理无非就是衰减低频幅度或者抬高高频幅度,从而达到在接收端高低频均衡的效果。同时我们在前文还埋了个伏笔:

2019-07-19 07:45:29

采用Xilinx 公司Virtex- II Pro 系列FPGA 内嵌得SERDES 模块———RocketIO 作为高速串行协议的物理层, 利用其8B/10B的编解码和串化、解串功能, 实现了两板间基于数据帧的简单高速串行传输

2010-09-22 08:44:28 28

28 具有低功耗意识的FPGA设计方法

ILGOO系列低功耗FPGA产品

Actel公司的ILGOO系列器件是低功耗FPGA产品,是在便携式产品设计中替代ASIC和CPLD的最

2009-11-26 09:41:19 676

676

摘要:为提高8B/10B编解码的工作速度和简化逻辑方法,提出一种基于FPGA的8B/10B编解码系统设计方案。与现有的8B/10B编解码方案相比,该方案是一种利用FPGA实现8B/lOB编解码的模块方

2011-05-26 11:08:20 3364

3364

白皮书 :采用低成本FPGA实现高效的低功耗PCIe接口 了解一个基于DDR3存储器控制器的真实PCI Express (PCIe) Gen1x4参考设计演示高效的Cyclone V FPGA怎样降低系统总成本,同时实现性能和功耗

2013-02-26 10:04:25 72

72 (Pseudo Random Binary Sequence,PRBS)检测方法对该编码器进行验证。FPGA综合结果表明,该设计占用的LUT为32,占用较少的逻辑资源。采用PIU3S-7测试结果表明,该8B/10B编码电路误码率为O,表明了该8B/10B编码器传输信息的可靠性。

2017-11-06 17:04:21 7

7 针对较为常用的Aurora 8B/10B和PCI Express 2.0,Serial RapidIO 2.0三种协议进行了测试及对比分析。首先搭建了基于Virtex-6 FPGA的高速串行协议测试

2017-11-18 01:00:06 11255

11255

Microsemi公司的SmartFusion2 SoC FPGA是低功耗FPGA器件,集成了第四代基于闪存FPGA架构,166MHz ARM Cortex-M3处理器和高性能通信接口,是业界最低功耗

2018-05-14 14:20:00 6839

6839

看看LatticeECP3 FPGA的功耗是多么的低,无论是在实验室中测量,还是利用莱迪思的功耗计算器软件计算。 LatticeECP3是业界最低功耗的配备SERDES的FPGA。

2018-06-15 13:36:00 4990

4990

关键词:FPGA , 低功耗 , RTL 在项目设计初期,基于硬件电源模块的设计考虑,对FPGA设计中的功耗估计是必不可少的。笔者经历过一个项目,整个系统的功耗达到了100w,而单片FPGA的功耗

2018-09-07 14:58:01 381

381 本方案是以CME最新的低功耗系列FPGA的HR03为平台,实现8/10b的SerDes接口,包括SERDES收发单元,通过完全数字化的方法实现SERDES的CDR(Clock Data

2019-05-24 15:33:25 4073

4073

8b/10b编码器用于将从上层协议芯片发送过来的字节信号映射成直流平衡的 10 位8b/10b 编码,并串转换用于将 10 位编码结果串行化,并串转换所需的高速、低抖动时钟由锁相环提供,发送器用于将 CMOS 电平的高速串行码流转换成抗噪声能力较强的差分信号,经背板连接或光纤信道发送到接收机。

2019-05-27 14:31:09 4988

4988

总线而成为高速接口设计的主流。 如今,随着SerDes接口的广泛应用,许多高端的FPGA都内嵌有SerDes接口硬核。在FPGA中内嵌的SERDES的硬核,可以大大地扩张FPGA的数据吞吐量,节约功耗,提高性能,使FPGA在高速系统设计中扮演着日益重要的角色。 国产

2020-07-28 12:05:16 1128

1128 功耗是各大设计不可绕过的话题,在各大设计中,我们应当追求低功耗。为增进大家对低功耗的认识,本文将对FPGA低功耗设计予以介绍。如果你对FPGA低功耗相关内容具有兴趣,不妨继续往下阅读哦。 FPGA

2020-10-28 15:02:13 2498

2498 功耗是各大设计不可绕过的话题,在各大设计中,我们应当追求低功耗。为增进大家对低功耗的认识,本文将对FPGA低功耗设计予以介绍。如果你对FPGA低功耗相关内容具有兴趣,不妨继续往下阅读哦。 FPGA

2020-10-26 18:51:16 2583

2583 因为摄像头输出的LVDS信号速率会达到600Mbps,我们将不能够通过FPGA的I/O接口直接去读取这么高速率的信号。因此,需要使用Xilinx FPGA内的SerDes去实现高速数据的串并转换。

2020-12-30 17:24:00 39

39 我在2015年底到2016年初的时候,使用7 Series FPGA Transceivers完成了TS流数据的传输,当时使用的传输速度为3.125G,SerDes选取的是8b/10b编码方式

2020-12-30 17:24:00 31

31 功耗是我们关注的设计焦点之一,优秀的器件设计往往具备低功耗特点。在前两篇文章中,小编对基于Freez技术的低功耗设计以及FPGA低功耗设计有所介绍。为增进大家对低功耗的了解,以及方便大家更好的实现低功耗设计,本文将对FPGA具备的功耗加以详细阐述。如果你对低功耗具有兴趣,不妨继续往下阅读哦。

2021-02-14 17:50:00 6072

6072 ARM与FPGA的接口实现的解析(应广单片机)-该文档为ARM与FPGA的接口实现的解析详述资料,讲解的还不错,感兴趣的可以下载看看…………………………

2021-07-22 09:47:55 14

14 论序 8b/10b编码/解码是高速串行通信,如PCle SATA(串行ATA),以及Fiber Channel中常用的编解码方式。在发送端,编码电路将串行输入的8比特一组的数据转变成10比特一组

2021-09-26 09:56:22 7402

7402

8b/10b最常见的是应用于光纤通讯和LVDS信号的。由于光模块光模块只能发送亮或者不亮,也就是0或者1这两种状态这种单极性码,那么这会存在一个问题,如果传输中出现较长的连0或者连1(例如

2022-11-12 15:47:27 7711

7711 与现有的中端FPGA相比,得益于专为低功耗设计的可编程结构、功耗优化的嵌入式存储器和DSP、低功耗高性能SERDES与I/O设计、内置协议逻辑等全方位优化措施,Avant系列产品的功耗比同类竞品器件低2.5倍。

2023-01-04 11:32:11 342

342 摘要:莱迪思(Lattice )半导体公司在这应用领域已经推出两款低成本带有SERDES的 FPGA器件系列基础上,日前又推出采用富士通公司先进的低功耗工艺,目前业界首款最低功耗与价格并拥有SERDES 功能的FPGA器件――中档的、采用65nm工艺技术的 LatticeECP3系列。

2023-10-27 16:54:24 237

237 的ASSP 或ASIC 器件。在过去几年中已经看到有内置SERDES 的FPGA 器件系列,但多见于高端FPGA芯片中,而且价格昂贵。 本方案是以CME的低功耗系列FPGA的HR03为平台,实现

2023-07-27 16:10:01 1565

1565

电子发烧友App

电子发烧友App

评论