当前,FPGA 已经成为云数据中心里重要的硬件加速单元。例如,在之前的文章中详细介绍过微软的“Catapult”项目。通过这个项目,微软在 Azure 云数据中心里部署了上百万个基于 FPGA 的智能网卡,并使用 FPGA 对一系列应用进行了硬件加速。这其中包括必应搜索(Bing)的文件排名运算,以及通过 FPGA 构建的实时 AI 系统“Brainwave”。

亚马逊 AWS 则采用了名为 FPGA 即服务(FaaS)的业务模式,也就是将 FPGA 作为了 AWS 云的硬件加速实例,面向云服务的广大用户和开发者。这种业务模式提供了 FPGA 云服务的完整基础设施架构,包括 FPGA 的开发、调试、部署、维护等等,使得开发者可以直接利用云中的 FPGA 资源进行算法的硬件加速和开发。腾讯云、阿里云、华为云等公有云提供商也纷纷跟进,也在云服务中加入了 FPGA 的硬件加速实例。

然而,随着 FPGA 在云数据中心的不断部署,由此引发的安全性隐患也逐渐成为业界关注的重点之一。和 CPU、GPU、网络交换芯片等数据中心常见的硬件单元不同,FPGA 带来的潜在安全性问题有着非常独特的一面。

一方面,FPGA 芯片本身可能存在高危漏洞。在之前的文章中,我们介绍过赛灵思的 7 系列 FPGA 被曝出名为“StarBleed”的漏洞,它使得攻击者能同时攻破 FPGA 配置文件的加密和鉴权两个重要环节,并由此随意更改 FPGA 中实现的逻辑功能。这个漏洞的严重之处在于,一旦 FPGA 芯片被攻破,就无法通过软件补丁的方式进行修复,而只能停机换芯片。

另一方面,由于 FPGA 的特殊性,即使芯片没有任何功能漏洞,攻击者也可以使用一些很巧妙的手段进行破坏性的操作,并破解并窃取加密信息。今天这篇文章,就将介绍这其中的一个攻击方法。

FPGA 虚拟化与多租户 FPGA

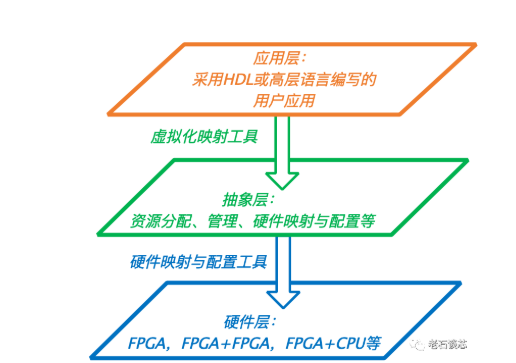

在 FPGA 的云计算应用中,虚拟化技术是目前比较常见的 FPGA 管理和资源调度方式。关于 FPGA 虚拟化技术,有兴趣的读者可以看看老石之前的文章《FPGA 虚拟化:突破次元壁的技术》,里面详细介绍了 FPGA 虚拟化的很多技术细节。简单来说,虚拟化技术在传统的 FPGA 开发层级中加入了额外的一层,从而将用户的应用逻辑与底层硬件分离开,使开发者无需太关心硬件的实现方式,这能大幅降低 FPGA 的开发难度,缩短开发周期。

通过 FPGA 虚拟化技术,就可以实现在单个 FPGA 上划分出多个逻辑区域,并分配给不同的用户进行使用,这就是 FPGA 的多租户(Multi-tenent)技术。

在多租户 FPGA 中,理论上不同用户的区域是相互独立的,这可以通过划分不同的 FPGA 设计区域实现。不同的用户并不会共享 FPGA 上的逻辑资源,此外,他们的 FPGA 配置文件、上层软件等都应该是加密和独立的。这些都由虚拟层进行调度和管理,在技术上,这可以通过 FPGA 的部分可重构(Partial Reconfiguration)特性实现。

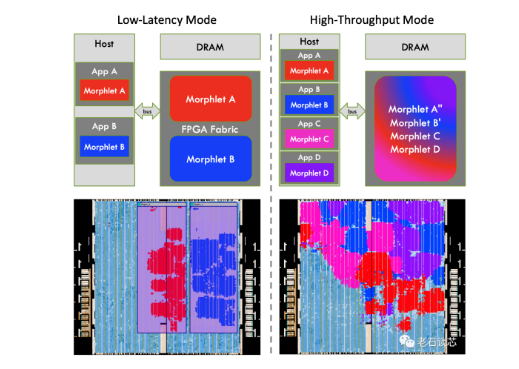

例如,下图中就展示了两种不同的多租户 FPGA 实现方法,第一种使用了两个相互独立的设计区域,第二种则实现了多个用户设计 A、B、C、D 在 FPGA 上的混合排列。

事实上,不同用户的设计区域很难做到完全独立。比如,在同一个 FPGA 芯片上,供电、时钟等全局资源往往需要共享。仅仅如此,就会给多租户 FPGA 设计带来安全隐患。

针对 FPGA 的电压攻击

在今年的 FCCM 大会上,来自马萨诸塞大学的 Russell Tessier 教授做了名为“Security and Privacy Concerns for the FPGA-Accelerated Cloud and Datacenters”的报告,并介绍了一种针对 FPGA 的电压攻击方法。

这篇论文的全文和大会报告,已上传至知识星球“老石谈芯 - 进阶版”,请于文末扫码进入星球查看。

简单来说,攻击者可以在 FPGA 上实现一些消耗大量功耗的电路,由此会引发芯片上电压的下降。由于使用同一个 FPGA 的用户共享芯片上的供电网络,这种电压下降会波及到 FPGA 上其他用户的设计区域。值得注意的是,这种利用电压进行攻击的方式会无视多租户之间相互独立的逻辑区域。

一旦电压下降过大,就会带来很多问题。其中最主要的问题,就是会造成电路延时的增加。这样一来,原本时序收敛的设计就不能满足时序,从而造成各种错误的功能和计算结果。

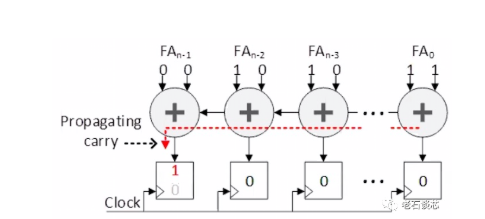

例如,对于常见的加法运算来说,它的关键路径取决于最长进位传播(carry propagation)的时间。正因此,FPGA 中内置了固化的进位链结构,以提高进位传播的速度。然而,一旦电路延时增加,可能会导致时钟沿到来时,加法的进位尚未完成传播,由此导致计算结果出现重大误差。

下图就是一个行波进位加法器(Ripple Carry Adder)的例子,它计算四位二进制加法 1111 + 0001 时,应该得到二进制数 10000(十进制 16),但由于电压降低导致延时增加,使得进位未能传播到最高位,最终得到的结果是 00000。

耗电单元(Power Waster)

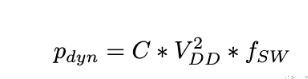

可以看到,这种电压攻击的关键,就是在 FPGA 上实现某种可以消耗大量功耗的电路。数字电路的一个重要知识点是,动态功耗和所谓的开关速率(switch activity)呈线性相关,也就是下面这个公式中的 f。因此只要实现一个能高速进行状态切换的电路,就能消耗大量功耗。

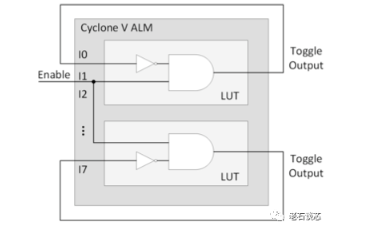

基于此,这种耗电模块事实上非常简单,可以直接用一阶环形振荡器实现,见下图。

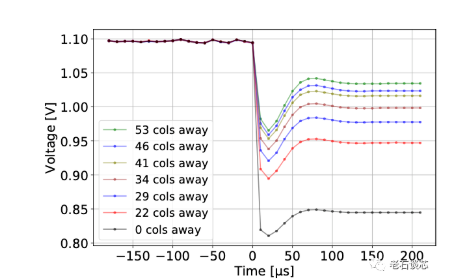

实验表明,当例化 28000 个这样的环形振荡器时,每个振荡器可以消耗 2.2mW 的功耗,并由此带来芯片上电压的迅速下降。在下图中可以看到,50 微秒之内,离这些耗电单元最近区域的电压(黑线)就由 1.1V 下降到 0.85V 左右。如果离耗电单元稍远,也会出现不同程度的电压下降,甚至在芯片的边缘部分也会受到波及。

使用这种电压攻击的方法,除了可以对其他用户的电路功能造成破坏之外,还可以用来窃取其他用户的加密信息。例如,Tessier 教授就展示了如何破解并获取 RSA 算法的私钥。简单来说,有一种名为中国剩余定理(CRT,也称为孙子定理)的算法,在实现 RSA 计算时可以得到 4 倍的性能提升。然而,如果在这个过程中通过电压攻击的方法引入错误的计算结果,就会简单的反推出 RSA 的私钥,并且这个过程与 RSA 密钥长度无关,且只需要一次迭代就可以完成。这个过程的具体细节在本文不再赘述,有兴趣的读者可以在知识星球“老石谈芯进阶版”或微博与我互动讨论。

FPGA 电压攻击的防治策略

如前文所述,这种基于大量耗电单元、并导致芯片电压下降和电路延时增加的攻击方式,会对使用 FPGA 的全部用户都造成影响,而且不受设计区域划分的限制。与之前介绍过的 StarBleed 漏洞不同,这种攻击方法并不利用 FPGA 芯片本身的设计缺陷,而是利用了 FPGA 的特点,大量例化耗电单元并实施攻击。因此这种方法理论上适用于任何 FPGA。

为了应对这样的新型攻击方式,一种防御方法就是在芯片上布置若干电压检测模块,并实时监控不同区域的电压值。如果一旦出现电压攻击,这些检测模块就可以锁定导致电压下降的源头,并配合管理软件对这个用户区域进行封锁。

在下图中,使用了 12000 个耗电模块,以及不同数量的电压检测单元,出现异常的电压检测单元以黑点表示。可以看到,当使用 40 个电压检测单元时(最右图),就可以把攻击源头锁定在一个相对较小的区域中。

此外,电压下降带来的延时增加并非都是坏事。这涉及到一个重要的思维方式的转变。近年来,一个比较流行的研究领域叫做“近似计算”,即 Approximate Computing。它的主要观点是,在很多特定的应用场景中,并不需要做到 100%的精确计算,而这会带来可观的性能提升与功耗降低。

电子发烧友App

电子发烧友App

评论