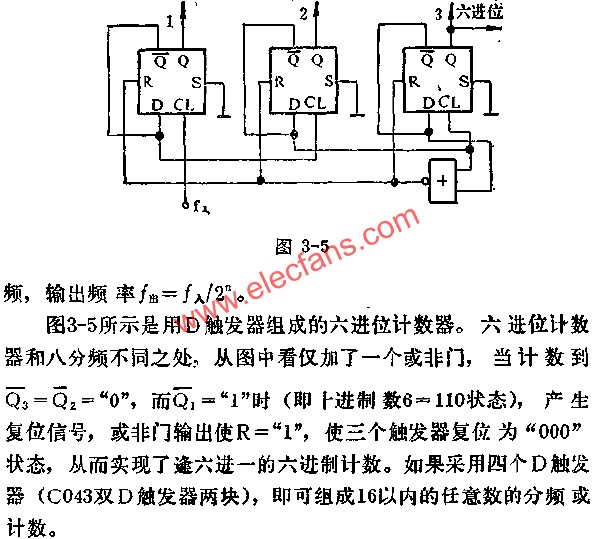

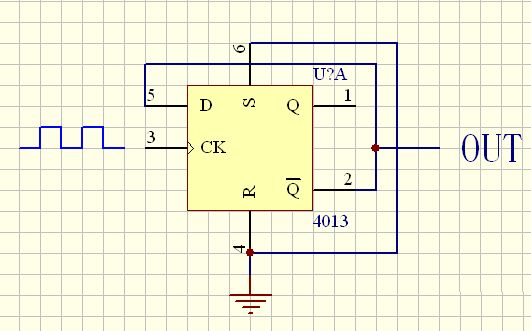

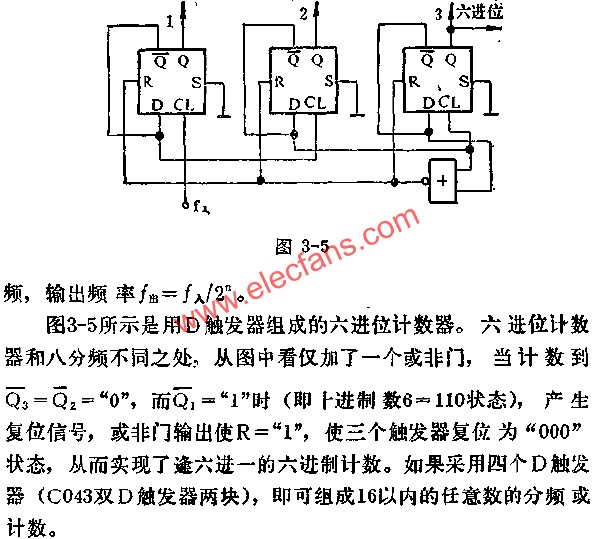

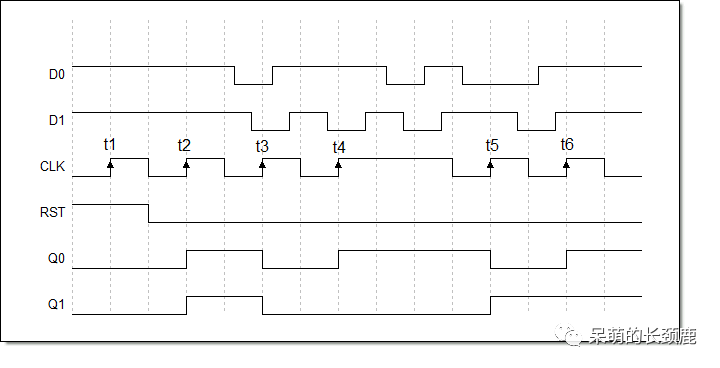

上例图中A将D触发器的D端和Q相连,即可组成二分频电路,如果把三个D触发器串行相连,如图所示,则经过一

2010-09-20 03:40:48 13636

13636

D触发器(D Flip-Flop)是一种数字电子电路,用于延迟其输出信号(Q)的状态变化,直到时钟输入信号的下一个上升沿出现。

2023-12-04 15:23:14 3955

3955

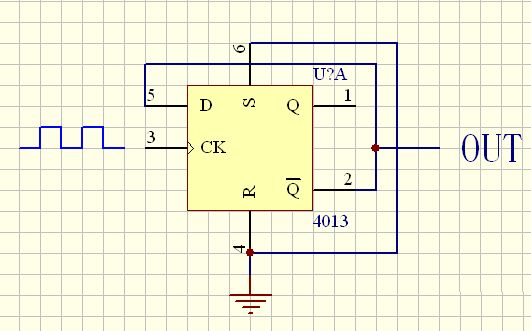

D触发器实现二分频电路(D触发器构成的2分频电路)

2020-03-02 11:05:49

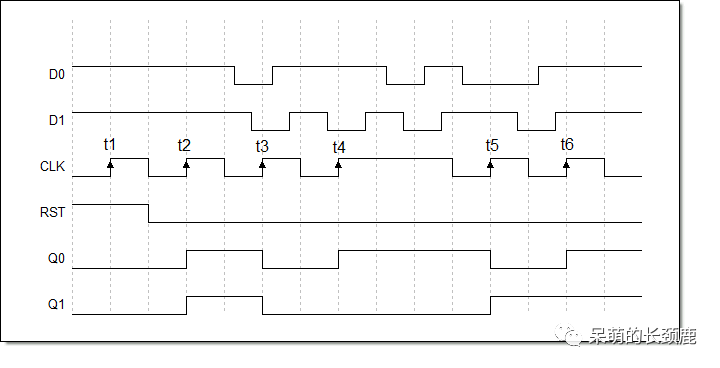

做了一个仿真:key_in作为D触发器的输入,led_out作为触发器输出,时钟周期20ns,key_in每10ns随机变化一次,这样的设置下,key_in信号的变化沿有时会和时钟上升沿重合,根据

2022-01-25 22:41:02

电路为什么要有触发器这种结构?为什么要用时钟同步起来呢?一个乘法器如果不设计成触发的会是什么状态?最近在想电路同步异步的时候想到这个问题。

2016-12-08 17:41:52

JK触发器和D触发器所使用的时钟脉冲能否用逻辑电平开关提供?为什么?

2023-05-10 11:38:04

根据输入信号改变输出状态。把这种在时钟信号触发时才能动作的存储单元电路称为触发器,以区别没有时钟信号控制的锁存器。触发器是一种能够保存1位二进制数的单元电路,是计算机中记忆装置的基本单元,由它可以组成

2019-12-25 17:09:20

`如图所示,图中第一个触发器D接第二个触发器的非Q端,这个时序图,整不明白啊,我的看法是:当第一个时钟信号高电平来的时候,第一个触发器的输出状态Q是不能判断的啊,因为D接在第二个触发器的非Q端。求大佬指点一下 这个图,是如何工作的?`

2019-01-16 11:50:35

触发器没有使用相同的时钟信号,需要分析哪些触发器时钟有效哪些无效分析步骤和同步时序电路一样,不过要加上时钟信号有关D触发器的例题抄自慕课上的一个题目,注意第二个触发器反相输出端同时连接到复位端JK

2021-09-06 08:20:26

。为了避免这种情况,在存储了所需数据之后,使用称为“时钟”或“使能”输入的附加输入将数据输入与触发器的锁存电路隔离。结果是,仅当时钟输入处于活动状态时,D输入条件才会复制到输出Q。然后,这构成了另一个

2021-02-03 08:00:00

我正在尝试使用 PTP 实现时钟同步,请帮忙。

2023-03-31 09:00:46

本帖最后由 gk320830 于 2015-3-5 20:47 编辑

如何用JK触发器构成D触发器 电路图来人给个图吧..

2011-11-14 15:21:03

单片机内部有大量寄存器, 寄存器是一种能够存储数据的电路, 由触发器构成。1.触发器触发器是一种具有记忆存储功能的电路, 由门电路组成。 常见的触发器包括: RS 触发器、 D 触发器和 JK触发器

2022-01-20 07:13:51

习时把这一章分为两节,它们分别是:§5、1 时序电路的概述§5、2 触发器 5、1 时序电路的概述 这一节我们来学习一些关于时序电路的概念,在学习时要注意同步时序电路和异步时序电路的区别一:时序电路

2018-08-23 10:36:20

Jack Kilby)和D(延迟)。典型的触发器包括零个、一个或两个输入信号,以及时钟信号和输出信号。一些触发器还包括一个重置当前输出的明确输入信号。第一个电子触发器是在1919年由

2019-06-20 04:20:50

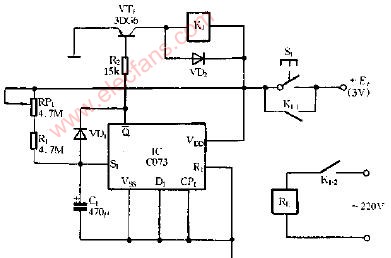

电后,与非门的1脚为低电平,故U1A输出端第3脚为高电平,3脚与与非门的12脚相连,故12脚也为高电平。 2、电路刚上电时,D触发器的RD引脚通过电容C1,电阻R2上电复位,使D触发器的输出Q=D

2023-03-20 15:33:48

使用带同步清零端的D触发器(清零高电平有效,在时钟下降沿执行清零操作)设计下一个下降沿触发的D触发器,只能使用行为语。使用设计出的D触发器输出一个周期为10个时间单位的时钟信号。下面是网上的答案

2015-07-30 21:01:49

的分类 触发器呢大体可以按这几个部分分类:1、按晶体管性质分,可以分为BJT集成电路触发器和MOS型集成电路触发器。2、按工作方式分,可分为异步工作方式和同步工作方式,异步工作方式也就是不受时钟控制

2015-04-07 17:47:42

D触发器的功能测试74LS74型双D触发器芯片引脚图,D触发器功能测试的引脚连线图,D触发器功能测试的引脚连线图,用D触发器构成二进制计数器,用D触发器构成四位移位寄存器

J-K

2009-02-14 15:27:51 0

0 D触发器的制作及电路图

2009-05-19 09:35:49 33

33 5.1 基本RS触发器5.2 时钟控制的触发器5.3 集成触发器5.4 触发器的逻辑符号及时序图

2010-08-10 11:53:23 0

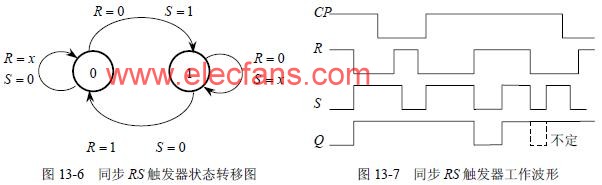

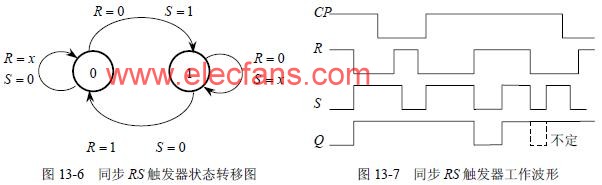

0 教学目标:1、 掌握钟控同步RS触发器的电路组成2、 掌握钟控同步RS触发器的工作原理及逻辑功能3、 了解触发器的应用教学重难点:重点:钟控同步 RS 触

2010-08-18 14:57:41 16

16 时钟触发器的结构形式

2010-08-19 11:04:21 28

28 一、基本要求1、理解R-S触发器、J-K触发器和D触发器的逻辑功能;2、掌握触发器构成的时序电路的分析,并了解其设计方法;3、理解计数器和寄存器的概念和功能,并掌握它

2010-08-26 11:40:22 57

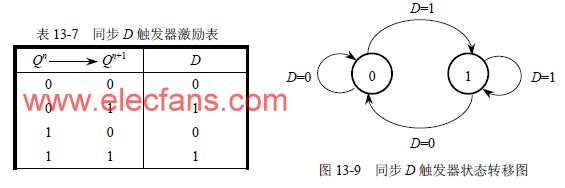

57 D触发器真值表分析:

1. D 触发器真值表

Dn

2007-09-11 23:15:20 20330

20330 D触发器

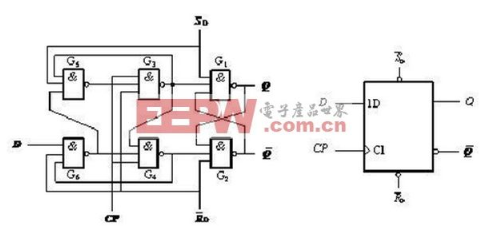

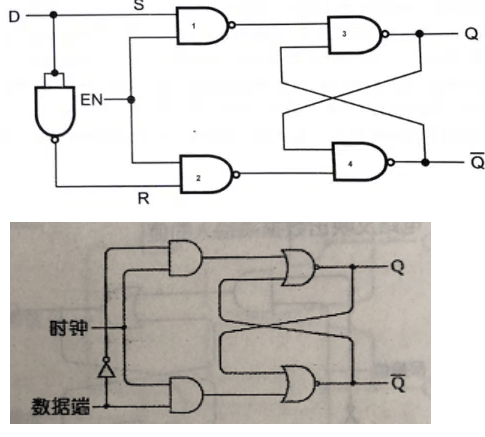

同步式D触发器逻辑电路图

D触发器功能

2008-10-20 09:57:54 2818

2818

同步式D触发器逻辑电路图

2008-10-20 09:58:19 9218

9218

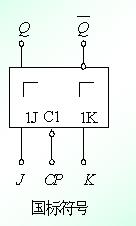

4.2.2 同步触发器二、同步D触发器1.电路结构2.逻辑功能3.特性方程4.状态转换图三、同步JK触发器1.电路结构2.逻辑功能3.特性方程4.状态转换

2009-03-30 16:17:07 5250

5250

D触发器电路图

2009-05-08 14:26:44 4008

4008

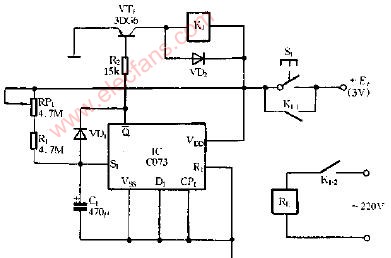

D触发器构成的定时电路图

2009-05-08 15:15:26 4564

4564

D触发器实现二分频电路(D触发器构成的2分频电路)&

2009-06-12 13:58:56 81145

81145

d触发器构成2分频电路

2009-06-22 07:36:33 8568

8568

T触发器,什么是T触发器

在数字电路中,凡在CP时钟脉冲控制下,根据输入信号T取值的不同,具有保持和翻转功能的电路,即当T=0时

2009-09-30 18:26:07 30888

30888

Verilog HDL语言实现时序逻辑电路

在Verilog HDL语言中,时序逻辑电路使用always语句块来实现。例如,实现一个带有异步复位信号的D触发器

2010-02-08 11:46:43 5099

5099 D触发器,D触发器是什么意思

边沿D 触发器: 电平触发的主从触发器工作时,必须在正跳沿前加入输入信号。如果在CP 高

2010-03-08 13:53:13 5319

5319 D触发器工作原理是什么?

边沿D 触发器:

负跳沿触发的主从触发器工作时,必须在正跳沿前加入输入信号。如果在CP 高电平期间输入端出

2010-03-08 13:56:50 70741

70741

触发器的分类, 触发器的电路

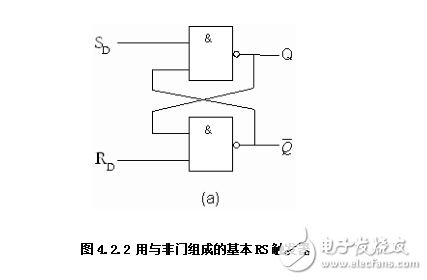

双稳态器件有两类:一类是触发器,一类是锁存器。锁存器是触发器的原始形式。基本

2010-03-09 09:59:59 1866

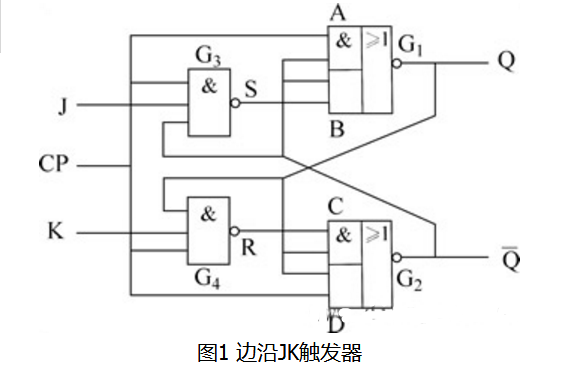

1866 由与非门构成的同步RS触发器如图13-5(a)所示,其逻辑符号如图13-5(b)所示。图中门A和B构成基本触发器,门C和E构成触发引导电路。由图13-5(a)可见,基本触发器的输

2010-08-18 09:00:00 17146

17146

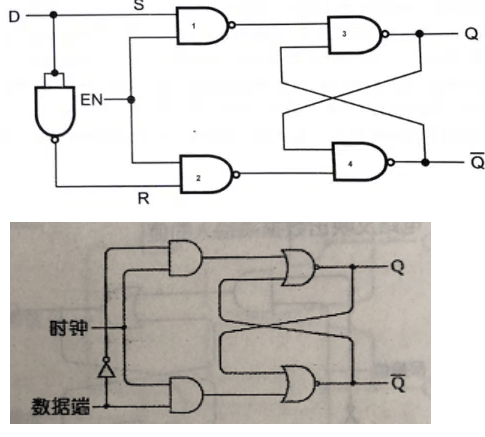

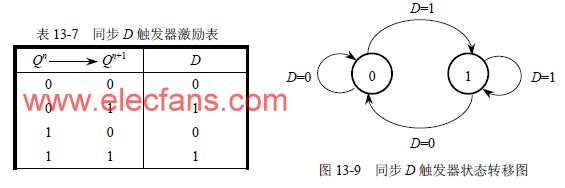

为了避免同步RS触发器的输入信号同时为1,可以在S和R之间接一个“非门”,信号只从S端输入,并将S端改称为数据输入端D,如图15-8所示。这种单输入的触发器称为

2010-08-18 09:06:00 13148

13148

一、空翻问题由于在CP=1期间,同步触发器的触发引导门都是开放的,触发器都可以接收输入信号而翻转,所以在CP=1期间,如果输入信号发生多次变化,触发器的

2010-08-18 09:08:32 22815

22815

图中所示是用CMOS电路D触发器组成T型触发器和J-K触发器线路。图示线路将D触发器的Q端与D端相连,就可组成T

2010-09-20 03:31:35 21923

21923

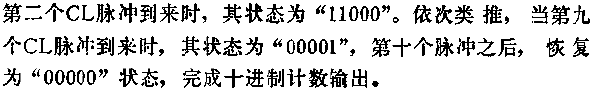

图中所示是用CMOS电路D触发器组成的十进制环形计数器.图中先将D触发器拼成移位寄存器,然后把最后一级D触发器

2010-09-20 23:46:58 20369

20369

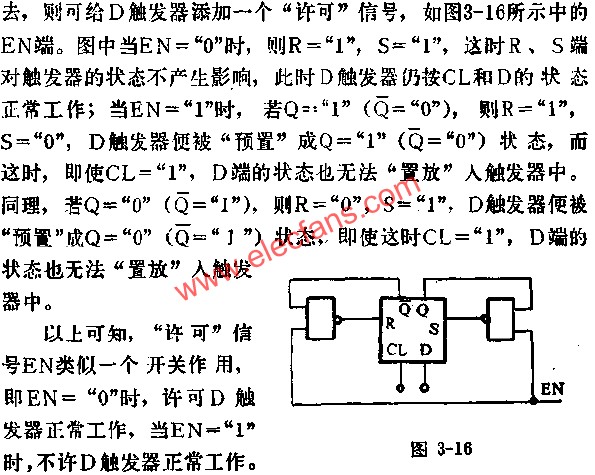

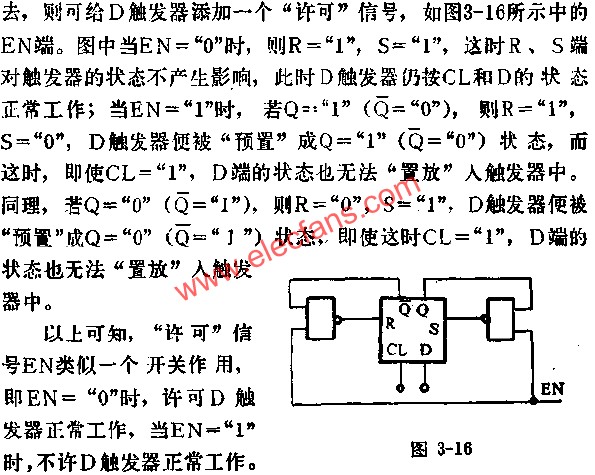

从D触发器的真值表可知,当时钟脉冲CL="1"时,数据输入端D的状态会被“置放”入触发器中去,而与触发器原状无关。如果当时钟冲CL="1",D端状态不旋转放入

2010-09-21 01:27:59 780

780

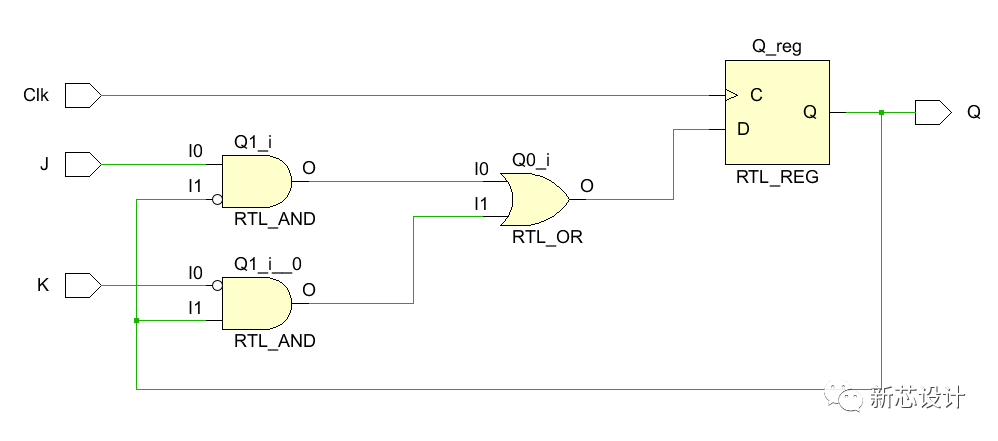

图中所示是用J-K触发器组成的D触发器电路。

从J-K触发器的逻辑图已知在D触发器端增

2010-09-24 00:21:27 8886

8886

请高手指点下有啥问题,D触发器开关电路

2017-01-14 01:30:04 25

25 1、掌握触发器功能的测试方法。

2、掌握基本RS触发器的组成及工作原理。

3、掌握集成JK触发器和D触发器的逻辑功能及触发方式。

4、掌握几种主要触发器之间相互转换的方法。

5、通过实验、体会CPLD芯片的高集成度和多I\O口。

2022-07-10 14:39:58 18

18 实验内容 将基本RS触发器,同步RS触发器,集成J-K触发器,D触发器同时集成一个CPLD芯片中模拟其功能,并研究其相互转换的方法。 实验的具体实现要连线测试。 原理图 如图6-1

2017-12-05 09:33:41 13

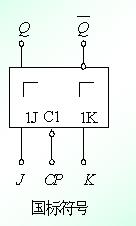

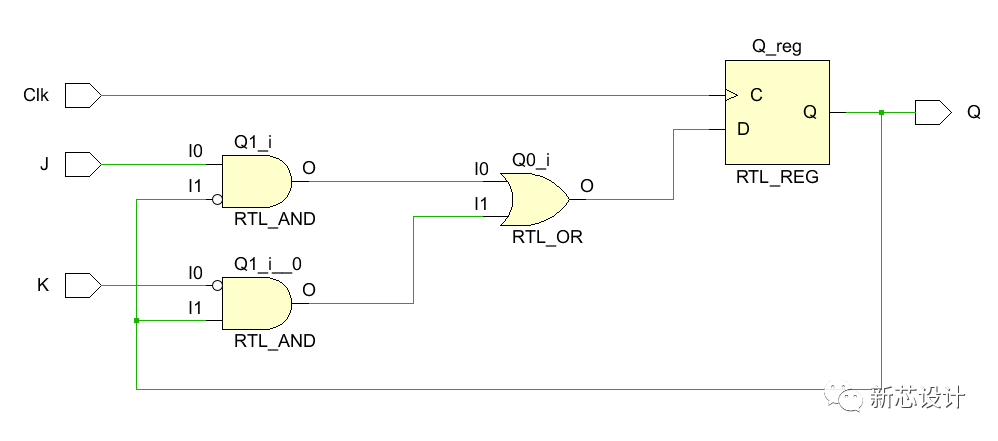

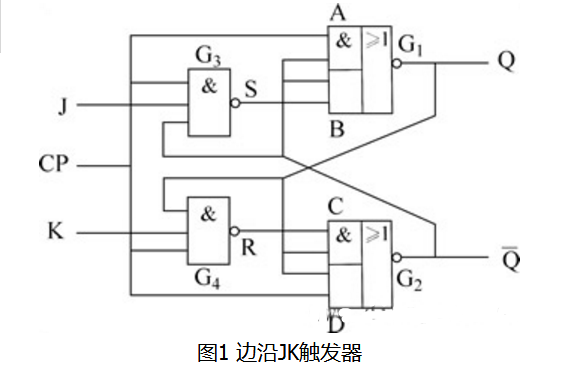

13 JK触发器是数字电路触发器中的一种基本电路单元。JK触发器具有置0、置1、保持和翻转功能,在各类集成触发器中,JK触发器的功能最为齐全。在实际应用中,它不仅有很强的通用性,而且能灵活地转换其他类型的触发器。由JK触发器可以构成D触发器和T触发器。

2017-12-25 17:30:03 192486

192486

边沿触发器,指的是接收时钟脉冲CP 的某一约定跳变(正跳变或负跳变)来到时的输入数据。在CP=l 及CP=0 期间以及CP非约定跳变到来时,触发器不接收数据的触发器。具有下列特点的触发器称为边沿触发方式触发器,简称边沿触发器。

2018-01-31 09:02:33 73165

73165

边沿触发器只在时钟脉冲CP上升沿或下降沿时刻接收输入信号,电路状态才发生翻转,从而提高了触发器工作的可靠性和抗干扰能力,它没有空翻现象。边沿触发器主要有维持阻塞D触发器、边沿JK触发器、CMOS边沿触发器等。

2018-01-31 09:17:11 33188

33188

按照稳定工作状态分,可分为双稳态触发器、单稳态触发器、无稳态触发器(多谐振荡器)等;按照逻辑功能划分,可分为RS触发器、D触发器、T触发器、JK触发器等几类;按照电路结构划分,可分为基本RS触发器、同步触发器(时钟控制的触发器)、主从型触发器、维持-阻塞型触发器和边沿触发器等几种类型。

2018-01-31 15:02:50 29042

29042

本文开始介绍了什么是单稳态触发器以及单稳态触发器的电路组成,其次阐述了单稳态触发器特点、门电路构成的单稳态触发器、D触发器构成的单稳态触发器,最后详细的阐述了时基电路构成的单稳态触发器。

2018-03-27 09:24:23 78857

78857

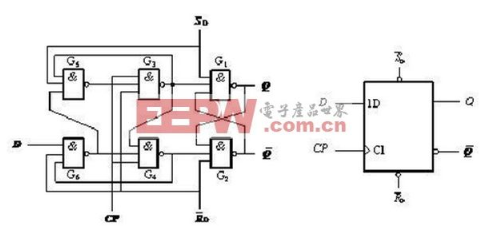

CP=1时,门。。打开,门。。被封锁,从触发器保持原来状态不变,D信号进入主触发器。但是要特别注意,这时主触发器只跟随而不锁存,即。。跟随D变化,D怎么变。。也随之怎么变。

2019-07-15 08:57:32 56238

56238

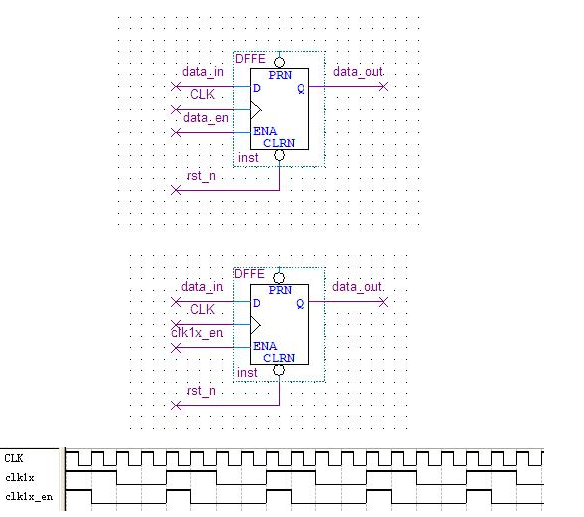

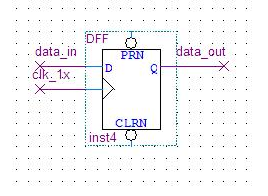

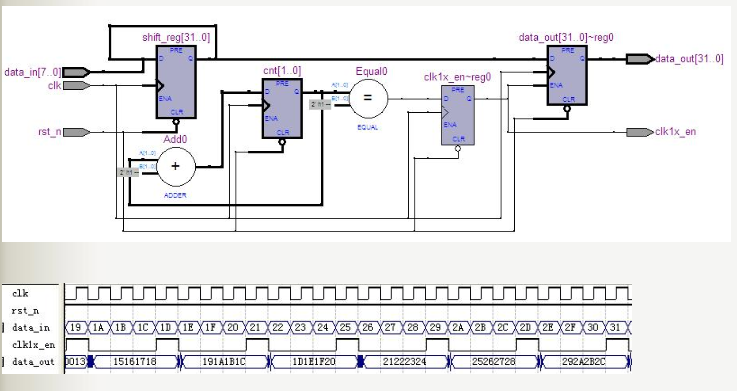

首选我们来聊聊时序逻辑中最基础的部分D触发器的同步异步,同步复位即复位信号随系统时钟的边沿触发起作用,异步复位即复位信号不随系统时钟的边沿触发起作用,置数同理,rst_n表示低电平复位,我们都知道D

2019-07-26 10:17:16 27982

27982

JK触发器是数字电路触发器中的一种基本电路单元。JK触发器具有置0、置1、保持和翻转功能,在各类集成触发器中,JK触发器的功能最为齐全。在实际应用中,它不仅有很强的通用性,而且能灵活地转换其他类型的触发器。由JK触发器可以构成D触发器和T触发器。

2019-11-08 14:48:44 96918

96918

在分析维持-阻塞边沿D触发器的工作原理之前,让我们先来看看 R0的复位功能 、S0的置位功能是如何实现的吧。

2020-10-18 11:26:31 26555

26555

74LS74内含两个独立的D上升沿双d触发器,每个触发器有数据输入(D)、置位输入( )复位输入( )、时钟输入(CP)和数据输出(Q)。 的低电平使输出预置或清除,而与其它输入端的电平无关。当

2021-06-04 15:40:41 94565

94565

上图是用与非门实现的D触发器的逻辑结构图,CP是时钟信号输入端,S和R分别是置位和清零信号,低有效; D是信号输入端,Q信号输出端;

2022-09-19 15:22:24 6647

6647 的输出连接,其状态由主触发器的状态决定,称为从触发器。电路结构 主从RS触发器由两个同步RS触发器组成,它们分别称为主触发器和从触发器。反相器使这两个触发器加上互补时钟脉冲。如图7.4.1所示。 工作原理: 当CP=1时,主触发器的输入门G7和G8打开

2022-10-19 19:16:03 34610

34610

在数字电路中,为协调各部分动作一致,常要求某些触发器于同一时刻工作,所以要引入同步信号。

2022-12-27 09:20:00 85131

85131 D 触发器或数据触发器是一种触发器,它只有一个数据输入“D”和一个时钟脉冲输入, 这种触发器也称为延迟触发器,经常用于许多时序电路,如寄存器、计数器等。下面一起来了解一下D触发器不同应用下的电路图。

2023-01-06 14:19:46 9743

9743 本文旨在总结近期复习的数字电路D触发器(边沿触发)的内容。

2023-05-22 16:54:29 22343

22343

锁存器和触发器有时组合在一起,因为它们都可以在其输出上存储一位(1或0)。与锁存器相比,触发器是需要时钟信号(Clk)的同步电路。D 触发器仅在时钟从

2023-06-29 11:50:18 51321

51321

,在很多应用场景中都可以用来构建序列发生器。本文将介绍使用D触发器设计序列发生器的方法和步骤。 首先,我们需要了解D触发器的基本原理和性质。D触发器是一种时序电路,它可以存储和延迟一个输入信号,并在时钟信号到来时输出

2023-08-24 15:50:17 6096

6096 在传统的异步 RS 触发器中,当输入的 R 和 S 同时为 1 时,会引发互锁问题,输出结果是不确定的。为了避免这个问题,常常使用带有使能控制的同步触发器,如带有时钟信号的 D 触发器或 JK 触发器。这些触发器在时钟边沿上才会响应输入信号,解决了异步 RS 触发器的互锁问题。

2023-08-28 15:44:35 6262

6262 的存储单元,具有时钟同步的特性。其中,D触发器是数字电路设计中使用最广泛的一种触发器类型之一,因为它具有简单、稳定和多功能等优点。

2023-08-31 10:50:19 20343

20343

由于RS触发器实现方式的不同,对输入信号抖动(即短时间内多次变化)的响应也不同。原始的电路设计可能导致RS触发器对输入信号的抖动比较敏感。

2023-09-07 15:47:45 7889

7889 D触发器,是时序逻辑电路中必备的一个基本单元,学好 D 触发器,是学好时序逻辑电路的前提条件,其重要性不亚于加法器,二者共同构成数字电路组合、时序逻辑的基础。

2023-10-09 17:26:57 6026

6026

JK 触发器的 Verilog 代码实现和 RTL 电路实现

2023-10-09 17:29:34 6642

6642

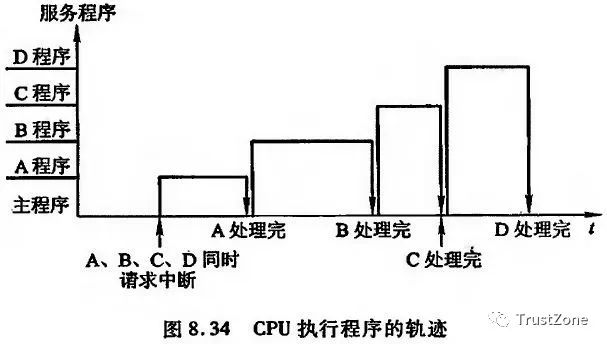

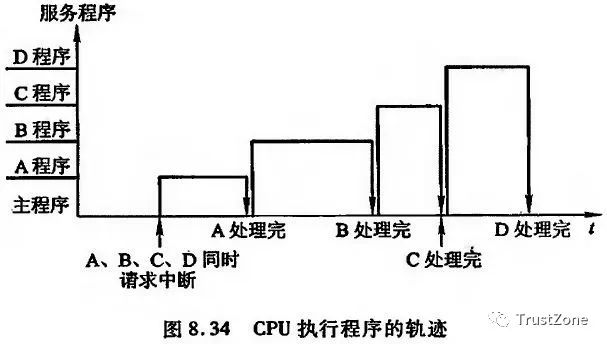

•1)屏蔽触发器和屏蔽字:程序中断接口电路中,完成触发器D,中断请求触发器INTR和屏蔽触发器MASK。 在程序中断接口电路中,有三个重要的组成部分:完成触发器D,中断请求触发器INTR和屏蔽触发器

2023-10-30 17:02:05 2731

2731

计算机的时钟节拍、频率分频、数据传输的帧同步等等。计数器可以通过级联多个RS触发器来实现,其中每个触发器的输出作为下一个触发器的输入。 频率分频器 RS触发器可以用于构建频率分频器电路。频率分频器可以将一个输入信号的频率减小为

2023-11-17 16:03:44 5535

5535 D触发器(D flip-flop)可以存储一位二进制数据的状态,因此具有记忆功能。D触发器通常用于数字电路中,用于实现寄存器、计数器等电路,可以通过时钟信号进行同步操作,使它们可以存储和操作二进制数据。值得注意的是,D触发器只能存储一位二进制数据,如果要存储更多的数据,则需要使用多位寄存器。

2023-11-29 14:52:03 6217

6217

的案例和挑战。 首先,让我们来了解一级触发器同步的概念。在计算机科学中,触发器是一种用于在特定条件下自动执行某个操作的设备或软件组件。触发器可以是硬件电路,也可以是软件程序。同步是指在两个或多个设备之间实现信息

2024-01-16 16:29:35 1027

1027 原理 两级触发器同步是一种数字电路设计技术,用于确保数据在传输过程中的可靠性。它通过两级触发器的级联来实现同步传输,可以有效地减少数据传输中的噪声、时钟抖动等因素对数据的干扰和误差。 在两级触发器同步中,两个触发器都由同一

2024-01-16 16:29:38 2541

2541 和计算机系统的设计中非常常见,它能够实现时序逻辑的控制和状态的存储。 JK触发器是由两个相互交叉的反馈线组成的。它有两个输入端J和K,一个时钟信号输入端CLK,还有一个输出端Q。当时钟信号CLK上升沿到来时,JK触发器会根

2024-01-30 13:54:53 4354

4354 D触发器的稳态 D触发器是数字电路中常用的一种存储元件,它有两种稳态,即低电平稳态和高电平稳态。当输入D为低电平时,输出Q保持为低电平;当输入D为高电平时,输出Q保持为高电平。 D触发器和RS触发器

2024-02-06 11:32:41 5586

5586 D触发器是一种常见的数字逻辑电路,它在数字系统和计算机中扮演着重要的角色。本文将详细探讨D触发器的逻辑功能、工作原理以及RD(Reset-D)触发器和SD(Set-D)触发器的作用。 首先,我们先来

2024-02-06 13:52:14 52523

52523 触发器是数字电路中常用的组合逻辑电路,在现代电子系统中有着广泛的应用。其中,最常用的两种触发器是T触发器和JK触发器。本文将详细介绍T触发器和JK触发器的区别和联系。 一、T触发器 T触发器是一种单

2024-02-06 14:04:55 7821

7821 D触发器是一种经典的时序逻辑电路,具有广泛的应用领域。它的功能包括存储和传输数据,以及在时钟信号的作用下进行状态转换。本文将探讨D触发器的功能和状态方程。 首先,让我们从D触发器的基本功能开始讨论

2024-02-18 16:28:45 17725

17725 触发方式可以有效地减少电路的功耗和提高电路的稳定性。边沿触发器有多种类型,下面介绍几种常见的边沿触发器类型。 D触发器(Data Flip-Flop) D触发器是一种最基本的边沿触发器,它具有一个数据输入端(D)、一个时钟输入端(CLK)和一个输出端(Q)。D触发器的功

2024-08-11 09:07:32 1938

1938 同步触发器,使用两个触发器(主触发器和从触发器)来实现同步操作。主触发器在时钟信号的上升沿或下降沿触发,而从触发器在相反的时钟边缘触发。这种触发方式可以消除竞争冒险,提高电路的稳定性。 边沿触发器:它是一种异步触发器,只在时钟信号的上升沿或下降沿触发

2024-08-11 09:16:37 4401

4401 定义: 主从触发器(Master-Slave Trigger)是一种用于实现时钟同步的触发器结构,它由两个触发器组成,一个为主触发器(Master Trigger),另一个为从触发器(Slave

2024-08-11 09:21:38 2229

2229 在数字电路设计中,触发器是一种非常重要的存储元件,用于存储一位二进制信息。触发器的种类很多,其中最为常见的是T触发器(Toggle Flip-Flop)和D触发器(Data Flip-Flop

2024-08-11 09:37:25 6781

6781 触发器是数字电路中的一种基本逻辑单元,用于存储和操作信息。它能够在特定的输入条件下改变输出状态,并在没有进一步输入时保持输出状态不变。时钟输入是触发器的一个重要组成部分,它提供了一个精确的时间参考点,使得触发器的状态转换能够按照预定的时间顺序进行。

2024-08-12 10:49:47 1476

1476 同步触发器和边沿触发器是数字电路中两种常见的触发器类型,它们在触发方式、工作原理、性能特点以及应用场景等方面存在显著的差异。

2024-08-12 11:26:01 3572

3572 作为双稳态电路的一种,其输出状态Q在时钟信号的上升沿或下降沿(具体取决于触发器的设计)到来时,会根据输入信号D的状态进行翻转或保持不变,从而实现对信号的存储和传输功能。 在数字电子系统中,边沿式D触发器被广泛应用于各种

2024-08-22 10:15:40 2377

2377 D触发器(Data Flip-Flop)是一种常见的数字逻辑电路元件,主要用于存储一位二进制数据。D触发器可以是电平触发的,也可以是边沿触发的,具体取决于设计和应用需求。 电平触发D触发器 1.1

2024-08-22 10:17:27 3012

3012 在数字电路设计中,触发器是一种非常重要的存储元件,用于存储一位二进制信息。触发器的种类很多,其中最为常见的有JK触发器、D触发器和T触发器等。 一、触发器的基本概念 1.1 触发器的定义 触发器

2024-08-22 10:33:51 3765

3765 引言 数字电路是现代电子技术的基础,广泛应用于计算机、通信、控制等领域。触发器是数字电路中的一种基本逻辑元件,具有存储和传递信息的功能。 触发器的基本概念 触发器是一种具有记忆功能的数字电路元件

2024-08-22 10:37:33 5059

5059 。D触发器有两个输入端,一个是数据输入端D,另一个是时钟输入端CLK;两个输出端,一个是Q输出端,另一个是Q非输出端。当CLK信号上升沿到来时,D触发器将D端的输入数据存储到Q端,实现数据的翻转。 D锁存器(Data Latch)也是一种双稳态电路,它可以存储一位

2024-08-28 09:34:17 3723

3723 与RS触发器的基本概念 D触发器 D触发器是一种具有数据输入(D)、时钟输入(CLK)和输出(Q)的存储单元。当CLK信号的上升沿或下降沿到来时,D触发器将输入端的数据D存储到输出端Q。D触发器具有以下特点: (1)数据传输:D触发器可以实现数据的同步传输,即在时钟信号的控制下,数据从

2024-08-28 09:35:37 2844

2844 将JK触发器变成T触发器,主要涉及到对JK触发器的输入端口进行适当的连接和配置,以实现T触发器的逻辑功能。以下是将JK触发器转换为T触发器的具体步骤: 步骤一:理解JK触发器和T触发器的逻辑功能

2024-08-28 09:41:19 6044

6044 :JK触发器可以存储一个二进制位(0或1),在电路中起到存储和记忆的作用。 双稳态特性:JK触发器具有两个稳定状态,即Q=0和Q=1。在没有输入信号的情况下,JK触发器可以保持当前状态不变。 同步更新:JK触发器在接收到时钟信号后,可以同步更

2024-08-28 09:48:39 7248

7248 边沿JK触发器是一种数字逻辑电路,广泛应用于数字电路设计中。它具有多种功能,包括同步操作、存储数据、实现时序逻辑等。以下是对边沿JK触发器功能的分析: 同步操作 边沿JK触发器是一种同步触发器,它在

2024-08-28 09:50:12 2291

2291

电子发烧友App

电子发烧友App

评论