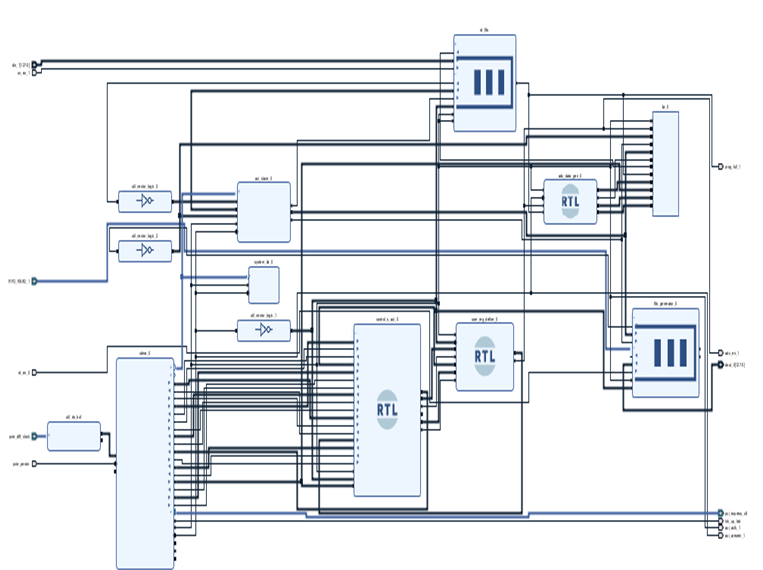

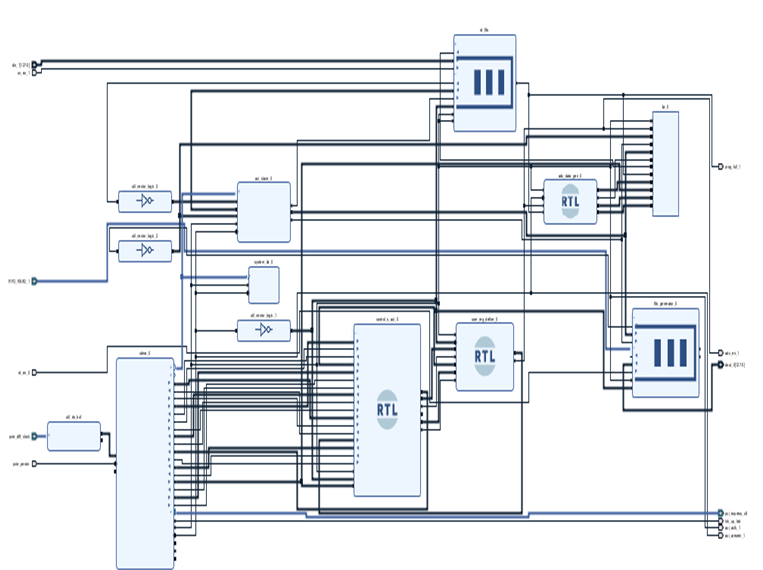

本工程的目的是在XC7K325tffg的平台上实现pcie的数据发送和接收,速率8通道2.5GB/s,首先看下本工程的PCIE部分的结构。

2022-04-21 09:36:14 3323

3323

在高速系统中FPGA时序约束不止包括内部时钟约束,还应包括完整的IO时序约束和时序例外约束才能实现PCB板级的时序收敛。因此,FPGA时序约束中IO口时序约束也是一个重点。只有约束正确才能在高速情况下保证FPGA和外部器件通信正确。

2022-09-27 09:56:09 1382

1382 的传输单元将高速数据及相关的时序信号一起发送至接收器电路。这些模块中的接收单元拥有时序调整的功能,以便在很高的速度下能可靠地采集数据。此外,这些模块通过增加数据的宽度来减缓数据传输速率,从而使FPGA

2018-11-26 11:17:24

。 FPGA与RGMII接口的PHY芯片之间的时序关系按照数据接口同步和数据采样方式属于源同步DDR采样。input delay约束对应接收方向,时序关系是中心对齐。output delay约束对应发送方向

2023-06-06 15:43:13

2、系统同步输入1、所谓的源同步输入指的是输入的数据和其对应的同步时钟,类似ADC和FPGA的相连接,对于这一类的约束比较典型的是DDR传输模式:如图所示:我们要做的约束是对接口相关的输入时钟,定义

2015-09-05 21:13:07

、LxCLKIN均以FPCA的角度来叙述),该接口由接收、控制和发送三部分组成。本设计FPGA时钟为40MHz,TS101核时钟上作在250MHz,链路口时钟设定为DSP核时钟的8分频,FPGA与DSP的实际

2018-12-04 10:39:29

、LxCLKIN均以FPCA的角度来叙述),该接口由接收、控制和发送三部分组成。本设计FPGA时钟为40MHz,TS101核时钟上作在250MHz,链路口时钟设定为DSP核时钟的8分频,FPGA与DSP的实际

2019-06-19 05:00:08

报告。FPGA与RGMII接口的PHY芯片之间的时序关系按照数据接口同步和数据采样方式属于源同步DDR采样。inputdelay约束对应接收方向,时序关系是中心对齐。outputdelay约束对应发送

2021-07-07 08:30:00

使能这两个配置也能在一定程度上改善时序收敛。 FPGA工程师的工作不只是将电路功能实现,由于器件和工具不是理想的,所以还需要研究器件特性和工具的局限,尤其是在如今算法结构越来越成熟的背景下,不断被工具折磨,也许这也是FPGA工程师的悲哀吧。

2020-12-23 17:42:10

数据发送模块,FPGA波特率发生控制模块,FPGA总体接口模块以及单片机数据接收模块。本文着重对FPGA数据发送模块实现进行说明。2FPGA数据发送模块的设计根据RS232 异步串行通信来的帧格式,在

2018-12-10 10:16:38

FPGA1中,其中FPGA1中的配置模块负责接收来自PC方软件发送的配置数据,并产生对被测FPGA的配置时序,完成配置步骤,测试模块负责发送测试激励和回收被测FPGA的响应数据,等待PC方软件的回收。系统

2020-05-14 07:00:00

,发送端是FPGA,而接收端是ADV7123芯片。如果传输的速率比较高,那么数据和时钟上升沿的严格对齐则要依靠PLL产生可调相位的时钟信号来保证。不过,我们这个25MHz或者50MHz的时钟通过较好的时序分析和约束后,则不必动用PLL。(特权同学,版权所有)图8.25 源同步接口寄存器模型

2015-07-29 11:19:04

reg的时序路径分析。(特权同学,版权所有)CMOS Sensor接口相对于FPGA来说是不折不扣的pin2reg所覆盖的约束类型。在开始这个CMOS Sensor的时序约束前,我们先来进一步认识一下

2015-08-12 12:42:14

adapt layer,信令ATM适配层)的CP(公共部分),即对高层产生的信令信息进行AAL5适配,经UTOPIA接口将ATM信元发送到路由及业务管理模块,然后再送至交换单元。3 中心控制单元的设计与实现

2009-05-25 16:38:13

5个连“1”则在其后插入1个“0”,数据发送结束后发送帧尾“7E”。FPGA设计FPGA中实现的主要是链路层协议完成HDLC数据接口的收发,并完成与DSP的数据交互,该电路由接口模块interface

2011-03-17 10:23:56

FPGA处理数据的时间,所以整个系统实现了流水线操作。1 系统的总体设计系统硬件主要由信号采集模块、FIFO、FPGA和SEP3203处理器组成。信号采集模块主要包括信号接收器和A/D转换模块。接收

2019-04-26 07:00:06

UART 内核模块是整个设计的核心,所以它也是整个设计中最为复杂的模块。由于 UART 内核模块的整体结构比较复杂,下面的内容将从模块接口、状态机设计和实现代码 3 方面介绍UART 内核的实现方法

2018-10-24 09:58:36

低电平)、8 位数据位、偶校验、停止位(1 b 高电平) , 波特率可调。 2 波特率发生模块 设计的UART 的接收和发送按照相同的波特率进行,波特率可以通过接口模块的总线接口进行设置

2015-02-05 15:33:30

拉高,对DSP 和FPGA 内部其他模块进行复位。(2)DS18B20 接口模块该模块用于实现与DS18B20 通信,读取并存储温度值。它包含2 个子模块。一、温度采集模块该模块实现与DS18B20

2019-06-18 05:00:08

大家好,Xilinx是否计划在FPGA内部构建任何功能,其中MGT与光学器件接口,提供直接光信号发送和接收,而无需分立光学模块。 ALTERA声称附有WP。问候钱德拉wp-01161-optical-fpga.pdf 863 KB

2019-10-28 06:45:31

帮助我们输入更多的信息。在pc机上,我们经常使用104键的键盘,这种键盘与pc机的接口,可分为USB接口和PS2接口,我们FPGA要实现USB接口比较困难,因为USB的接口线路,不是标准的TTL电平,而

2019-04-28 06:06:49

This is a Product Note on how to use the HP E4829B custom / UTOPIA Level 1 implementation for real-time bit error rate (BER) measurements.

2019-02-18 17:09:23

Implementation of UTOPIA level 2 with Keysight E4829B

2019-02-22 13:36:05

?以保证FPGA发送过去的数据能被外部芯片正确接收的。

FPGA通过某种通用接口(如SPI)和外部芯片通信时,FPGA如何实现才能满足芯片手册给出的时序要求呢?

2023-04-23 11:35:02

的接口,有固定的引脚和通信协议。使用FPGA实现串口通信,可分为“计算机发送数据给FPGA”和“FPGA发送数据给计算机”两部分。本节为串口接收实验,使用FPGA接收从计算机发来的数据。进行串口接收实验

2022-07-19 11:09:48

模块

字节传输控制模块以字节为单位控制 I2C 总线的数据传输。这个模块按照命令寄存器设置的内容将数据传输寄存器内容传递到 I2C 总线的接收端,或者从 I2C 总线发送端接收数据并保存到数据接收寄存器

2023-08-14 18:21:26

摘要:RS 232接口是现在最常用的一种通信接口。随着FPGA技术的高速发展,一些常见的接口电路的时序电路可以通过FPGA实现,通过这种设计可减少电路系统元件的数量,提高系统集成度和可靠性。详细阐述

2019-06-19 07:42:37

适用于该背景的控制状态机,并对控制时序作了详尽的分析。系统测试结果表明,该设计满足大容量数据的高速率存储和读取要求。一、引言随着软件无线电[1]思想的提出和FPGA技术[2]的不断发展,高速实时

2018-08-30 09:59:01

语言,他可以用来进行各种级别的逻辑设计,可以用来进行数字逻辑系统的仿真验证、时序分析和逻辑综合等,应用十分广泛。本文使用Verilog设计 SPI接口模块,实现可IP复用的通用结构。根据SPI总线

2019-05-28 05:00:05

发送到MISO 上。当CPHA=1 时,MOSI 和MISO 的时序完全相同。2 SPI 主机模块的设计本文设计的SPI 主机模块主要完成以下工作:(1) 将主机收到的8 位并行数据转换为串行

2015-01-28 14:09:51

数据流发送,通过DVI-I端口发送给显示终端显示。本设计方案中,MT9M111输出图像的分辨率为1280×960。 图1 系统采集与显示过程 在现实景物的采集与显示过程中,视频转换接口功能的实现通过以下

2018-12-11 10:59:36

。2 缓冲区接口软件设计 为了设计ARM和FPGA的缓冲区接口,首先要利用图1中的信号线实现ARM对FPGA的基本读写操作,这需要双方遵循拟定的接口时序相互配合进行,这可以通过参考相应的ARM内核

2019-05-30 05:00:03

寄存器(IR-InstruetionRegister)和数据寄存器(DR-DataRegister)中。JTAG接口模块在接收到上位机软件发送的指令后,相应的解释如表1所列。2FIash控制器和FPGA

2019-06-06 05:00:38

FPGA中实现。具体实现(1)PC/104接口逻辑:负责对PC/104的地址总线和控制总线进行译码以产生相应的命令。由于设备地址可能产生冲突,故需在接口模块中设定跳线以便灵活地改变地址空间。(2)接收

2019-04-16 07:00:04

其它设备,又可将计算机或其它设备发出的数字信号转换为429信号输出。本文介绍的总线接口板采用FPGA和DSP实现四路429信号接收通道和四路429信号发送通道,且每路通道之间相互独立。在这个接口板中

2019-06-13 05:00:06

HSDI接口的硬件结构以及接口信号的时序和功能操作基于FPGA实现HSDI接口的设计

2021-04-09 06:40:16

大家好,我想知道如何实现硬件(FPGA)中的时序报告给出的时序。我的意思是,如何测量FPGA和FPGA中输入信号的建立或保持时间与静态时间报告给出的值进行比较。FPGA怪胎以上来自于谷歌翻译以下

2019-01-15 11:07:15

)发送沿(Launch Edge):前级寄存器发送数据对应的时钟沿,是时序分析的起点;(2)捕获沿(Latch Edge):后记寄存器捕获数据对应的时钟沿,是时序分析的终点。相对于launch

2018-04-03 11:19:08

如何利用STM32接口接收和探测去实现数据的接收和发送呢?其代码是如何去实现的?

2021-11-17 07:12:00

基于51315(或者433)发送和接收模块测试一.实现功能二.硬件清单三.资料清单程序代码文档资料四.通信原理说明五.接线基于51 +315接发模块接线六.代码说明1.发送模块代码2.接收模块函数七

2022-02-18 06:44:41

设计方案。EMA的设计自动化工具--TimingDesigner,允许创建交互式时序图来获取接口规范,分析组件接口时序的特点,在项目工程师团队中沟通设计要求3002 2. 导 言FPGA的设计与高速

2009-04-14 17:03:52

请问如何采用Altera公司Cyclom系列FPGA来实现ATM层UTOPIA LEVEL2主接口,与物理层UTOPIA从接口连接?

2021-04-08 06:32:34

1、列出项目的功能要求(客户提出的产品功能要求) 2、画出硬件的系统结构框图(添加外设) 3、框图中每个外围接口都对应有一个接口转换模块接口转换模块的作用是将外围器件的接口时序转为通用的接口时序,或者

2020-01-04 17:03:20

各位大哥大姐求一个 基于FPGA的PS/2鼠标接口的设计与实现的程序设计可有偿~~~~联系qq392404578

2016-05-11 14:17:48

控制方案。 成帧器、网络处理器与相关器件间通常使用的接口包括Utopia接口、POS-PHY接口、SPI接口和Flexbus接口。每个接口的后缀为 level X,其级别表明标称数据速率。Level 2

2019-05-15 07:00:10

本帖最后由 一只耳朵怪 于 2018-5-22 14:54 编辑

标准SPI方式调试。关于SPI的“接收/发送中断”有些疑惑:使用HalCoGen工具时,发现SPI2模块的中断使能TXINT

2018-05-22 02:12:23

,使用FPGA实现SPI通信接口是切实可行的,本文作者创新点:1、将总线控制信号封装成指令,使用者只需通过发送指令的方式操作,避免了复杂的时序逻辑设计问题。2、可以在SPI工作过程中随时调整配置参数。3

2019-05-05 09:29:34

) 232接口模块 该模块用于实现串口数据输出,它包含 2个子模块:一、串口波特率模块 串口通信协议要求数据收发双方有相同的波特率。该模块用于设定串口通信波特率。二、串口发送模块双口 RAM模块将数据存储

2020-08-19 09:29:48

DVI和HDMI标准是什么?采用FPGA实现DVI/HDMI接口具有什么优点?基于ECP2M的接收/发送功能怎么实现?

2021-05-07 07:00:06

芯片提供视频数据的模拟通道,共同汇集到DVI-I输出接口,传送到数字显示器或模拟显示器上显示。 图2 硬件构架框图 输出图像的分辨率要求FPGA与TMDS发送芯片之间传送数据的带宽在100M

2019-05-05 09:29:33

驱动模块对WM8731写控制字的时序仿真如图8所示。图中各引脚定义如表2所示。 4 结 语 利用FPGA对音频编解码芯片WM8731进行接口电路的设计,实现了控制接口与数字音频接口的统一控制,简化

2019-05-22 05:01:13

设计中对集成到SOPC系统上的VGA接口的地址赋值为0x1后,数据写入0x1,VGA接口控制器接收到数据,就会根据设计产生VGA时序信息及RGB信号,在屏幕上显示图像。图3为整个一维信号VGA显示系统

2019-06-04 05:00:12

USB数据与并行I/O口数据的交换缓冲区。FIFO实现与外界(微控制器、FPGA或其它器件)的接口,主要通过8根数据线D0~D7、读写控制线RD#和WR#以及FIFO发送缓冲区空标志TXE#和FIFO接收

2019-04-22 07:00:07

USB数据与并行I/O口数据的交换缓冲区。FIFO实现与外界(微控制器、FPGA或其它器件)的接口,主要通过8根数据线D0~D7、读写控制线RD#和WR#以及FIFO发送缓冲区空标志TXE#和FIFO接收

2019-04-26 07:00:12

和更低的实现成本。1 JTAG接口模块的设计为了将配置码流写入Flash存储器,上位机软件通过JTAG下载线与JTAG接口模块连接。JTAG接口模块接收上位机软件发送的JTAG信号,从中提取出JTAG

2019-05-30 05:00:05

和配置统计两大功能:第一、接收MAC层处理子模块发送过来的数据片,完成MAC帧重组和十路数据合路处理,再根据MAC帧封装的三层协议类型实现数据包的分类处理,按照不同的处理要求把数据包分别送B接口、F接口

2019-04-29 07:00:07

每个处理帧将预观测的变量结果以DMA的方式打包向上位机发送。FPGA实现ADSP-TS101的Linkport接口与CY7C68013A之间的双向数据缓冲和接口协议转换。考虑到CY7C68013A中

2019-05-31 05:00:04

介绍了利用Altera 公司的Stratix GX 系列FPGA 器件实现POS-PHY Level 4 接口协议的工作原理、设计思想和电路结构,并详细讨论了一种计算128 位数据的4 位对角交叉奇偶校验码DIP-4 的适合

2009-08-17 11:09:16 7

7 为了使计算机能够通过串口控制FPGA 的输出信号,笔者根据异步串行通信的原理,设计了简便易行的FPGA 串行通信接口系统,并应用VHDL 语言在FPGA 内部集成了串行接收模块,具有较强

2009-09-24 15:52:56 18

18 基于FPGA的SPI自动发送模块的设计:一、摘要:SPI 接口应用十分广泛,在很多情况下,人们会用软件模拟的方法来产生SPI 时序或是采用带SPI 功能模块的MCU。但随着可编程逻辑技

2009-10-04 08:44:40 25

25 摘 要:介绍了基于现场可编程门阵列(FPGA)的以太网MAC子层协议的硬件实现方法.硬件结构上由控制模块、发送模块和接收模块3个部分组成,发送模块和接收模块采用状态机控制数据发

2010-07-15 11:27:29 24

24 本文详细分析了ADSL系统中ATM层和物理层之间的UTOPIA LEVEL2接口时序,采用FPGA实现了UTOPIA接口设计,应用在ADSL系统中,数据收发正确,工作稳定;该方案的实现对解决现有专门通信芯

2010-07-28 16:54:10 19

19 介绍了一种利用FPGA实现DVB—ASI视频传输流发送系统的组成原理和实现方法。不同于使用Cypress公司的CY7B923的方法,使用FPGA编程实现ASI接口转换与发送功能,具有更大的灵活性,且接

2010-07-28 17:45:32 22

22 摘 要: 本文采用Altera的CPLD实现了PCI总线至UTOPIA接口的逻辑转换控制,为低成本实现ATM终端奠定了基础。

2006-03-11 13:16:50 864

864

如何有效的管理FPGA设计中的时序问题

当FPGA设计面临到高级接口的设计问题时,EMA的TimingDesigner可以简化这些设计问题,并提供对几乎所有接口的预先精确控制。从简单

2009-04-15 14:19:31 659

659

模块化FPGA设计在某雷达接收机中的应用

0 引言 目前基于FPGA和DSP结构的软件无线电技术被广泛应用在数字接收机设计中,雷达接收机领域的数字化技术

2009-11-24 17:17:41 831

831

为实现某专用接口装置的接口功能检测,文中详细地介绍了一种34位串行码的编码方式,并基于FPGA芯片设计了该类型编码的接收、发送电路。重点分析了电路各模块的设计思路。电路采

2012-06-18 12:37:09 41

41 本文设计一个通信接口模块,通过光纤接口与中心机连接,实现对前端受控模块的远程控制和状态监测。

2012-09-03 15:59:18 4808

4808

FPGA与SPI接口程序:使用xc3s400,时钟50Mhz,串行DA 使用max544,max544使用的是SPI接口,所以要模拟SPI发送方式。其实最重要的就是精确的模拟出发送数据的时序图。有用的就下吧。

2012-10-23 12:35:09 194

194 电子发烧友网核心提示 :RS 232接口是现在最常用的一种通信接口。随着FPGA技术的高速发展,一些常见的接口电路的时序电路可以通过FPGA实现,通过这种设计可减少电路系统元件的数量

2012-11-27 10:28:11 5937

5937 FPGA 设计人员在满足关键时序余量的同时力争实现更高性能,在这种情况下,存储器接口的设计是一个一向构成艰难而耗时的挑战。Xilinx FPGA 提供 I/O 模块和逻辑资源,从而使接口设计变

2013-03-14 15:16:07 71

71 当你的FPGA设计不能满足时序要求时,原因也许并不明显。解决方案不仅仅依赖于使用FPGA的实现工具来优化设计从而满足时序要求,也需要设计者具有明确目标和诊断/隔离时序问题的能力。

2014-08-15 14:22:10 1169

1169 简单的nrf24l01模块应用,发送字符,接收端数码管显示

2017-04-27 16:13:30 21

21 本篇应用说明中,主要描述通过使用串行通信接口IICA,实现单主系统中主发送/接收通信(地址发送、数据发送与接收)的方法。 IIC通信概要

2017-09-13 10:24:11 3

3 本篇应用说明介绍了通过使用串行接口IICA 实现从发送和接收。单主系统使用IICA 实现从操作(地址接收、数据发送和接收)。 硬件配置

2017-09-13 11:00:03 10

10 SPI 接口应用十分广泛,在很多情况下,人们会用软件模拟的方法来产生SPI 时序或是采用带SPI 功能模块的MCU。但随着可编程逻辑技术的发展,人们往往需要自己设计简单的SPI 发送模块。本文介绍

2017-10-19 10:33:01 18

18 基于FPGA的高速DSP与液晶模块接口的实现

2017-10-19 13:46:23 3

3 一个好的FPGA设计一定是包含两个层面:良好的代码风格和合理的约束。时序约束作为FPGA设计中不可或缺的一部分,已发挥着越来越重要的作用。毋庸置疑,时序约束的最终目的是实现时序收敛。时序收敛作为

2017-11-17 07:54:36 2326

2326

针对八通道采样器AD9252的高速串行数据接口的特点,提出了一种基于FPGA时序约束 的高速解串方法。使用Xilinx公司的FPGA接收高速串行数据,利用FPGA内部的时钟管理模块DCM、位置约束

2017-11-17 12:27:01 6488

6488

现有的工具和技术可帮助您有效地实现时序性能目标。当您的FPGA 设计无法满足时序性能目标时,其原因可能并不明显。解决方案不仅取决于FPGA 实现工具为满足时序要求而优化设计的能力,还取决于设计人员指定前方目标,诊断并隔离下游时序问题的能力。

2017-11-18 04:32:34 2951

2951 设计,详述了各子模块的设计思路和方法,给出了它们的仿真时序图。综合实现后,将程序下载到FPGA芯片中,运行正确无误。又经长时间发送和接收测试,运行稳定可靠。

2017-11-18 11:33:01 5153

5153 SPI接口应用十分广泛,在很多情况下,人们会用软件模拟的方法来产生SPI时序或是采用带SPI功能模块的MCU。但随着可编程逻辑技术的发展,人们往往需要自己设计简单的SPI发送模块。本文介绍一种基于FPGA的将并行数据以SPI串行方式自动发送出去的方法。

2017-11-24 15:32:02 1807

1807

作为赛灵思用户论坛的定期访客(见 ),我注意到新用户往往对时序收敛以及如何使用时序约束来达到时序收敛感到困惑。为帮助 FPGA设计新手实现时序收敛,让我们来深入了解时序约束以及如何利用时序约束实现

2017-11-24 19:37:55 4903

4903

某鱼雷声自导的硬件系统使用了百兆网络交换机实现DSP之间的互联。交换机在MAC和PHY之间的接I=I是RMII,但DSP没有相应的外围设备与它匹配。因此必须在FPGA中设计RMII的通讯模块,完成DSP数据格式向RMII数据格式的转化。在设计中将该通讯模块分为发送状态机和接收状态机两部分

2018-10-18 16:46:51 64

64 2018年以来,因为驾驶员高估了特斯拉Autopilot功能,特斯拉车主在启用Autopilot功能后,发生过一些备受关注的事故,包括驾驶员致死事故。虽然我们都知道严重依赖Level2功能的Autopilot是很危险,但确切的风险很难量化。

2018-11-06 11:35:55 1167

1167 的UART的实现方法,具体描述了发送、接收等模块的设计,恰当使用了有限状态机,实现了FPGA上的UART的设计,给出仿真结果。

2020-07-07 15:51:05 7

7 的实现方法,具体描述了发送、接收等模块的设计,恰当使用了有限状态机,实现了FPGA上的UART的设计,给出仿真结果。

2020-07-07 17:28:03 10

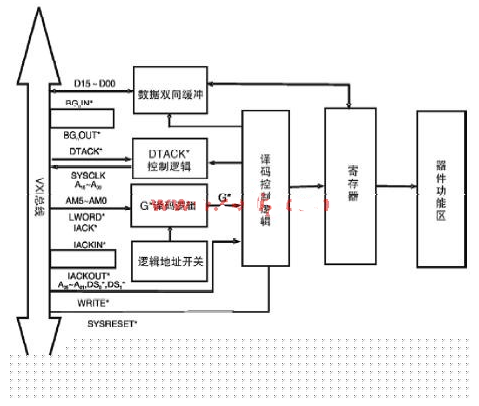

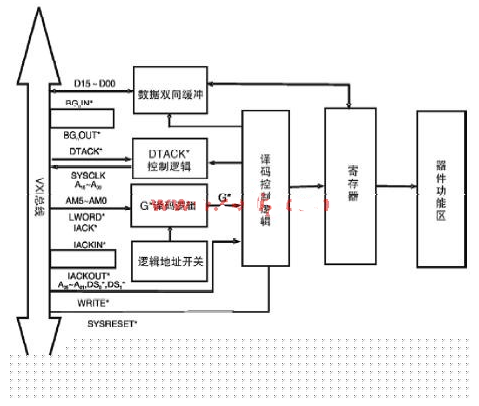

10 采用;另一种是利用中、小规模电路基PAL、GAL、CPLD和FPGA实现。通过利用FPGA实现模块与VXI总线接口的设计过程中,总结出一些通用的设计思路。

2020-07-27 18:11:22 789

789

FPGA完成ARINC429总线数据的接收。重点介绍接口电路设计和FPGA中的软件开发,与传统的ARINC429总线数据接收系统相比,具有接口电路简单、具备一定的抗干扰能力、不受协议芯片速率限制等优点.此方法已成功应用于产品中。并对其他串行总线数据接收具有借鉴意义。

2021-02-03 15:53:00 38

38 基于FPGA的GPS接收机实现说明。

2021-04-09 14:01:04 51

51 基于51 315(或者433)发送和接收模块测试一. 实现功能二. 硬件清单三. 资料清单程序代码文档资料四. 通信原理说明五. 接线基于51 +315接发模块接线六.代码说明1. 发送模块代码

2021-12-23 19:28:39 14

14 433模块是一种常用的无线通信模块,用于实现短距离无线通信。在433模块中,一般有发送和接收两种模式。

2023-06-12 17:41:01 7277

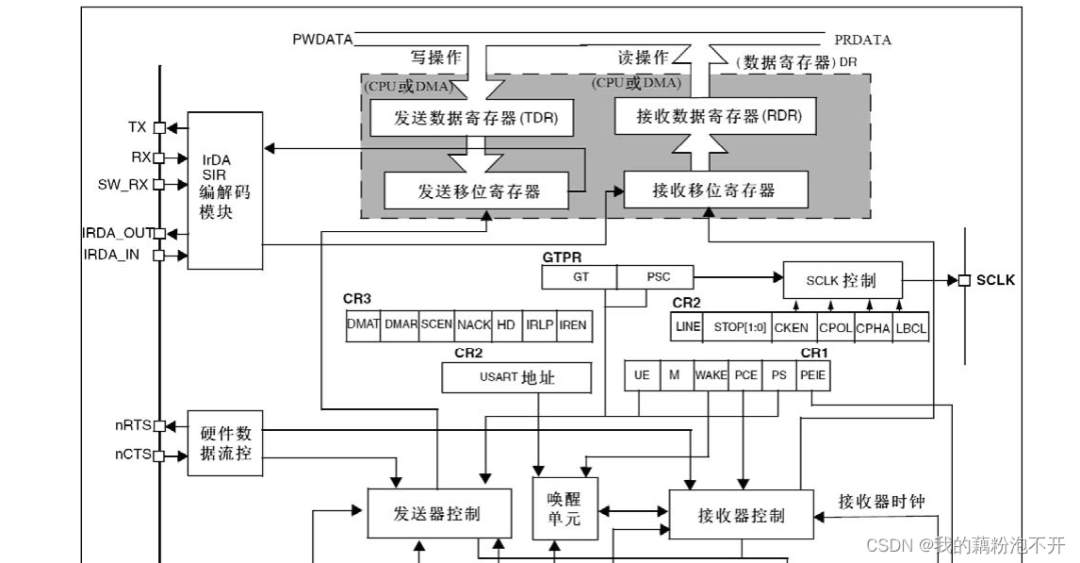

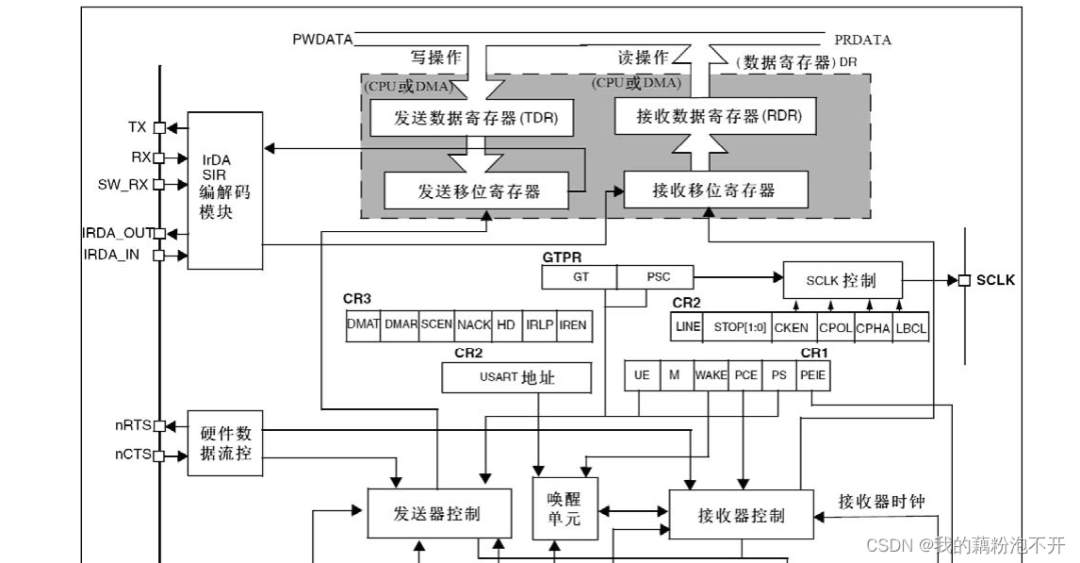

7277 USART是STM32内部集成的硬件外设,可以根据数据寄存器的一个字节数据自动生成数据帧时序,从TX引脚发送出去,也可以自动接收RX引脚的数据帧时序,拼接成一个字节数据,存放在数据寄存器里。 当配置

2023-11-10 16:04:53 512

512

电子发烧友App

电子发烧友App

评论