1、 概述

随着信息社会的发展,数据交换,网上交易等活动日益频繁,从而网络安全成为人们关注的重要问题。随着信息技术的发展与应用,信息安全的内涵也在不断延伸,从最初的信息保密性发展到信息完整性、可用性、可控性和不可否认性,进而又发展为攻(攻击)、防(防范)、测(检测)、控(控制)、管(管理)、评(评估)等多方面的基础理论和实施技术。目前对于安全性有以下三个指标:身份验证、数据完整性和机密性。

HMAC_SHA1算法在身份验证和数据完整性方面可以得到很好的应用,在目前网络安全也得到较好的实现。然而大多数应用通过软件实现,但其安全性很难得到真正的保障,于是研究安全算法的硬件实现已成为热点。本文通过对算法和现场可编程芯片特点的分析,优化设计和实现了硬件系统的HMAC_SHA1_96算法应用方案。

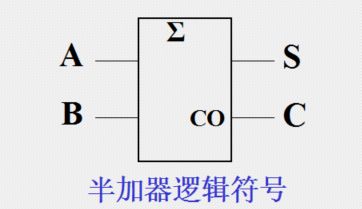

2、 SHA1函数

SHA1函数是由美国国家标准和技术局和美国国家安全局设计的与DSS一起使用的安全散列算法SHA,并作为安全散列标准(SHS)的联邦信息处理标准(FIPS)而公布,SHA1是SHA的修订版。当输入长度小于2 64bit消息时,输出160bit的摘要,其算法步骤如下:

步骤一:填充附加位。一般经过填充使报文长度512取模余64bit。该步骤通常是需要的,即使报文长度已经是所希望的长度。因此填充长度范围为1到512,最高位为1,其余为0。

步骤二:附加报文长度值。即把一个64bit的报文长度数附加在上述报文之后(高字节优先),从而达到512bit的倍数。

步骤三:初始化变量。可以使用160bit的缓存(即160bit寄存器)来存放该散列函数的初始变量、中间摘要及最终摘要,但首先必须初始化, 给初始变量赋值,即:

A=0x67452301,B=0xefcdab98, C=0x98badcfe,D=0x10325476,E=0xc3d2e1f0

步骤四:处理512bit报文分组。在该步骤中包括四个循环,每个循环有20个处理步骤,而每个循环对 B﹑C﹑D所用的非线性函数不同,并且所用的常数也不同:

对于t=0~19,

ft (B,C,D)=(B∧C )∨((¬B)∧D),

Kt=0x5a827999

对于t=20~39,

ft (B,C,D)=B⊕C ⊕D,

Kt=0x6ed9eba1

对于t=40~59,

ft (B,C,D)=(B∧C )∨(B∧D)∨(C∧D),

Kt=0x8f1bbcdc

对于t=60~79,

ft (B,C,D)=B⊕C ⊕D,

Kt=0xca62c1d6

注:∧表示“与”;∨表示“或”;⊕表示“异或”;¬表示“取反”。

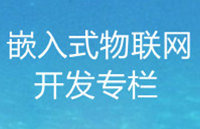

在每一步骤中都将执行如下的算法过程(图1)。

归纳为以下形式﹐其中 《《《 表示循环左移: A’, B’, C’, D’, E’← ((A《《《5) + ft (B,C,D)+Et +Wt +Kt ), A, (B《《《30), C, D 由于我们输入的是16个32bit消息,而SHA1运算需要80个32bit数据,所以存在一个由512bit 消息生成2560bit数据的转换过程(即生成W运算) ,其转换机制如下:

对于t=0~15, W t=Mt;

对于t=16~79,

Wt=(M t-3⊕Mt-8⊕Mt-14 ⊕Mt-16)《《《1。

步骤五:结果输出。512bit报文运算完就输出 160bit的报文摘要。

3、HMAC_SHA1_96算法

HMAC_SHA1_96算法[2,3,6] 是基于单向散列函数SHA1和以密钥为基础的完整性检查验证机制,它是从生成的160bit摘要中选择从高到低的96bit作为最终输出。在该算法中主要就是SHA1函数和HMAC算法。它的作用在于生成摘要放在消息后面以验证消息在传输时是否受到修改或变动,保证消息的完整性。根据HMAC的定义,本设计的HMAC_SHA1_96算法原理图如图2。

图2算法的几点说明:① _ipad表示补位后的密钥与ipad 异或的结果,K_opad表示补位后的密钥与opad异或的结果;② 次SHA1运算包括生成W运算;③ 由SHA1运算输出的结果是经过加法处理的结果;④ 虚线部分表示图上忽略的信息分组和相应的SHA1运算部分;⑤ 如果只有512bit消息,则第一轮只需进行两次SAH1运算,就转到第二轮。图2又可写成如下的表达式:

SHA1( K XOR opad, SHA1(K XOR ipad, M) )

其中 K是密钥补位后的新值,即在密钥后补0使之为512bit;ipad是0×36重复16次的一个数组;opad是0×5c重复16次的一个数组;M是消息;XOR表示异或运算;SHA1是安全散列函数。

4、 硬件设计

针对以上算法分析和实现流程特点,结合 FPGA芯片的硬件结构,进行如下的硬件系统设计和优化。

4.1使用RAM结构

在HMAC_SHA1_96算法体系中,有大位数的数据存储,如果要用寄存器来实现,需要大约7000左右的寄存器,占用大量的FPGA芯片资源,这是因为FPGA芯片上,每个LE(逻辑单元)单元只有一个寄存器,这样每个LE单元上其它硬件资源将会浪费。然而FPGA芯片上大量的ESB(嵌入式系统块)资源没有充分利用,而ESB可以用来实现各种类型的存储模块,如RAM、ROM、FIFO和CAM等,在这种情况下,可以采用ESB实现RAM来代替寄存器,从而节省LE硬件资源,并且RAM存储数据,控制起来比寄存器方便很多。

4.2 重复利用相同模块

正如前面算法所述,SHA1算法是由80次运算组成的,而每次运算的结构又是一样的,如果采用水线形式的运算模式,利用80个同样的模块,会占用很多的硬件资源,不符合优化设计的要求,因此可以先优化设计出一个模块,再对该模块复用80 次,每一次运算的结果需存入寄存器,以便送入下一次运算,这样可极大地优化利用FPGA硬件资源。

4.3 模块划分

HMAC_SHA1_96算法体系的硬件实现,必会存在与外围电路的数据握手传输。由于外围电路(8255或CPU)的工作时钟频率与所设计的芯片工作时钟频率不一样,要让设计芯片与外围电路协调工作,就必须专门设计输入输出接口电路,再设计出核心处理模块,从而不受外界电路工作环境影响。由此,可以将本设计分为三个部分:输入模块、算法实现模块和输出模块。

4.3.1 输入模块

由于输入模块会跟外围电路(如8255)连接进行信号或数据传输,根据握手信号ACK和OBF,每次输入8bit数据写到64×8bit的RAM,需要64 次,而外围电路什么时候输入数据由内部信号sha_end控制,该模块的输出一次为32bit,所以相当于一次读4×8bit数据。

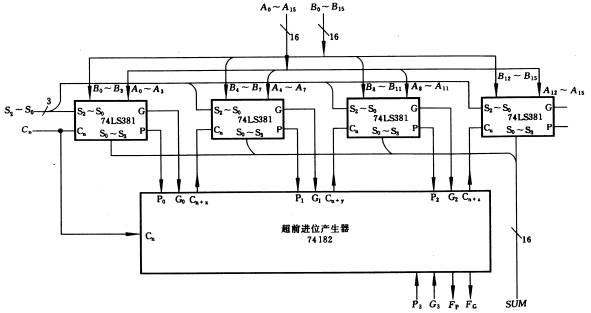

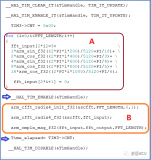

4.3.2 算法实现模块

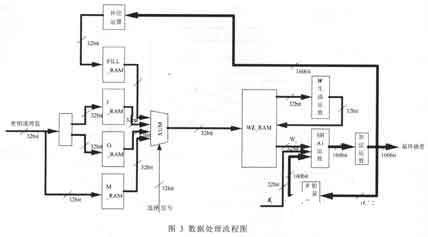

该模块主要进行HAMC_SHA运算,输出160bit摘要,其数据处理流程图见图3(图中 M_RAM用来存储消息),其中又可以分为以下几个主要部分:

① 密钥输入处理部分。处理密钥时需要先对其进行异或运算,然后把其写入两个32×16bit的 RAM,假设分别为I_RAM和O_RAM。I_RAM里数据在第一轮SHA1算法首先运算,而O_RAM 里的数据要到第二轮才开始运算。

② 生成W处理部分。 由于SHA1函数中要进行80次运算,每次运算采用不同的32bit W值,而输入的只有16个32bit数据,于是该算法采用四个不同的W值进行异或运算生成新的W值。这四个W值是从80×32bit的W_RAM读出的,而生成新的 W值再依次写入该RAM中没有使用的位置。

③ SHA1运算部分。是设计的核心部分,需要完成80次运算,每次从32×80bit RAM读出一个32bit W值,最终生成160bit摘要。

④ 摘要处理部分。主要对每一次SHA1运算后生成的摘要与本次的初始密钥进行加法运算,作为下次SHA1运算的初始密钥,或者作为最终输出摘要,或者作为下一轮SHA1运算的消息输入。

⑤ 摘要补位部分[6] 。对第一轮生成的160bit摘要进行补位,方法为:[160]~[190] 0[191] 1 [192]~[479] 0 [480]~[511]=1010100000,将此值写入一个16×32bit的FILL_RAM。

4.3.3 输出模块

同输入模块一样,由于同外围电路进行信号或数据传输,根据握手信号STB和IBF,每次输出8bit数据到外围电路,但该部分主要是一个8×12bit RAM,可以一次写入96bit数据。

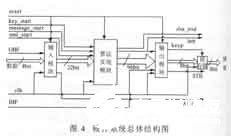

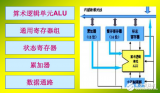

4.4 硬件系统总体结构

在数据输出端加锁存器是为了保证输出数据被外围电路采样之前始终有效,从而达到本设计与外围电路协调工作的目的。结构图如图4。

5、 FPGA实现

我们知道,FPGA芯片内部结构是由逻辑阵列块(LAB)、嵌入式系统块(ESB)、快速通道互联和输入输出单元(IOE)组成。LAB是由10个LE、LE 间关联的进位链﹑级连链﹑LAB控制信号和LAB局部互连构成,可以实现快速运算通道,特别适合本设计算术运算单元的硬件实现。ESB如前所说,可以用来实现不同的存储模块,特别适合于大位数的数据存储。快速通道是用来实现LE之间,ESB 与I/O之间的快速互连,并且具有高扇出能力,它是一系列纵横交错的连续式分布通道,能够得到高性能和快速的信号传输,提高本设计运算效率和信号的稳定性。I/O单元由一个双向缓冲器和一个寄存器组成,含有可编程延时,可确保零保持时间或最小的时钟到输出时间,减少设计数据输出的毛刺现象。另外FPGA可以重复使用,以方便修改代码或参数时再重新配置FPGA。

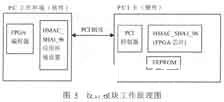

本设计采用Altera的APEX20KE160EQC240_1X 芯片实现,其功能模块及PC接口原理图见图5。

图中FPGA编程器采用QuartusⅡ2.0软件, HMAC_SHA1_96应用环境设置主要配置软件控制HMAC_SHA1_96的运行机制,PCI控制器用来控制FPGA芯片与PCI BUS的通讯。先通过QuartusⅡ2.0软件对代码布局布线生成pof文件或sof文件, pof文件可直接用来配置FPGA,但每次使用时必须重新配置;而sof文件可以先存入EEPROM,再由 EEPROM对FPGA配置,每次上电前由EEPROM配置,这样可以直接应用于信息安全硬件系统中。

责任编辑:gt

电子发烧友App

电子发烧友App

评论