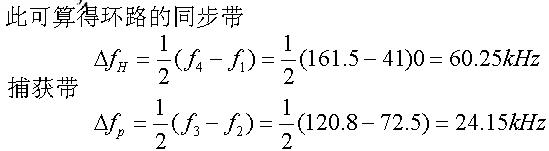

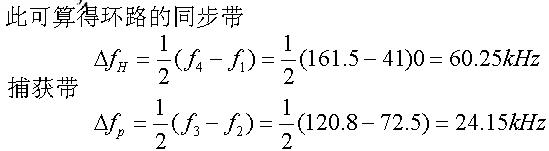

本文采用一种基于比例积分(PI)控制算法的环路滤波器应用于带宽自适应的全数字锁相环,建立了该锁相环的数学模型

2010-10-14 10:03:25 1791

1791

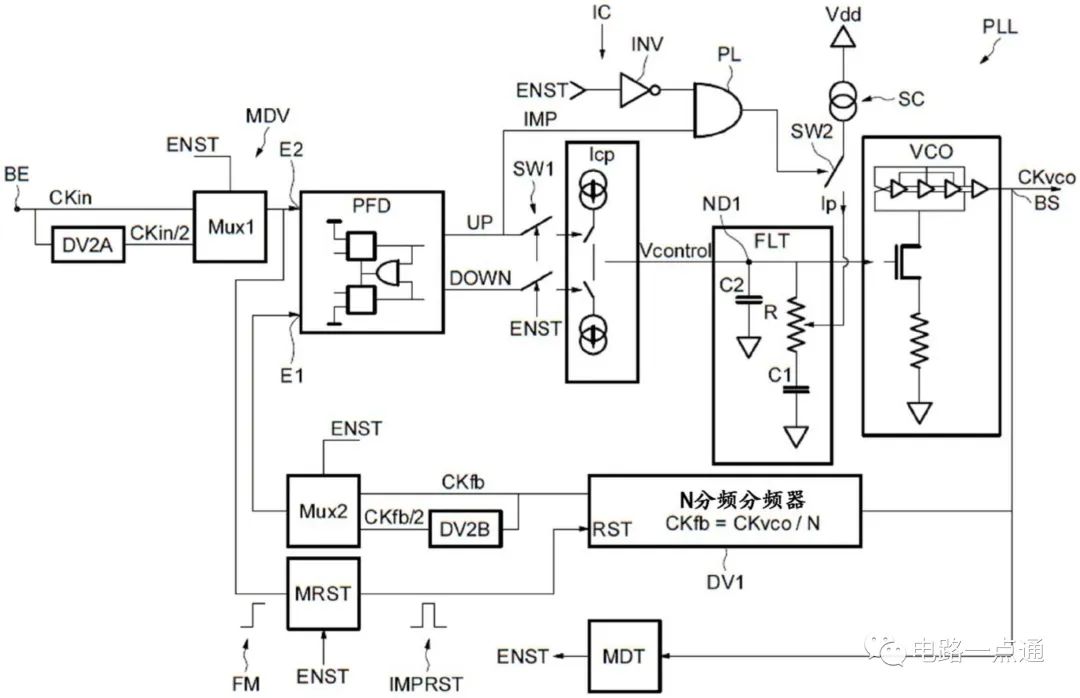

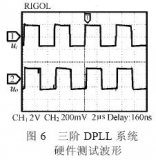

本文针对传统锁相环所存在的锁相范围窄、环路带宽和控制参数固定、以及提高锁相速度与减小稳态误差相互制约等问题,提出了一种新型带宽自适应全数字锁相环的设计方案。该设计方案中的系统采用比例积分控制

2014-01-17 11:33:47 3704

3704

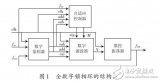

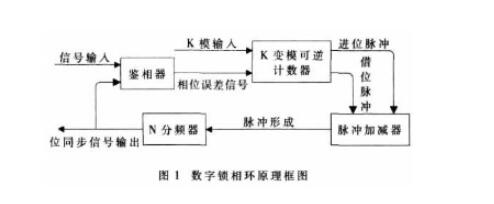

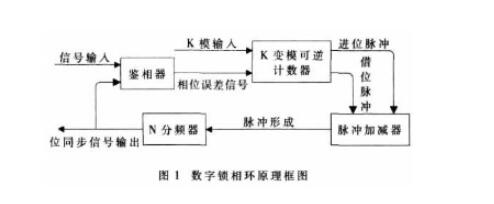

本文在说明全数字锁相环的基础上,提出了一种利用FPGA设计一阶全数字锁相环的方法,并给出了关键部件的RTL可综合代码,并结合本设计的一些仿真波形详细描述了数字锁相环的工作过程,最后对一些有关

2018-10-25 09:17:13 9370

9370 该文章是完全原创,用最简洁的语言讲清楚FPGA实现负反馈的精要。震撼!FPGA实现负反馈控制纯数字锁相环!.zip (225.26 KB )

2019-04-30 04:50:41

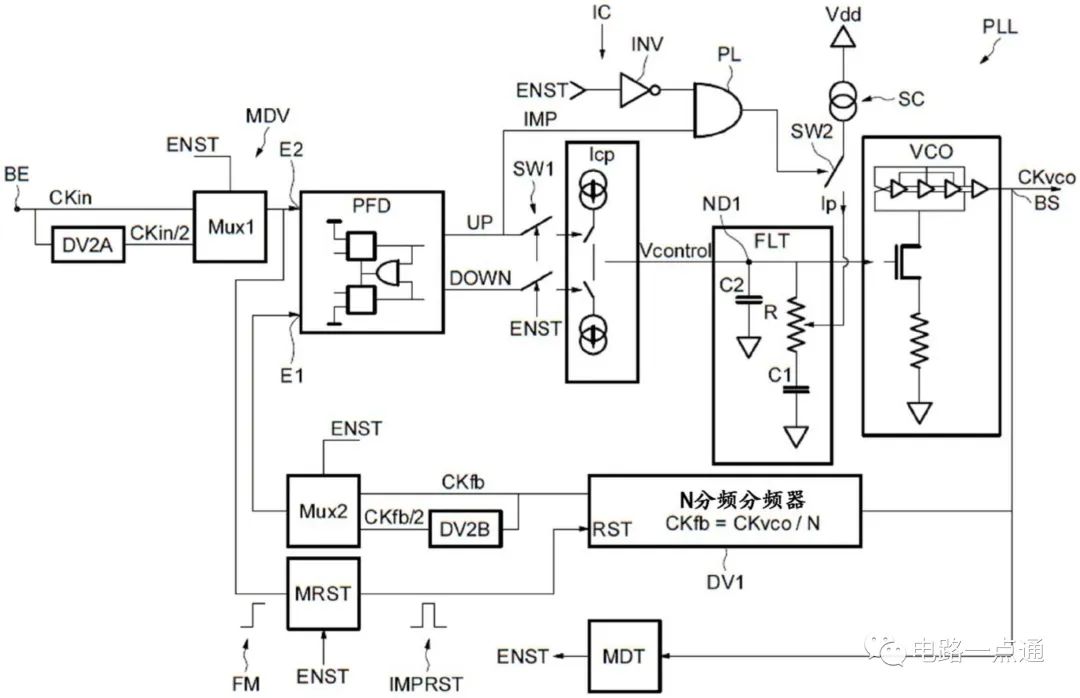

Phase-Locked Loop)逐步发展起来。所谓全数字锁相环,就是环路部件全部数字化,采用数字鉴相器、数字环路滤波器、数控振荡器构成锁相环路,并且系统中的信号全是数字信号。与传统的模拟电路实现的锁相环

2010-03-16 10:56:10

本帖最后由 gk320830 于 2015-3-7 20:18 编辑

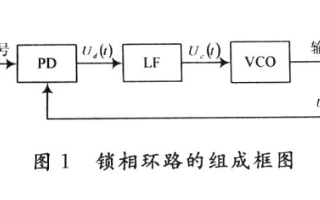

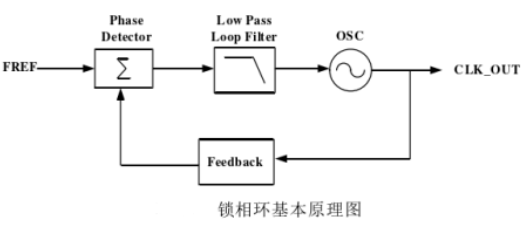

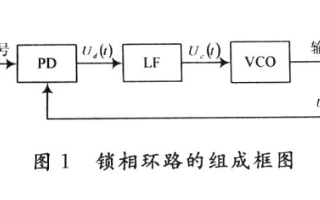

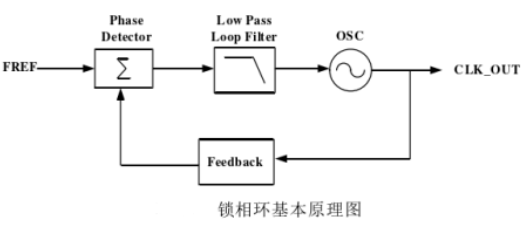

锁相环的原理,特性与分析所谓锁相环路,实际是指自动相位控制电路(APC),它是利用两个电信号的相位误差,通过环路自身调整作用,实现频率准确跟踪的系统,称该系统为锁相环路,简称环路,通常用PLL 表示。

2008-08-15 13:18:46

锁相环路中的反馈信号是正反馈还是负反馈呢?

2023-04-13 11:28:35

锁相环路是一种反馈控制电路,简称锁相环(PLL,Phase-Locked Loop)。锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。因锁相环可以实现输出信号频率对输入信号

2022-01-11 06:34:28

锁相环路由哪些组成?它的基本特性是什么?应用于哪些领域?

2021-04-12 06:58:54

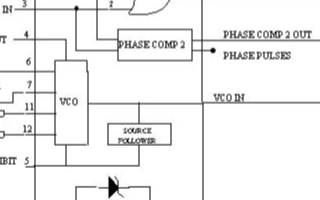

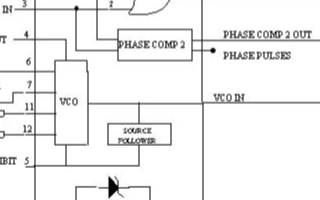

介绍了锁相环路的基本原理,分析了集成锁相环芯片ADF4106的工作特性,给出了集成锁相环芯片ADF4106的一个应用实例,为高频频率合成器的设计提供了很好的思路。 关键词:ADF4106,锁相环,频率合成器,环路滤波器

2019-07-04 07:01:10

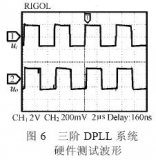

HDL硬件描述语言对优化前后的算法进行了编码实现。仿真和实验结果表明,优化后的数字三相锁相环大大节省了FPGA的资源,并能快速、准确地锁定相位,具有良好的性能。关键词:FPGA;三相锁相环;乘法复用;CORDIC

2019-06-27 07:02:23

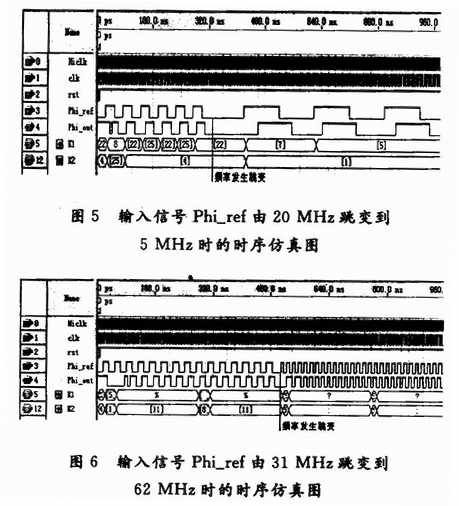

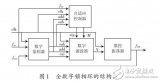

随着集成电路技术的不断进步,数字化应用逐渐普及,在数字通信、电力系统自动化等方面越来越多地运用了数字锁相环。它的好处在于免去了模拟器件的繁琐,而且成本低、易实现、省资源。本文综合以上考虑,在一片FPGA中以Quartus II为平台用VHDL实现了一个全数字锁相环功能模块,构成了片内锁相环。

2019-10-10 06:12:52

锁相环是什么工作原理?如何采用FPGA与频率综合器ADF4111相结合的方法实现数字锁相式频率源的设计?

2021-04-14 07:00:20

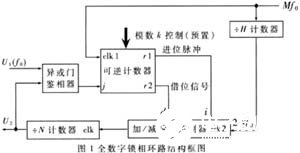

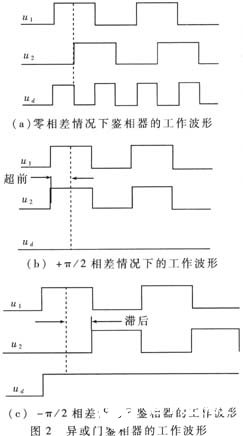

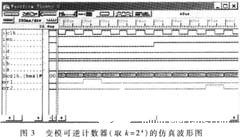

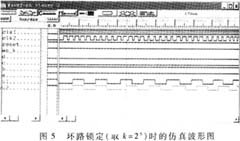

全数字锁相环由那几部分组成?数字锁相环的原理是什么?如何采用VHDL实现全数字锁相环电路的设计?

2021-05-07 06:14:44

由于一般的晶振受限于工艺与成本,做不到很高的频率,可在需要高频应用时,由相应的器件VCO,实现转成高频,但并不稳定,故利用锁相环路来实现稳定且高频的时脉冲讯号。本例通过MC9S12XS128这款

2021-12-10 06:26:47

经典数字锁相环路结构及工作原理是什么?改进的数字锁相环结构及工作原理是什么怎样对改进的数字锁相环进行仿真?

2021-04-20 06:47:12

数字锁相环频率合成系统的工作原理CPU控制数字锁相环频率合成系统FPGA实现

2021-04-09 06:20:37

我刚接触锁相环没多长时间,最近想使用ADF4106搭建一个双环锁相环,我阅读的资料都没有说主环路环路滤波器参数计算问题,我想咨询专家ADIsimPLL是否可以仿真计算双环锁相环,如果可以具体怎么考虑,如果可以告诉我一些主环路环路带宽的知识就更好了.

2019-03-07 10:34:03

概述:LMX2430是一款高频锁相环路芯片,它可在2.25V至2.75V的电压范围内操作。这三款芯片的其他功能包括可随意选择的同步或异步停机模式、1mA或4mA的可编程电荷泵电流、内置超时计数器的快速锁定技术、...

2021-04-08 07:24:00

LMX2433是一款高频锁相环路芯片,它可在2.25V至2.75V的电压范围内操作。这三款芯片的其他功能包括可随意选择的同步或异步停机模式、1mA或4mA的可编程电荷泵电流、内置超时计数器的快速锁定

2021-04-13 07:27:00

高频锁相环路LMX2434资料下载内容包括:LMX2434引脚功能LMX2434内部方框图

2021-03-29 06:27:34

第1章 锁相环路的基本工作原理第1节 锁定与跟踪的概念第2节 环路组成第3节 环路的动态方程第4节 一阶锁相环路的捕获、锁定与失

2008-04-21 08:52:00 155

155 智能全数字锁相环的设计

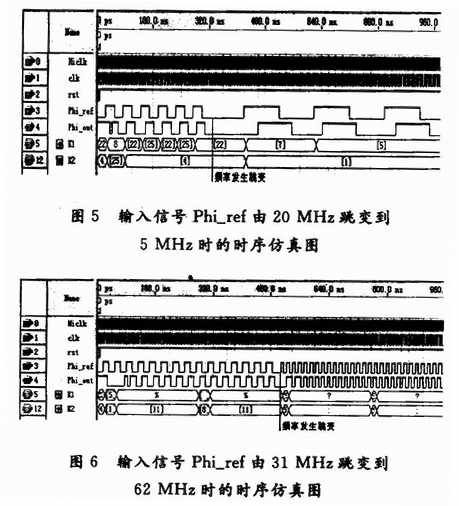

摘要: 在FPGA片内实现全数字

2008-08-14 22:12:51 56

56 所谓锁相环路,实际是指自动相位控制电路(APC),它是利用两个电信号的相位误差,通过环路自身调整作用,实现频率准确跟踪的系统,称该系统为锁相环路,简称

2008-08-15 12:41:05 333

333 一、实验目的1、掌握模拟锁相环的组成及工作原理。2、学习用集成锁相环构成锁相解调电路。3、学习用集成锁相环构成锁相倍频电路。

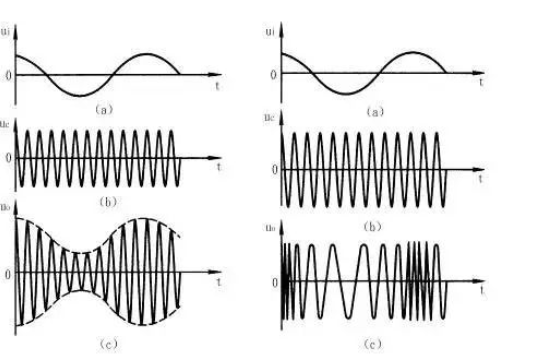

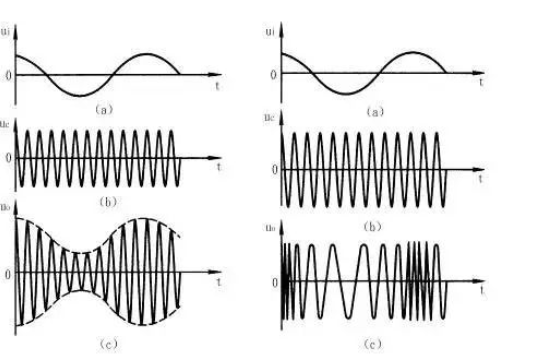

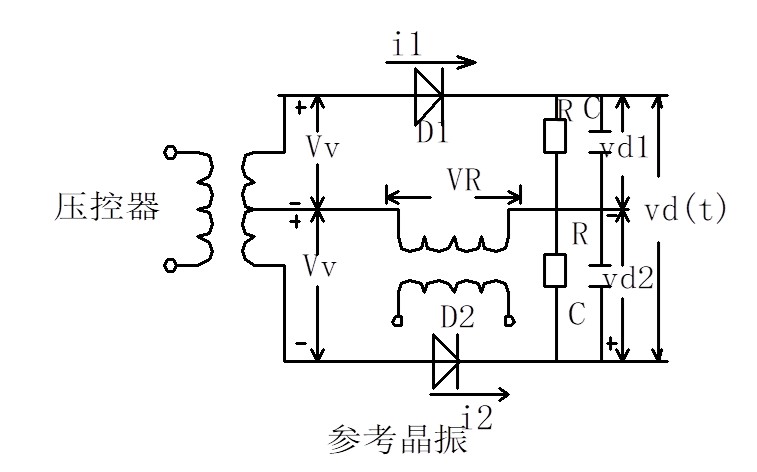

二、锁相环路的基本原理

2009-03-22 11:44:37 127

127 介绍了锁相环路的工作原理以及MM74HC4046AN锁相环芯片的引脚功能。给出了利用锁相环进行频率变换的方案和用方波信号进行频率变换的实际电路,并对环路和相位进行了分析。

2009-04-27 15:42:23 50

50 美国国家半导体公司生产的集成锁相环路解码器LM567以其优良的性能和低廉的价格而在各种解码电路中获得了广泛的应用.本文详细介绍了LM567的内部结构、工作原理、性能指标和选择

2009-04-30 15:22:57 156

156 智能全数字锁相环的设计:在FPGA片内实现全数字锁相环用途极广。本文在集成数字锁相环74297的基础上进行改进,设计了锁相状态检测电路,配合CPU对环路滤波参数进行动态智能配

2009-06-25 23:32:57 72

72 基于FPGA的全数字锁相环设计:

2009-06-26 17:30:59 145

145 介绍了应用VHDL技术设计嵌入式全数字锁相环路的方法。详细叙述了其工作原理和设计思路,并用可编程逻辑器件FPCA予以实现。

2009-07-21 16:46:41 0

0 在载波调制信号的相干解调中,必须提取相干载波,如何从接收信号中提取相干载波,一般方法是采用锁相环路。它能从淹埋在噪声中的微弱信号中提取出相干载波,从而大大提高接

2009-08-03 10:09:06 5

5 本文在介绍了经典全数字锁相环(all digital PLL, ADPLL)的基础上,提出了具有捕获锁定未知输入信号频率功能的ADPLL,使用方便,应用广泛。本文详尽的描述了系统的工作原理和关

2009-08-29 10:07:08 43

43 锁相环频率合成器(Motorola集成电路应用技术丛书):锁相环路设计基础,鉴相器,压控振荡器,程序分频器,前置分频器,单片集成锁相环路等内容。

2009-09-05 08:20:52 0

0 锁相环被广泛应用于电力系统的测量和控制中。介绍了一种新型的基于比例积分控制逻辑的全数字锁相环。通过对其数学模型的分析,阐述了该锁相环的各项性能指标与设计参数的

2010-07-02 16:54:10 30

30 本文在分析商用全数字锁相环的常用技术和低频信号的特点后,提出一种适用于低频信号的基于CPLD的锁相环实现方法。

2010-08-06 14:39:19 118

118 锁相环路的原理及特性

锁相环路的应用

单片集成鉴相器

集成压控振荡器

单片集成锁相环

.................

2010-08-28 15:56:34 99

99 介绍了应用VHDL技术设计嵌入式全数字锁相环路的方法。详细描

2010-09-19 10:09:14 68

68 锁相环原理

锁相环路是一种反馈电路,锁相环的英文全称是Phase-Locked Loop,简称PLL。其作用是使得电路上的时钟和某一外部时钟的相位同步。因锁相环可以

2007-08-21 14:46:04 5484

5484 锁相环路跟踪特性的测量方法:锁相环路的跟踪特性是可以测量的。以CMOS集成锁相环路5G4046构成的跟踪滤波器如图6-2(a)。在电源电压为10V,中心频率fo=1

2008-04-21 11:53:40 1590

1590

摘要: 在FPGA片内实现全数字锁相环用途极广。本文在集成数字锁相环74297的基础上进行改进,设计了锁相状态检测电路,配合CPU对环路滤波参数进行动态智

2009-06-20 12:39:32 1760

1760

基于柔性锁相环路的动态电压恢复器控制方案的研究

摘要:动态电压恢复器(DVR)是一种新型电能质量调节装

2009-07-11 13:46:26 837

837

宽频带数字锁相环的设计及基于FPGA的实现数字锁相环(DPLL)技术在数字通信、无线电电子学等众多领域得到了极为广泛的应用。与传统的模拟电路实现的

2009-11-23 21:00:58 1713

1713

环路滤波器,什么是环路滤波器

环路滤波器

PLL的概念

我们所说的PLL。其实就是锁相环路,简称为锁相环。许多电子设备

2010-03-23 10:58:42 13998

13998 数字锁相环(DPLL),数字锁相环(DPLL)是什么?

背景知识:

随着数字电路技术的发展,数字锁相环在调制解调、频率合成、FM 立体声解码、彩色副

2010-03-23 15:06:21 6110

6110 全数字环路滤波器,什么是全数字环路滤波器

环路滤波器的性能优劣会直接影响到跟踪环路的性能。而采用数字化的环路滤波器便于调试参数和提高

2010-03-23 15:12:15 3869

3869 本文涉及的锁相环路是基于相位控制的时钟恢复系统。目的是用锁相环电路-PLL和DLL实现USB2.0收发器宏单远UTM的时钟恢复木块。其中PLL环路构成的时钟发生器奖外部晶振的12MHZ的正弦信号

2011-03-03 14:58:34 51

51 锁相环路由于具有高稳定性、优越的跟踪性能及良好的抗干扰性,在频率合成中得到了广泛应用。但简单的锁相环路对输出频率、频率分辨率等指标往往不能满足要求,所以要对简单锁相环

2011-05-28 13:42:13 1355

1355

针对扩频通信系统的载波同步,提出一套完善的数字锁相环设计方案. 该方案利用新颖的可控根法完成1~3阶模拟锁相环(APLL)环路参数设计,并实现从模拟域到数字域的转换,得到的数字锁相

2011-08-26 16:10:38 122

122 针对传统的全数字锁相环只能锁定已知信号和锁频范围较小的问题, 提出了一种自动变模控制的宽频带全数字锁相环。对比分析了各类全数字锁相环锁频、锁相的工作机理, 提出了一种新

2011-09-14 15:22:22 79

79 由于锁相环路有上述种种优良的特性,再加上集成锁相环的出现,使锁相环路在电子技术等各个领域获得了广泛的应用,下面对锁相环在不同领域中的应用情况作一简单的概述。 1 在通

2012-09-21 10:09:10 5117

5117 基于FPGA的数字锁相环设计与实现技术论文

2015-10-30 10:38:35 9

9 基于锁相环的滞后超前环路滤波器的设计与仿真,设计方案。技术指标、电路等。

2016-05-24 10:03:05 13

13 Xilinx FPGA工程例子源码:用FPGA实现数字锁相环

2016-06-07 15:07:45 38

38 锁相环路的基本原理和性能分析,有需要的下来看看

2016-08-09 15:45:55 0

0 一种基于bang_bang鉴频鉴相器的全数字锁相环设计_陈原聪

2017-01-07 20:49:27 11

11 PLL(Phase Locked Loop),也称为锁相环路(PLL)或锁相环,它能使受控振荡器的频率和相位均与输入参考信号保持同步,称为相位锁定,简称锁相。

2017-05-22 10:11:40 13190

13190

锁相环路在通信系统中得到了广泛的应用。本文针对超高频RFID读写器的工作特点,设计了基于数字频率合成器LMX2315的锁相环路,给出了锁相环伪随机跳频程序流程图。

2017-09-07 18:54:00 18

18 一、设计目标 基于锁相环的理论,以载波恢复环为依托搭建数字锁相环平台,并在FPGA中实现锁相环的基本功能。 在FPGA中实现锁相环的自动增益控制,锁定检测,锁定时间、失锁时间的统计计算,多普勒频偏

2017-10-16 11:36:45 19

19 1.锁相环的基本组成许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步,利用锁相环路就可以实

2017-11-20 10:33:16 198916

198916

锁相环在通信、雷达、测量和自动化控制等领域应用极为广泛,已经成为各种电子设备中必不可少的基本部件。随着电子技术向数字化方向发展,需要采用数字方式实现信号的锁相处理。因此,对全数字锁相环的研究和应用得

2017-11-24 20:03:04 14190

14190

许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步,利用锁相环路就可以实现这个目的。锁相环路是一种反馈控制电路,简称锁相环(PLL)。锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。

2018-01-22 11:18:45 15350

15350

EngineerIt-锁相环应用中的环路带宽

2019-04-15 06:07:00 13946

13946

锁相环路是一种反馈控制电路,简称锁相环(PLL,Phase-Locked Loop)。锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。

2019-09-20 07:05:00 4322

4322

随着集成电路技术的不断进步,数字化应用逐渐普及,在数字通信、电力系统自动化等方面越来越多地运用了数字锁相环。它的好处在于免去了模拟器件的繁琐,而且成本低、易实现、省资源。本文综合以上考虑,在一片FPGA中以Quartus II为平台用VHDL实现了一个全数字锁相环功能模块,构成了片内锁相环。

2020-07-16 09:16:08 3429

3429

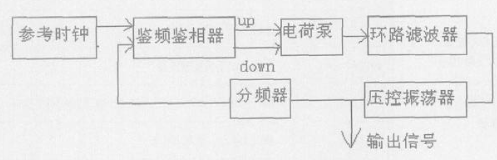

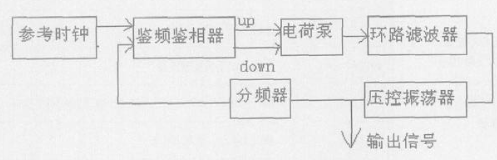

,为了减小压控振荡器控制电压的纹波,它采用了二阶无源环路滤波器,这样就构成了三阶电荷泵锁相环。系统级设计与仿真验证是锁相环设计的第一步和关键的一步。本文对一种用作时钟倍频器的三阶电荷泵锁相环进行了系统级设计与仿真验证,仿真环境采用SIMULINK。

2020-07-24 09:59:51 4277

4277

锁相环路(Phase Lock Loop,PLL)是一种自动相位控制(APC)系统,是现代电子系统中应用广泛的一个基本部件。它的基本作用是在环路中产生一个振荡信号(有时也称本地振荡),这个信号的频率

2020-08-05 14:15:24 7330

7330

锁相环路是一种反馈控制电路,简称锁相环( PLL)。锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。因锁相环可以实现输出信号频率对输入信号频率的自动跟踪, 所以锁相环通常

2020-08-06 17:58:25 26

26 基本锁相环路是由鉴相器、低通滤波器以及压控振荡器构成的相位负反馈系统,具有一个频率输入端口,一个电压输出端口以及一个频率输出端口,通常,模拟模拟锁相环的鉴相器由模拟乘法器承担,压控振荡器由弛张振荡器承担。

2020-12-04 08:00:00 3

3 本文提出了一种适用范围广泛的全数字锁相环(ADPLL)实现方法.在锁相环输入频率未知的情况下,实现锁相锁频功能。本文从全数字锁相环的基本实现方式入手.进行改进,并使用VH DL语言建模,使用FPGA进行验证。

2021-01-26 15:03:00 66

66 本文提出了一种适用范围广泛的全数字锁相环(ADPLL)实现方法.在锁相环输入频率未知的情况下,实现锁相锁频功能。本文从全数字锁相环的基本实现方式入手.进行改进,并使用VH DL语言建模,使用FPGA进行验证。

2021-01-26 15:03:00 20

20 ,具有广泛的应用价值。本文介绍在我国磁悬浮列车车地通信系统中应用的一种CPFSK中频调制器,其核心是基于锁相环路的CPFSK信号调制技术。系统要求中频频率为280 MHz,在信道带宽25 MHz以内,对前

2021-04-05 09:22:00 3708

3708

锁相环路诞生于20世纪30年代。近年来,锁相技术在通信、航天、测量、电视、原子能、电机控制等领域,能够高性能地完成信号的提取、信号的跟踪与同步,模拟和数字通信的调制与解调、频率合成、滤波等功能

2021-03-31 11:59:11 6328

6328

为了提高全数字锁相环的系统运行速度、降低系统功耗,同时提高锁相系统的动态性能与稳态性能,提出一种基于流

2021-04-01 11:53:12 2635

2635

AD805:数据重定时锁相环路过时数据表

2021-05-10 16:12:35 8

8 基于FPGA的宽频带数字锁相环的设计与实现简介说明。

2021-06-01 09:41:14 26

26 基于FPGA的高性能全数字锁相环

2021-06-08 11:09:01 46

46 锁相环路是一种反馈控制电路,简称锁相环(PLL,Phase-Locked Loop)。锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。

2022-03-29 09:54:55 15826

15826 许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步,利用锁相环路就可以实现这个目的。

2022-05-06 15:27:28 3823

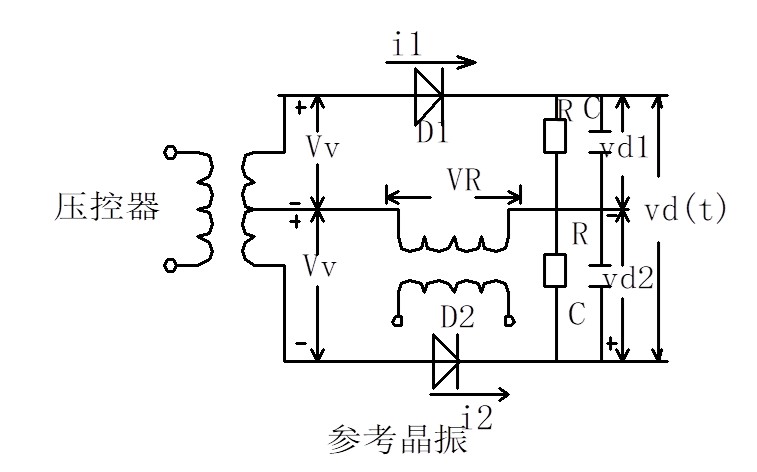

3823 鉴相器是锁相环路的关键部件。在频率合成器中所采用的鉴相器主要有正弦波相位检波器与脉冲取样保持相位比较器两种。

2022-11-11 16:56:47 7791

7791

模拟锁相环和数字锁相环的主要区别在于它们的控制方式不同。模拟锁相环是通过模拟电路来控制频率和相位,而数字锁相环是通过数字信号处理技术来控制频率和相位。此外,模拟锁相环的精度较低,而数字锁相环的精度较高。

2023-02-15 13:47:53 6625

6625 许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步,利用锁相环路就可以实现这个目的。

2023-02-23 10:00:31 3541

3541 许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步,利用锁相环路就可以实现这个目的。

2023-08-19 09:31:50 5872

5872

信号倍频。在本文中,我们将详细探讨锁相环如何实现倍频。 锁相环的基本原理 在介绍锁相环如何实现倍频之前,我们先来回顾一下锁相环的基本原理。锁相环电路主要由三个部分组成:相位检测器(Phase Detector, PD)、环路滤波器(Loop Filter, LF)和振荡器(Voltage Cont

2023-09-02 14:59:37 5114

5114 电子发烧友网站提供《基于VHDL的全数字锁相环的设计.pdf》资料免费下载

2023-11-10 09:47:34 0

0 在现代数字通信中, 数据传输中一个很重要的问题就是同步问题。而同步系统中的核心技 术就是锁相环。锁相环有模拟锁相环、模拟ö数字混合环、全数字锁相环等。前二种环路都要采 用压控振荡器V CO , 利用

2023-11-09 08:31:40 2

2 简介:动态电压恢复器(DVR)是一种新型电能质量调节装置,它能有效抑制电网电压波动对敏感负载的影响。介绍了应用于DVR的一种新型的锁相技术—柔性锁相环路〔softphase locked loop(SPLL)〕和以此为基础的控制方案。

2023-11-09 08:31:40 0

0 简介:锁相环路的工作原理

§1-2 锁相环路的工作原理

锁相环路实质上是一个相差自动调节系统。为了掌握环境的工作原理,理解环 路工作过程中发生的物理现象,必须导出环路的相位

2023-11-09 15:16:24 0

0 锁相环路(Phase Locked Loop)是一个闭环的相位控制系统,它的输出信号的相位能自动跟踪输入信号相

位。

2023-11-09 15:20:46 0

0 在锁相环(PLL)中,低通滤波器通常用于滤除锁相环环路中的高频噪声,并平滑锁相环的控制信号。

2023-12-22 18:15:04 2066

2066 环路的跟踪状态是指锁相环锁定后的状态,即环路中的压控振荡器(VCO)的输出信号的相位能够自动跟踪输入信号的相位,从而保持恒定的稳态相位差。

2024-01-30 14:18:32 2329

2329 基本锁相环通常由锁相检测器(Phase Detector)、低通滤波器(Loop Filter)和令牌圈振荡器(VCO)组成。它是最简单的锁相环形式,用于频率和相位同步。

2024-01-31 16:00:55 3303

3303

锁相环(Phase-LockedLoop, PLL),是一种反馈控制电路,电子设备正常工作,通常需要外部的输入信号与内部的振荡信号同步,利用锁相环路就可以实现这个目的,它可用来从固定的低频信号生成稳定的输出高频信号。

2024-08-06 15:07:20 1844

1844

电子发烧友网站提供《CDC2516锁相环路时钟驱动器数据表.pdf》资料免费下载

2024-08-22 12:27:11 0

0

电子发烧友App

电子发烧友App

评论