8237 可编程DMA控制器 altera提供

2012-08-10 18:09:17

有谁需要ALTERA的ip核,qq57694560,cjfwindy@163.com [此贴子已经被作者于2009-10-14 14:26:18编辑过]

2008-11-16 19:50:33

我用的是CYCLONEIII的芯片,定制DDR2 IP核,之后直接用SINALTAP进行信号抓取,发现无法读写的原因是local_init_done 一直为低,就像XILINX里

2013-04-27 09:46:54

本帖最后由 dybttkl 于 2015-11-1 13:26 编辑

用的cycloneiii 里面的ddr2 ip核。感觉网上的资料很少,仿真的倒很多,但是真正到用户接口那段时序的解释却一个也没有。为何没人写个教程

2015-11-01 13:24:54

模块转换方向(FFT/IFFT)可指定。?易于使用的IP工具台(Toolbench)接口。?Altera支持的VHDL和Verflog HDL仿真器上的IP功能仿真模型。2.特点FFT 2.0.0版具有

2012-08-13 14:34:06

研究了很久,实在弄不出来了,有没有人用过Altera的PCIe IP核???急求!!!谢谢!!!求大神帮忙......

2016-05-26 09:12:33

小弟用的quartus ii软件,调用altera公司的一个乘法器lpm_mult,无结果输出,是不是调用的IP核都要收费呢,有没有办法破解呢????

2015-06-05 11:23:31

以下主题概述了Altera的外部内存接口解决方案。

Altera提供最快、最高效、延迟最低的内存接口IP核。Altera的外部存储器接口IP设计用于方便地与当今更高速的存储器设备接口。

Altera

2023-09-26 07:38:12

语言编写的浮点矩阵相乘处理单元[1],其关键技术是乘累加单元的设计,这样设计的硬件,其性能依赖于设计者的编程水平。此外,FPGA厂商也推出了一定规模的浮点矩阵运算IP核[2],虽然此IP核应用了本厂家的器件,并经过专业调试和硬件实测,性能稳定且优于手写代码,但仍可对其进行改进,以进一步提高运算速度。

2019-08-22 06:41:38

Altera系列FPGA芯片IP核详解

2020-06-28 13:51:01

Altera_IP核,仅供参考

2016-08-24 16:57:15

实现特权同学的例程 特权FPGA VIP视频图像开发套件例程详解2——DDR2控制器读写测试 时,进行IP核配置时,进入下一步配置参数时,变成黑屏重装软件也不行

2018-01-24 08:23:17

IP核生成文件:XilinxAlteraIP 核生成文件:(Xilinx/Altera同) IP 核生成器生成ip 后有两个文件对我们比较有用,假设生成了一个 asyn_fifo 的核,则

2012-08-12 12:21:36

本帖最后由 eehome 于 2013-1-5 09:59 编辑

IP核简介IP核是指:将一些在数字电路中常用但比较复杂的功能块,如FIR滤波器、SDRAM控制器、PCI接口等等设计成可修改

2011-07-06 14:15:52

IP核简介IP核是指:将一些在数字电路中常用但比较复杂的功能块,如FIR滤波器、SDRAM控制器、PCI接口等等设计成可修改参数的模块,让其它用户可以直接调用这些模块,以避免重复劳动。随着CPLD

2011-07-15 14:46:14

实现特权同学的例程 特权FPGA VIP视频图像开发套件例程详解2——DDR2控制器读写测试 时,进行IP核配置时,进入下一步配置参数时,变成黑屏重装了软件也不行,到这个页面还是黑屏,软件版本是13.0

2019-05-17 06:35:42

使用altera的FFTIP核的可变流结构进行FFT时,输出为什么跟实际情况是倍数关系

2016-09-20 19:18:10

最近在使用altera的FIR IP核做半带滤波器,quartus ii软件也破解了,firIP核也破解了,modelsin仿真也通过了,但是下载不了.sof文件到开发板,大家有用FIR IP核成功实现下板的经验吗,求大神指点呀。谢谢!

2018-05-11 16:01:15

altera公司IP核使用手册

2012-08-15 13:11:24

altera公司IP核使用手册,分享给想学习altera公司FPGA的IP核使用的亲们~~

2013-02-16 22:40:19

问题:采用altera公司的ep4ce6e22c8控制器的一对差分引脚实现差分输入输出配置功能尝试方法:尝试配置LVDS IP核,但发现只有单独的输入输出,如图

2019-10-20 22:13:05

机制对当前变长分组骨干网的流量控制还是具有重要的参考价值,所以有必要对ATM的流量控制及其实现方式进行深入的研究。 IP核是一段具有特定电路功能的硬件描述语言代码,该程序与集成电路工艺无关,因而

2011-09-27 11:54:25

CAN控制器IP核(可直接在Nios II中使用)

2016-08-24 16:54:21

为任意或所有DDR3 SDRAM器件提供单独的终端阻抗控制,提高了存储器通道的信号完整性。图2:DDR3存储器控制器IP核框图DDR3存储器控制器应支持广泛的存储器速率和配置,以满足各种应用需求。例如

2019-05-24 05:00:34

在quartus2中创建了一个DDR2 控制器的ip核 ,但是在选择 DDR型号的时候,找不到我要用的DDR芯片信号 怎么办?选择了一个DDR芯片将它的行列bits数改了之后 发现 内存大小又不对 。求解答

2017-09-19 14:50:23

EVL6562A-35WFLB,评估板使用L6562A 35W宽范围高功率因数反激式转换器。它描述了基于过渡模式PFC控制器L6562A的产品评估板,并展示了其台架演示的结果。该板是35 W,宽范围

2019-10-11 08:40:07

的SOPC系统中设计了LCD显示驱动IP核,并下载到Cyclone系列的FPGA中,实现了对LCD的显示驱动。

2019-08-06 08:29:14

Rockchip I2C控制器支持哪些功能?

2022-03-02 09:56:27

(Intellectual Property Core)。本文介绍USB 2.0设备控制器IP中的AHB接口部分设计。1设计概述1.1协议概述 设计前首先需要了解USB和AHB数据传输的特点

2019-05-13 07:00:04

大家好,有没有谁比较熟悉ALTERA公司的VIP系列ip核,我们用该系列IP核中的某些模块(主要是scaler和interlacer)来实现高清图像转标清图像(具体就是1080p50转576i30

2015-04-13 14:12:18

你好任何人都可以指导我,Xilinx ISE中的DDR控制器是否有任何IP实现。如果没有如何实现DDR控制器以上来自于谷歌翻译以下为原文Hi can any one guide me

2019-02-27 12:13:51

大家好,应用altera Cyclone V外接DDR3,启用HMC实现硬核控制,IP核在设计生成时出现如下错误:Error: Error during execution of script

2018-04-25 10:28:52

请教各位大神,小弟刚学FPGA,现在在用spartan-3E的板子,想用上面的DDR SDRAM进行简单的读写,用MIG生成DDR核之后出现了很多引脚,看了一些资料也不是很清楚,不知道怎么使用生成的这个IP核控制器来进行读写,希望大神们稍作指点

2013-06-20 20:43:56

modelsim 仿真 altera IP核(ROM,RAM实例)急求大神们ROM和RAM 的综合仿真代码

2015-11-19 21:02:57

2.5MHz 振幅0-5V 的正弦信号,请问 data 端口应该输入怎样的信号?如果有Altera IP核相关的详解资料推荐下更好。多谢了。

2014-10-28 12:34:41

本文和设计代码由FPGA爱好者小梅哥编写,未经作者许可,本文仅允许网络论坛复制转载,且转载时请标明原作者。Altera DDR2控制器使用IP的方式实现,一般很少自己写控制器代码。ddr22

2020-02-25 18:33:00

本文介绍一款USB OTG IP核的设计与实现,该设备控制器可作为IP核用于SoC系统中,完成与主机控制器的通信,并能与普通的USB从设备进行通信。

2021-04-29 06:47:00

在较大工程中由于其局限性使用的越来越少,不推荐再学习;Verilog HDL为当今主流的设计方式;用IP核代替用户自己设计的逻辑,可以大大缩短开发周期,提供更加有效的逻辑综合和实现。Altera IP

2019-03-04 06:35:13

的DDR2控制器IP核模块进行读写操作。每1.78秒执行一次DDR2的写入和读出操作。先是从0地址开始遍历写256*64bits数据到DDR2的地址0-1023中;在执行完写入后,执行一次相同地址的读

2016-10-08 17:05:55

`例说FPGA连载41:DDR控制器集成与读写测试之DDR2 IP核接口描述特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1c0nf6Qc 如图

2016-10-27 16:36:58

用 quartus 生成一个ddr2的ip核,选择了生成仿真模型,但生成不了,文件目录下没有example.v,只有一个对应 的sdc文件 。 另外生成报告里还有 一个warning ,,求指导

2017-09-07 11:48:09

想问下 怎样 用 Altera DE2C35F672C6 进行视频图像采集。一个摄像头采集,一个液晶显示采集的图像?谢谢各位啊 新手不会,希望能附上工程{:4:}

2012-04-27 21:57:13

Altera系列FPGA芯片IP核详解

2016-08-19 17:24:48

`勇敢的芯伴你玩转Altera FPGA连载63:PLL IP核创建于配置特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1i5LMUUD 可以复制上一个

2018-04-20 21:45:06

;nbsp;IP碎片;FPGA;RLDRAM控制器;最大传输单元;Abstract:In order to secure the&

2008-10-07 11:01:03

工具,经面向硬件电路的仿真验证,本文的方法可实现OC-48接口(2.5Gb/s)上线速分组的IP碎片重组,并具有硬件开销小,可扩展性好的特点。关键词: IP碎片;FPGA;RLDRAM控制器;最大传输

2008-10-07 11:00:19

PCI接口控制器兆核函数(即接口IP)及相关测试平台,通过选择合适的芯片速度,可以满足运行在33MHz或66MHzPCI时钟下的时序要求,支持Altera的Stratix II、Stratix

2018-12-04 10:35:21

引言随着半导体技术的发展,深亚微米工艺加工技术允许开发上百万门级的单芯片,已能够将系统级设计集成到单个芯片中即实现片上系统SoC。IP核的复用是SoC设计的关键,但困难在于缺乏IP核与系统的接口标准

2019-06-11 05:00:07

Viterbi译码的基本过程,接着根据Viterbi译码器IP核的特点,分别详细介绍了并行结构、混合结构和基于混合结构的增信删余3种Viterbi译码器IP核的主要性能和使用方法,并通过应用实例给出了译码器IP

2010-04-26 16:08:39

此提供了新的解决方案。IP核(IP Core)是具有特定电路功能的硬件描述语言程序,可较方便地进行修改和定制,以提高设计效率[3]。本文研究了基于FPGA的数据采集控制器IP 核的设计方案和实现方法,该IP核既可以应用在独立IC芯片上,还可作为合成系统的子模块直接调用,实现IP核的复用。

2019-07-09 07:23:09

的CycloneIIEP2C35芯片上集成了NiosII软核,相关的外围控制器和自定义的电机控制模块,完成了该设计的验证工作。1基本原理步进电机是一种把电脉冲信号变换成直线位移或角位移的执行元件。步进

2019-05-31 05:00:07

性,因此本文选择了PCI总线。33MHz、32位的PCI总线的数据传输速率最高可达133MBps, 完全可以满足高速实时传输的需求。选择了Altera公司的PCI编译器软件包来实现PCI接口控制

2018-12-07 10:34:34

任务需求来定制显示控制功能,可以增强系统可靠性和设计灵活性,降低了成本。目前针对LCD 显示屏设计的控制器IP 核文章较多[1-2],但对于TFT-LCD 触控屏设计的控制器IP 核文章较少[3],而且

2018-11-07 15:59:27

,LCD液晶显示器凭借功耗低、体积小、轻薄及控制驱动简单等特点,在智能仪器、仪表和低功耗电子产品中得到了广泛应用。以深圳秋田视佳实业有限公司的液晶显示模块CBGl28064为例,告诉大家, 如何在SOPC的NiosII中设计LCD显示驱动IP核?实现了对LCD的显示驱动。

2019-08-05 07:56:59

,以及对应的波形图和 Verilog HDL 实现。我们调取的 DDR3 SDRAM 控制器给用户端预留了接口,我们可以通过这些预留的接口总线实现对该 IP 核的控制,本章节将会讲解如何根据

2022-02-08 07:08:01

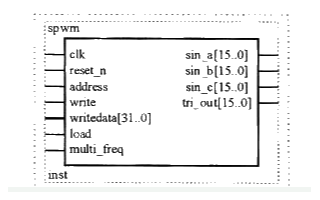

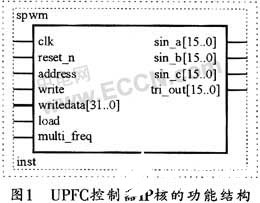

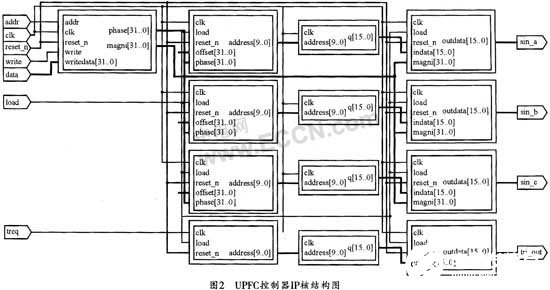

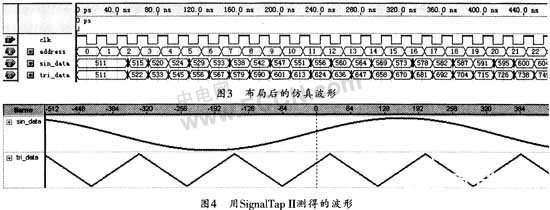

本文利用Altera公司的Quartus开发工具设计了一个基于Avalon总线接口的UPFC控制器IP核,以便于和NiosII组成一个完整的控制系统。

2021-04-08 06:25:12

我想通过JTAG在我的设计中内部访问寄存器。1)如何挂钩fpga JTAG链?2)是否有JTAG控制器IP?我看了,没看到一个。谢谢,弗雷德

2020-05-29 06:13:24

本文介绍的是基于RISC体系结构的8位高速MCUIP软核的设计与实现,采用Verilog HDL自上而下地描述了MCUIP软核的硬件结构,并验证了设计的可行性和正确性。在实际硬件电路中,该IP核的运行频率达到75MHz,可应用于高速控制领域。

2021-04-19 07:28:21

请问谁手里还有原来ip-extreme免费版本的coldfire for altera软核,能否分享给我一份?

2021-06-21 06:25:01

1、建立工程,2、调用DDR2 ip核。3、设置参数,选择如上图。其余保持默认。生成IP4、选择ddr2_phy_ddr_timing.sdc、ddr2

2014-11-01 20:50:15

本人想使用altera的以太网IP核tse核,发现Quartus里面并没有告诉怎样控制这个核。请问大家是怎样控制这个IP核的呢?完全用Verilog代码编写控制程序,好像很复杂呀,难道只能通过NiosII软核吗

2015-01-22 14:55:31

很多FPGA工程师陶醉于用硬件描述语言搞定庞大的逻辑难题,面对复杂的TCP/IP 协议时却素手无策,怎么办? 方案1、用ALTERA的NIOS II+免费的以太网第三方软核,搞定!速度达到

2014-12-16 16:11:47

pc和一款控制器通过网线连接,arp-a命令查询不到局域网内有控制器的ip,请问有没有什么方法可以查询到控制器的ip地址?

2021-06-18 10:53:37

数学运算(乘法器、除法器、浮点运算器等)、信号处理(FFT、DFT、DDS等)。IP核类似编程中的函数库(例如C语言中的printf()函数),可以直接调用,非常方便,大大加快了开发速度。使用Verilog调用IP

2018-05-16 11:42:55

请问Altera RAM IP核怎么使用?

2022-01-18 06:59:33

本文介绍的在电能质量监测系统中信号采集模块控制器的 IP核,是采用硬件描述语言来实现的。

2021-04-08 06:33:16

如题,调用altera公司的FFT IP核,用的是13.1版本,将modulsim仿真的结果输入到matlab画出频谱图,功能仿真结果没有问题,但门级仿真中除了原频率信息外,出现了很多不存在的频率

2018-08-28 20:43:56

系统级设计,设计人员现在使用SOPC Builder工具时,可以选择Freescale?、ARM?或者Altera软核处理器以及50多种其他的知识产权(IP)模块。 &

2008-06-17 11:40:12

IP核的Verilog程序进行综合时,可选用Altera公司的CycloneIIEP2C35评估板。该板有33216个逻辑单元,105个M4k存储模块,35个18×18乘法单元,4个PLL和475个I

2019-06-03 05:00:05

,我国也迫切需要发展自己的IP核。本文针对I2C的主方式串行扩展通信的特点,详细给出设计过程和结果。1 IP核简介 IP核是指:将一些在数字电路中常用但比较复杂的功能块,如FIR滤波器、SDRAM

2019-04-12 07:00:09

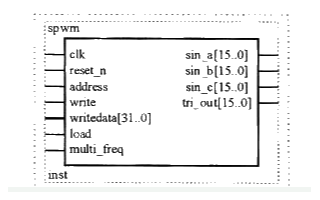

统一潮流控制器渊UPFC冤是柔性交流输电系统渊FACTS冤的一种,其核心是控制系统设计遥文中根据正弦脉宽调制原理,并针对软件和硬件实现正弦调制波形所存在的不同缺点,提

2009-03-07 10:07:08 15

15 本文介绍一款USB 设备控制器IP CORE 的设计与实现。论文首先介绍了USB 设备控制器的设计原理,模块划分及每个模块的功能。然后介绍了该IP CORE 在ModelsimSE 中的功能仿真及FPGA 验证结

2009-08-06 11:39:00 8

8 本文以改善UPFC 动态性能为出发点,指出了UPFC 研究中存在的问题:1 目前针对UPFC 系统所建立的模型不完整,使得控制系统设计中存在缺陷;2 没有一个有效、合理的潮流调节器参数

2010-02-22 10:00:31 19

19 针对给定的UPFC 的控制目标,提出了一种在全论域范围内带有自调整因子的变间距模糊 交互控制 策略,并将其应用于UPFC 的控制系统设计中,减少了多个调整因子寻优的复杂性,克服了

2011-08-11 16:51:16 26

26 本设计基于FPGA的彩色触摸屏控制器能够实现颜色深度为24 bit,分辨率为480×272的TFT-LCD控制和ADS7843芯片的时序控制,为后续IP核的编写工作打下了基础。

2013-01-07 11:08:20 2731

2731

统一潮流控制器(Unified Power Flow Con-troller,简称UPFC)是一种可以较大范围地控制电流使之按指定路经流动的设备,它可在保证输电线输送容量接近热稳定极限的同时又不

2020-03-19 10:00:47 1290

1290

本文的目的是使用基于智能控制器的 UPFC 设备提高电力系统的稳定性和可靠性。 UPFC 设备在各种故障条件下由模糊逻辑控制器控制。 模糊逻辑控制器将电压、相角等电力系统参数与参考值进行比较,产生

2021-11-29 16:04:59 0

0

![]()

电子发烧友App

电子发烧友App

评论