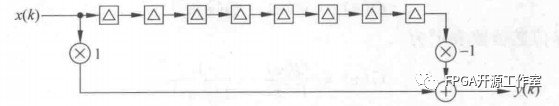

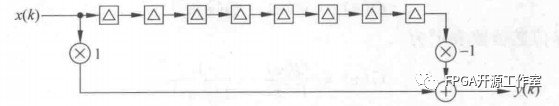

sample rate convert 和 down sample rate convert 的FPGA实现打下基础。 1 梳状滤波器 图1 梳状滤波器结构 梳状滤波器的两端为1和-1的权值,具有简单

2020-11-21 09:57:00 5220

5220

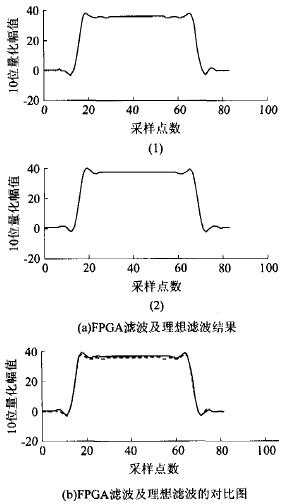

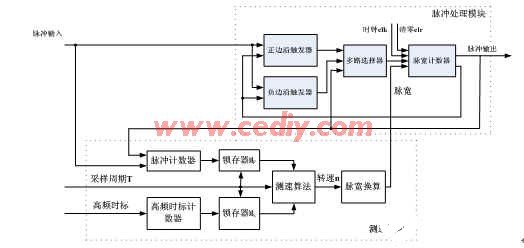

fpga实现滤波器fpga实现滤波器在利用FPGA实现数字信号处理方面,分布式算法发挥着关键作用,与传统的乘加结构相比,具有并行处理的高效性特点。本文研究了一种16阶FIR滤波器的FPGA设计方法

2012-08-12 11:50:16

。本文研究了一种16阶FIR滤波器的FPGA设计方法,采用Verilog HDI语言描述设计文件,在Xilinx ISE 7.1i及ModelSim SE 6.1b平台上进行了实验仿真及时序分析,并探讨了实际工程中硬件资源利用率及运算速度等问题。

2012-08-11 18:27:41

实现FPGA数字下变频的多类滤波器分组级联技术分析1 引 言 本文针对以下高效算法做了总结,进行合理的分组级联并引入流水线技术以便于在FPGA上实现。数字下变频(DDC)就是通过混频、抽取和滤波等

2009-10-23 10:26:53

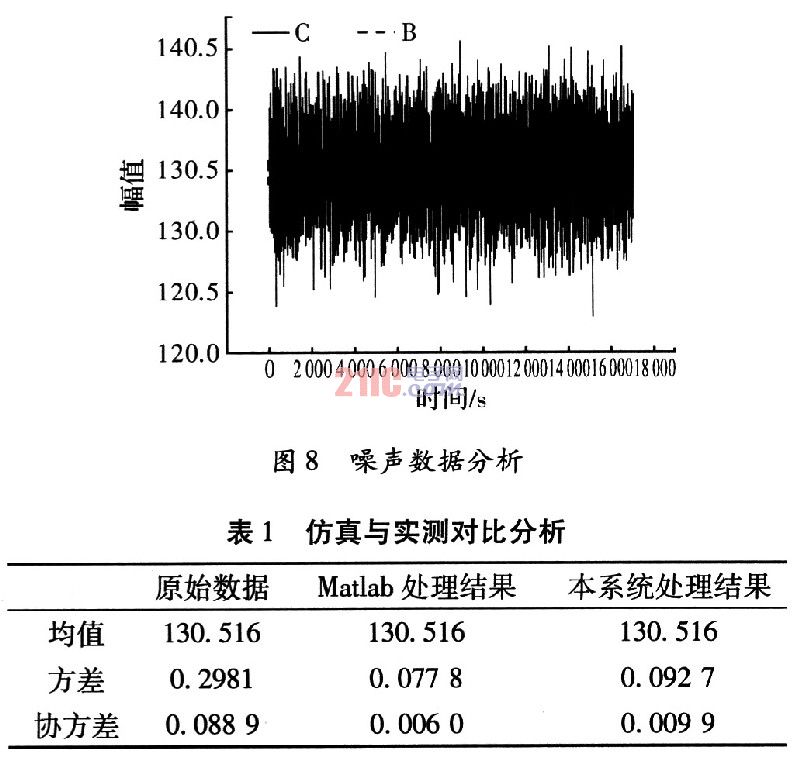

诊断仪对超声信号进行动态滤波。动态滤波包含模拟动态滤波和数字动态滤波。模拟动态滤波器要改变器件的参数,从而达到改变通频带中心频率的效果,方法简易,效果很好。同时,控制信号是来自FPGA输送出的数字信号,经D/A转换所得,采用FPGA实现控制信号,实现了很高的精度,达到了预想的效果。

2019-10-17 07:34:05

字技术迅速发展以后,相关滤波也经常利用A/D板对信号采样后,在计算机中实现,成为数字滤波的一种形式。本文设计了一种实现相关滤波的方法,这是相关分析在测试技术中的一个典型应用。图1所示为相关滤波器的典型框图

2019-05-06 09:26:39

CIC抽取滤波器MATLAB仿真和FPGA实现(1)设计理想滤波器目标:1、滤波器在有效频段内纹波满足设计要求。2、抽取或内插处理后在有效频段内不产生混叠。3、滤波器实现简单,需要资源较少。这个

2021-08-17 08:27:40

FIR滤波器的实现方法有哪几种?基于Verilog HDL的FIR数字滤波器设计与仿真

2021-04-09 06:02:50

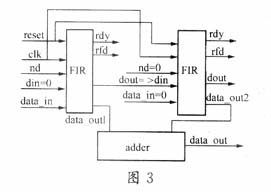

FIR滤波器工程说明本案例设计了一个15阶的低通线性相位FIR滤波器,采用布莱克曼窗函数设计,截止频率为500HZ,采样频率为2000HZ;实现全串行结构的滤波器;采用具有白噪声特性的输入信号,以及

2017-08-02 17:35:24

本帖最后由 eehome 于 2013-1-5 10:01 编辑

IIR数字滤波器的Matlab和FPGA实现

2012-08-20 22:16:49

使用iir滤波器相对fir滤波器可以在使用更小的阶数的情况下实现更好的效果。实验证明,可能20阶的iir效果堪比500阶左右的fir滤波器效果。首先放出iir的matlab仿真代码:%本程

2021-12-22 08:29:40

最近在做一个FPGA的课程设计,遇到一个比较烦人的问题,希望大神们可以指点迷律。一个16阶的FIR滤波器,采用分布式算法实现的,采样率1M,fc=100K,频率到了30K以上时就会出现那些尖刺,很

2018-02-25 19:25:50

Filter Design&Analysis Tool求得,下面以一个IIR三阶低通滤波器为例,介绍C语言IIR滤波器的实现方法:1、计算滤波器的系数根据信号的采

2021-07-14 08:26:21

主要任务:1.熟悉低通滤波器的原理及应用2.熟悉FPGA的硬件描述3.FPGA如何实现小数分频器4.用MATLAB对低通滤波器的验证预期成果或目标:FPGA对低通滤波器的Verilog(或VHDL

2013-04-04 22:16:11

以单片机和可编程逻辑器件(FPGA)为控制核心,设计了一个程控滤波器,实现了小信号程控放大、程控调整滤波器截止频率和幅频特性测试的功能。其中放大模块由可变增益放大器AD603实现,最大增益60dB

2019-09-29 14:08:52

诊断仪对超声信号进行动态滤波。动态滤波包含模拟动态滤波和数字动态滤波。模拟动态滤波器要改变器件的参数,从而达到改变通频带中心频率的效果,方法简易,效果很好。同时,控制信号是来自FPGA输送出的数字信号

2019-07-23 06:11:34

设计一般采用CIC、HB、FIR级联的形式组成。同时,由于CIC滤波器的通带性能实在太差,所以中间还要加上一级PFIR滤波器以平滑滤波器的通带性能。

2019-09-20 06:13:11

本帖最后由 eehome 于 2013-1-5 09:50 编辑

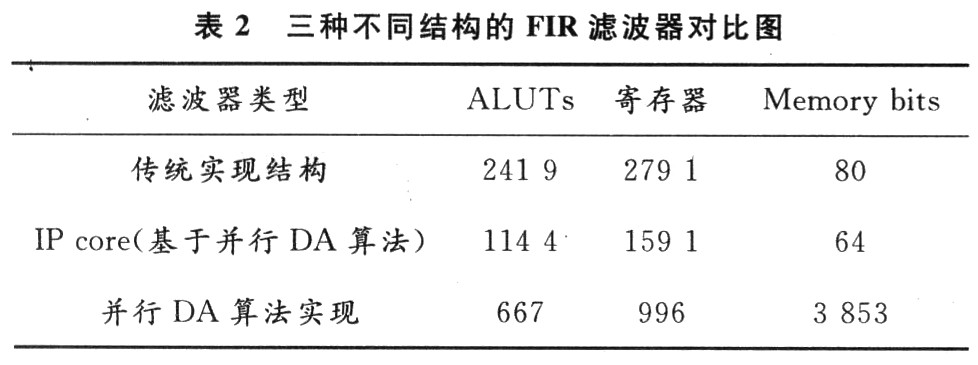

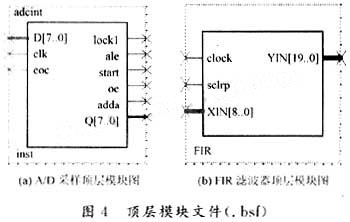

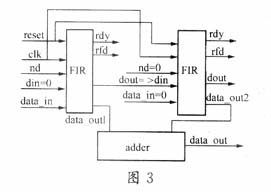

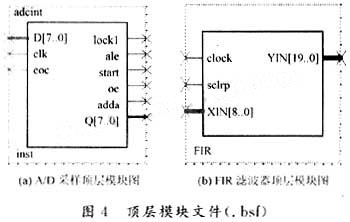

基于FPGA的FIR滤波器设计与实现 文章研究基于FPGA、采用分布式算法实现FIR滤波器的原理和方法,用

2012-08-11 15:32:34

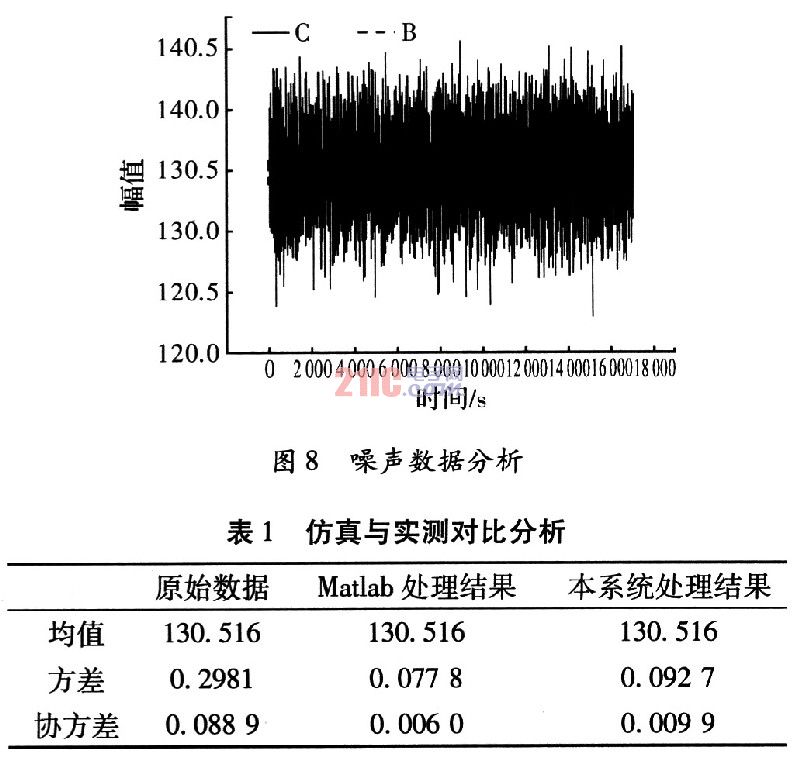

数字滤波器、DSP器件或可编程逻辑器件(如FPGA)实现。因为,用FPGA实现数字滤波器具有实时性强、灵活性高、处理速度快以及小批量生产成本低等优点,所以得到了较为广泛的应用。本文以巴特沃思数字

2019-07-08 07:18:25

基于FPGA的fir滤波器实现

2017-08-28 19:57:36

本帖最后由 eehome 于 2013-1-5 09:50 编辑

基于fpga的fir滤波器的实现

2012-08-17 16:42:33

【作者】:袁江南;汤碧玉;陈辉煌;【来源】:《厦门大学学报(自然科学版)》2010年02期【摘要】:给出了一种自适应滤波器的设计和FPGA的实现方法.简要分析了最小均方误差(LMS)、归一化最小均方

2010-04-24 09:01:12

脉冲响应(ⅡR)滤波器和有限长单位脉冲响应(FIR)滤波器两种,其中,FIR滤波器能提供理想的线性相位响应,在整个频带上获得常数群时延从而得到零失真输出信号,同时它可以采用十分简单的算法实现,这两个

2019-08-30 07:18:39

【作者】:丁稳房;郑利枝;黄文聪;张党文;【来源】:《湖北工业大学学报》2010年01期【摘要】:根据有源电力滤波器的基本原理,介绍了硬件电路和控制方法.控制器件采用DSP TMS320F2812.

2010-04-24 09:06:54

的逻辑、需要较少的计算资源、更低的功耗,并减少了可能的饱和/溢出。可用如今新型的小规模、中档的FPGA,如LatticeECP3 来实现这些滤波器。

2019-07-08 08:01:03

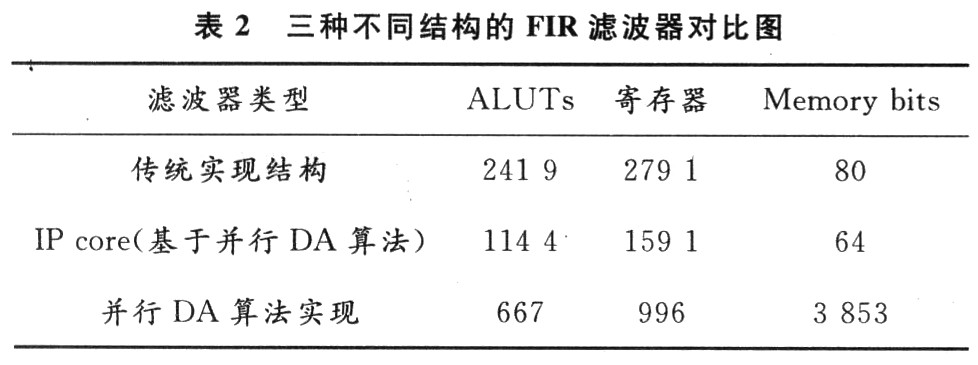

传统数字滤波器硬件的实现主要采用专用集成电路(ASIC)和数字信号处理器(DSP)来实现。FPGA内部的功能块中采用了SRAM的查找表(lo-ok up table,LUT)结构,这种结构特别适用于并行处理结构,相对于传统方法来说,其并行度和扩展性都很好,它逐渐成为构造可编程高性能算法结构的新选择。

2019-10-22 07:14:04

滤波器是任何信号处理系统的关键组成部分,随着现代应用的日趋复杂,滤波器设计的复杂程度也日益提高。采用 FPGA 设计和实现的高性能滤波器的能力是模拟方法所望尘莫及的。另外,采用FPGA

2019-09-18 08:28:47

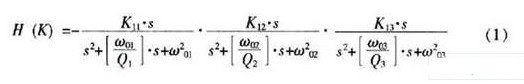

本文介绍了一种采用级联结构在FPGA上实现IIR数字滤波器的方法。

2021-04-15 06:16:32

本文提出一种基于Stratix系列FPGA器件的新的实时高速脉动FIR滤波器的快速实现方法。

2021-05-06 09:50:42

滤波器在FPGA中的实现用FPGA来实现滤波器的设计优点用FPGA来设计滤波器,不但设计简单,而且成本小,可靠性好。且无需像传统的设计芯片一样进行测试。主要优点:设计简洁。若设计有误,则只需

2021-07-30 07:03:10

使用了较少的逻辑、需要较少的计算资源、更低的功耗,并减少了可能的饱和/溢出。可怎么办,才能用中档FPGA实现多相滤波器?

2019-08-06 07:12:39

如何用中档FPGA实现多相滤波器?

2021-04-29 06:30:57

使用了较少的逻辑、需要较少的计算资源、更低的功耗,并减少了可能的饱和/溢出。可用如今新型的小规模、中档的FPGA,如LatticeECP3 来实现这些滤波器。

2019-10-22 06:55:44

最近想从嵌入式平台上用C语言实现二阶滤波器,于是先从Matlab上验证二阶滤波器公式,再编写C语言来验证。算法移植(实现过程)①先用Matlab自带公式的二阶滤波器实现;②运用公式Matlab实现

2021-12-15 09:12:52

设计FIR的方法。数字滤波器数字滤波器从实现结构上划分,有FIR和IIR两种。FIR的特点是:线性相位、消耗资源多;IIR的特点是:非线性相位、消耗资源少。由于FIR系统的线性相位特点,设计中绝大多数情况

2020-09-25 17:44:38

并行流水结构FIR的原理是什么基于并行流水线结构的可重配FIR滤波器的FPGA实现

2021-04-29 06:30:54

目前FIR滤波器的硬件实现的方式有哪几种?怎么在FPGA上实现FIR滤波器的设计?

2021-05-07 06:03:13

本文以实现抽取率为2的具有线性相位的3阶FIR抽取滤波器为例,介绍了一种用XC2V1000型FPGA实现FIR抽取滤波器的设计方法。

2021-05-07 06:02:47

本文将简单介绍另一种数字滤波器——IIR滤波器的原理,详细介绍使用Verilog HDL设计直接型IIR滤波器的方法。数字滤波器数字滤波器从实现结构上划分,有FIR和IIR两种。FIR的特点是:线性

2020-09-27 09:22:58

分布式的滤波器算法是什么?一种基于FPGA分布式算法的滤波器设计实现

2021-04-29 07:13:23

用FPGA来实现滤波器的设计优点有哪些?

2021-11-05 07:59:53

利用matlab设计一个线性相位FIR带通滤波器,并在FPGA上实现。要求:1、滤波器指标:过渡带带宽分别为100~300HZ,500~700HZ,阻带允许误差为0.02,通带允许误差为0.01,采样

2015-06-16 19:25:35

的方式实现乘法运算 采用级联方式实现FPGA的过程要注意的是每级滤波器的输出位数,保证每级滤波器的输出数据没有溢出,其他地方都跟直接型类似至于采用流水线结构实现级联结构,就是在每级滤波器的输出部分加一个

2015-07-26 21:44:21

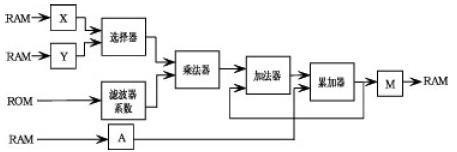

本文提出了一种采用现场可编程门阵列器件 FPGA 实现FIR 字滤波器硬件电路的方案,该方案基于只读存储器ROM 查找表的分布式算法。并以一个十六阶低通FIR 数字滤波电路在ALTERA 公

2009-08-31 16:47:47 44

44 本文介绍了自适应滤波器的实现方法,给出了基于LMS 算法自适应滤波器在FPGA 中的实现,简单介绍了这种实现方法的各个功能模块,主要包括输入信号的延时输出模块、控制模块

2009-09-14 15:51:00 34

34 本文利用Xilinx公司Virtex系列器件的特殊结构,提出了一种比较新颖的数字匹配滤波器设计方法,它在保证了该匹配滤波器与传统匹配滤波器性能

2009-09-15 09:07:29 22

22 基于FPGA对称型FIR滤波器的设计与实现:在基于FPGA的对称型FIR数字滤波器设计中,为了提高速度和运行效率,提出了使用线性I相位结构和加法树乘法器的方法,并利用Altera公I司的FPG

2009-09-25 15:38:38 30

30 本文详细讨论了利用新版本FPGA 辅助设计软件QuartusII6.0 中提供的浮点运算功能模块实现IIR 滤波器的方法,与采用FPGA 的乘法模块的同类设计相比,此滤波器设计结构简单,容易扩

2009-12-19 15:44:27 38

38 在软件无线电的下变频模块中,级联梳状积分滤波器有着重要的应用,其主要作用是信号的抽取与低通滤波。文中总结了级联梳状积分抽取滤波器的理论要点,并介绍了采用FPGA

2010-01-06 15:16:45 31

31 数字滤波器在FPGA中的实现

2010-02-09 10:21:27 76

76 设计一个由现场可编程门阵列(FPGA)控制的滤波器。该滤波器主要由3个模块组成:前置放大、滤波电路、FPGA显示与控制电路等利用FPGA作为放大器及程控滤波器电路中继电器组的控制模

2010-07-17 18:00:09 45

45 IIR数字滤波器设计-在FPGA上实现任意阶IIR数字滤波器

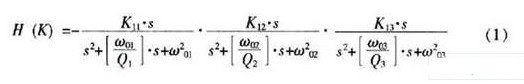

摘 要:本文介绍了一种采用级联结构在FPGA上实现任意阶IIR数字滤波器的方法。此

2008-01-16 09:45:39 2276

2276

高效FIR滤波器的设计与仿真-基于FPGA

摘要:该文在介绍有限冲激响应(FIR)数字滤波器理论及常见实现方法的基础上,提出了一种基于FPGA的高效实现方案。

2008-01-16 09:56:02 1456

1456

如何用用FPGA实现FIR滤波器

你接到要求用FPGA实现FIR滤波器的任务时,也许会想起在学校里所学的FIR基础知识,但是下一步该做什么呢?哪些参数是重

2009-03-30 12:25:45 4503

4503

【摘 要】 提出了一种基于分布式算法的,采用基于RAM之移位寄存器来设计可级联FIR滤波器的设计方法。 &

2009-05-11 19:45:52 983

983

摘要: 提出了一种采用现场可编码门阵列器件(FPGA)并利用窗函数法实现线性FIR数字滤波器的设计方案,并以一个十六阶低通FIR数字滤波器电路的实现

2009-06-20 14:05:46 1057

1057

摘要: 针对在FPGA中实现FIR滤波器的关键--乘法运算的高效实现进行了研究,给了了将乘法化为查表的DA算法,并采用这一算法设计了FIR滤波器。通过FPGA仿零点验证

2009-06-20 14:09:36 677

677

FIR带通滤波器的FPGA实现

引 言 在FPGA应用中,比较广泛而基础的就是数字滤波器。根据其单位冲激响应函数的时域特性可分为无限冲击响应(Infinite

2009-11-13 09:55:18 6564

6564

基于多速率DA的根升余弦滤波器的FPGA实现

0 引 言 根升余弦成形滤波器是数字信号处理中的重要部件,它能对数字信号进行成形滤波,压缩旁瓣,减少

2009-11-13 09:59:54 1518

1518

基于FPGA的数字滤波器的设计与实现

在信息信号处理过程中,如对信号的过滤、检测、预测等,都要使用到滤波器,数字滤波器是数字信号处理中使用最广泛的一

2010-01-07 10:45:35 3475

3475

FPGA的Kalman滤波器的设计

摘要:针对电路设计中经常碰到数据的噪声干扰现象,提出了一种Kalman滤波的FPGA实现方法。该方法采用了TI公司的高精度模数转换

2010-04-13 13:32:46 2566

2566

摘要: 针对水下目标跟踪定位系统中信号的特点, 采用自适应Notch 滤波器对接收信号进行检测, 使系统在低信噪 比的情况下仍能保证较高的正确检测率。提出了用FPGA 实现Notch 滤波器的硬件电路方案, 用DDS 技术解决了 Notch 滤波器的正交参考源的输入问题, 简化

2011-02-17 16:00:14 69

69 目前数字滤波器的硬件实现方法通常采用专用DSP芯片或FPGA,本文从FIR滤波器的系数考虑,采用CSD编码,对FIR数字滤波器进行优化设计。

2011-08-16 10:54:41 3632

3632

针对罗兰C前端 带通滤波 的需求,提出了采用级联形式在FPGA上实现罗兰C数字带通滤波器的方法。首先利用Matlab设计出满足要求的滤波器,考虑硬件设计要求将参数进行取整,并对取整

2011-08-30 16:24:25 45

45 文中设计的均衡滤波器充分利用FPGA内部资源、时间换取空间的方法,在EP1C3系列的FPGA内实现1 024阶FIR数字均衡滤波器,并通过重载系数,可实现多种频率响应的均衡特性、简易数字均衡滤波

2011-10-19 15:23:48 38

38 基于FPGA的FIR滤波器设计与实现,下来看看

2016-05-10 11:49:02 38

38 研究了一种采用FPGA实现32阶FIR滤波器硬件电路方案;讨论了窗函数的选择、滤波器的结构以及系数量化问题;研究了FIR滤波器的FPGA实现,各模块的设计以及如何优化硬件资源,提高运行

2017-11-10 16:41:57 15

15 为了减少信道化接收机的资源消耗,对低通滤波器组实现信道化接收机的结构进行了研究。在前人将HB滤波器和FIR滤波器设计为多通道并采用时分复用方法的基础上,将NCO和CIC滤波器也做了同样处理,并在

2017-11-17 05:38:02 3382

3382

ISE 12.3在Xilinx xc5vsx95t-2ff1136 FPGA上实现了一种下采样率为64的抽取滤波器。Modelsim仿真结果表明,该抽取滤波器设计是有效的,达到了设计指标。

2017-11-17 09:01:55 5303

5303 本文针对快速、准确选择参数符合项目要求的滤波器设计方法的目的,通过系统的介绍有限脉冲响应( Finite Impulse Response,FIR)滤波器的原理、结构形式以及几种FIR滤波器设计方法

2017-12-21 14:53:14 14

14 ,常规做法是利用插值和抽取的方法实现数字信号的变采样处理,这种方法实现复杂,硬件成本高。文中提出了一种高速并行成型滤波器的FPGA实现方法,这种基于群延时结构的查找表算法,所需的查找表只需存储单位冲击响应的采样值,

2018-02-23 10:14:22 0

0 用FPGA实现抽取滤波器比较复杂,主要是因为在FPGA中缺乏实现乘法运算的有效结构,现在,FPGA中集成了硬件乘法器,使FPGA在数字信号处理方面有了长足的进步。本文介绍了一种采用Xilinx公司的XC2V1000实现FIR抽取滤波器的设计方法。

2018-04-28 11:50:00 1073

1073

基于灵活自适应的空口波形技术FOFDM(Filtered OFDM)是现代通信技术的研究热点,设计并实现可调FIR滤波器是实现该技术的核心工作之一。本文设计的基于FPGA的可调节FIR滤波器系数

2018-07-23 17:21:00 2372

2372

常见的片内滤波器的设计带宽都上兆赫兹,而几十千赫兹带宽的滤波器大多采用片外无源器件来实现。原因是低频滤波器的时间常数巨大,在芯片内占据大量的芯片面积。

2019-01-10 08:01:00 2315

2315

高通滤波器在滤波电路中占据了重要的地位,它和低通滤波器配合可以构成超宽带滤波器,也可以构成通带相接的频率分配器,超宽带的吸收式滤波器也需要采用这个器件。其他结构的滤波器在课本和站上均能找到大量

2020-07-17 10:26:00 3

3 用FPGA实现抽取滤波器比较复杂,主要是因为在FPGA中缺乏实现乘法运算的有效结构,现在,FPGA中集成了硬件乘法器,使FPGA在数字信号处理方面有了长足的进步。本文介绍了一种采用Xilinx公司的XC2V1000实现FIR抽取滤波器的设计方法。

2020-09-25 10:44:00 3

3 数字滤波器、DSP器件或可编程逻辑器件(如FPGA)实现。因为,用FPGA实现数字滤波器具有实时性强、灵活性高、处理速度快以及小批量生产成本低等优点,所以得到了较为广泛的应用。本文以巴特沃思数字带通滤波器为例,较为详细地介绍了其设计和实

2020-08-06 18:50:00 3

3 针对Σ△ADC输出端存在的高频噪声问题,设计了一种 Sinc数字抽取滤波器,实现了Σ-△调制器输出信号的高频滤波。分析了Sinc滤波器的结构原理,基于 Spartan6FPGA进行滤波器的设计与实现

2020-08-26 17:12:00 14

14 一个模拟集成运算放大器可实现一个二阶滤波器,高阶滤波器可由二阶滤波器串联而成。然而,无源元器件实现滤波器的误差值为1.5%或更高,这需要提高元器件的性能。滤波器的典型的调试方法是不断的更换元器件

2020-11-23 16:18:00 1101

1101

WCDMA中规定了小区搜索的时隙同步过程采用匹配滤波器的方法实现,本论文主要研究匹配滤波器原理及FPGA实现结构。

2021-01-26 16:22:43 12

12 提出一种新的高阶FIR滤波器的FPGA实现方法。该方法运用多相分解结构对高阶FIR滤波器进行降阶处理,采用改进的分布式算法来实现降阶后的FIR滤波器。设计了一系列阶数从8到1 024的FIR滤波器

2021-03-23 15:44:54 30

30 引言 目前,用FPGA(现场可编程门阵列)实现FIR(有限冲击响应) 滤波器 的方法大多利用FPGA中LUT(查找表)的特点采用DA(分布式算法)或CSD码等方法,将乘加运算操作转化为位与、加减

2022-12-01 10:20:05 698

698 本文介绍了设计滤波器的FPGA实现步骤,并结合杜勇老师的书籍中的串行FIR滤波器部分进行一步步实现硬件设计,对书中的架构做了简单的优化,并进行了仿真验证。

2023-05-24 10:56:34 552

552

本文介绍了设计滤波器的FPGA实现步骤,并结合杜勇老师的书籍中的并行FIR滤波器部分进行一步步实现硬件设计,对书中的架构做了复现以及解读,并进行了仿真验证。

2023-05-24 10:57:36 653

653

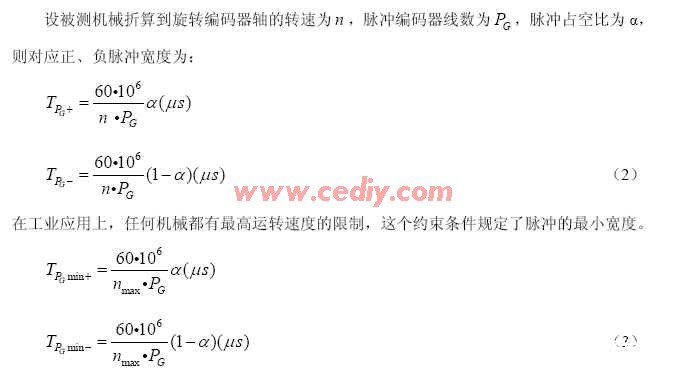

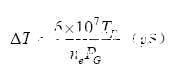

![]() 秒内从静止上升到额定转速,则任意两个相连脉冲的宽度变化为:

秒内从静止上升到额定转速,则任意两个相连脉冲的宽度变化为: (4)

(4)

(5)

(5)![]() 为采样周期内计取的高频时标信号数。

为采样周期内计取的高频时标信号数。

电子发烧友App

电子发烧友App

评论