电子发烧友网核心提示: 根据ALTERA官方FAE(现场应用工程师)的强烈建议,请注意不要随意带电插拔JTAG下载接口,否则会损坏FPGA芯片的JTAG口信号管脚。 现象: 在排除了下载线的问题

2012-09-05 09:00:42 12784

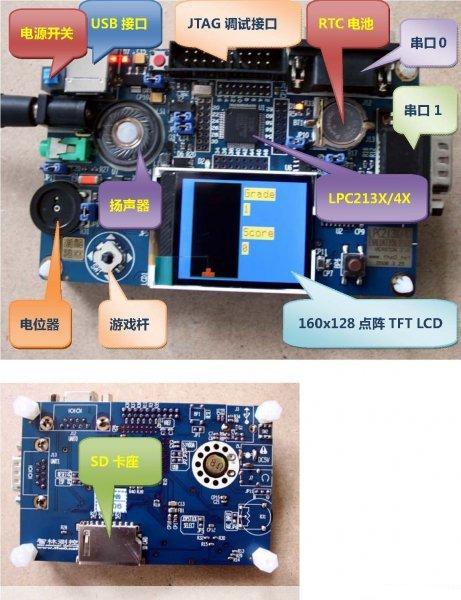

12784 ARM系列处理器正是通过JTAG 接口使用内部集成的ICE 功能, 并采用这种方式实现在线调试。此外CPLD、FPGA 等器件大多都可以使用JTAG 接口实现在线编程或下载。因此,JTAG 接口已经成为复杂芯片系统的必备接口, 在芯片测试、调试及实现其他特殊功能方面发挥着重要作用。

2018-10-16 08:11:00 5801

5801

调试,提示Incorrect clock value。按照网上的方法,已经试过下面的方法了:1.JTAG测了,对地和对电源,没有短路;2.FPGA底部焊盘焊接3.烧写器使用的是USB Blaster,用其他烧写器也试过,不通各位大神,给支支招

2015-10-14 16:00:22

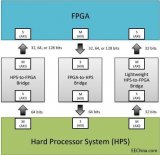

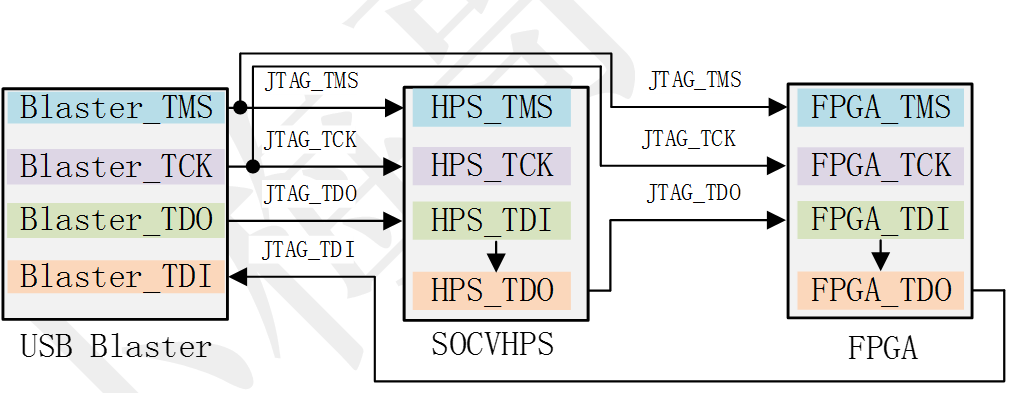

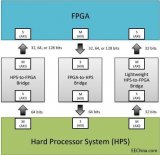

可编程逻辑(FPGA)与硬核处理器(HPS)之间互联的结构

2021-04-02 06:03:40

在线调试方式大都是通过FPGA器件引出的JTAG接口,同时使用了一些FPGA片内固有的逻辑、存储器或布线资源就能够实现的。这些调试功能通常也只需要随着用户设计所生产的配置文件一同下载到目标FPGA器件中

2015-09-02 18:39:49

下载配置与调试接口电路设计FPGA是SRAM型结构,本身并不能固化程序。因此FPGA需要一片Flash结构的配置芯片来存储逻辑配置信息,用于进行上电配置。以Altera公司的FPGA为例,配置芯片

2019-06-11 05:00:07

后,将电路板上电运行。然后把下载电缆接到JTAG接口上,在主机中运行Quartus II软件,并打开Programmer编程器,单击其中的“Auto Detect”按钮进行FPGA下载链路自动检测。若能正确检测到FPGA,说明配置电路是正确连接的。

2012-08-12 11:52:54

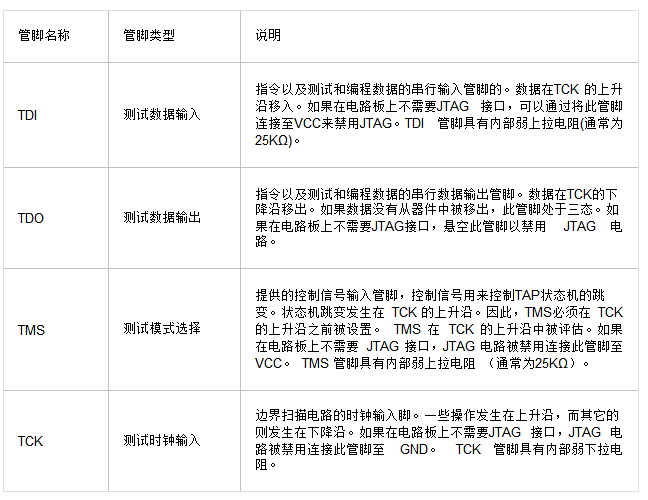

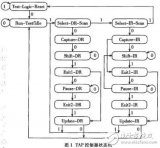

设计和制造技术的快速发展,JTAG越来越多的被用于电路的边界扫描测试和可编程芯片的在线系统编程。(特权同学,版权所有)FPGA器件都支持JTAG进行在线配置,JTAG边界扫描的基本原理如图3.7所示

2019-01-30 02:34:52

`JTAG电路设计规范`

2012-08-20 21:50:52

电路设计[FPGA]设计经验

2012-05-23 19:49:45

电路设计[FPGA]设计经验

2012-08-20 15:37:36

电路设计[FPGA]设计经验

2019-01-03 14:19:28

嗨,我附上了JTAG链设计结构。请看一下。我想在单JTAG链中连接CPLD和FPGA。但是,在我的CPLD中,VCCAUX电压网是1.8V_CPLD而FPGA Bank-0(VCCO_0)电压网

2020-05-29 14:17:04

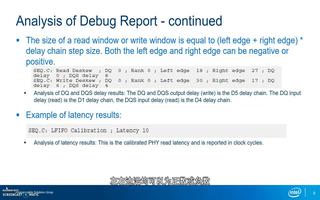

接收端链路均衡测试(Rx LEQ)进入环回模式进行误码率测试

2020-12-02 06:49:35

以下 JTAG 连接错误。

错误:连接失败。

无法正确配置 JTAG 链(CCSProtocolPlugin)

错误:连接失败。

2023-04-23 07:25:01

各位大神,小弟做FPGA不久,最近设计了一个XC3S1500的FPGA板子,经测试电源供电没问题,但是JTAG链路建立不起来,初步怀疑是FPGA芯片和配置芯片(XCF08P)的VCCO不一致

2013-04-03 16:30:12

原谅我记忆力不好。。。花了好久弄明白的东西才十个小时不到就忘记了,所以趁现在记得赶紧记录下来。本文内容:重建de1-soc中HPS-FPGA工程。 PS:原工程在http

2018-07-03 08:10:25

的FPGA或ARM处理器都有一些差异,但是同时两者又有紧密的联系。AC501-SoC开发板上的JTAG链同时连接了FPGA和HPS。使用时,仅需一个JTAG链路,就能同时调试FPGA和HPS。FPGA

2020-02-25 18:40:45

本文由FPGA爱好者小梅哥编写,未经作者许可,本文仅允许网络论坛复制转载,且转载时请标明原作者。Qsys系统和Linux应用程序之间通过一个名为hps_0.h的文件交互硬件信息,例如总线上添加

2020-02-16 18:41:59

循环以从闪存配置FPGA之后,两个JTAG工具都无法看到JTAG链。“Initialize Chain”产生通用的带链错误问题,同时加载匹配的项目文件并尝试对flash进行编程会产生不匹配的ID错误

2019-05-24 14:11:46

由于Quartus®II15.0 Update 2及更早版本中的问题,用于将数据从HPS EMAC内核发送到FPGA内核的时钟缺少时钟分配。因此,这些HPS EMAC到FPGA路径将不会进行时序分析。

2018-07-27 14:27:56

链路预算表用于计算Maxim工业、科学与医疗无线频段(ISM-RF)产品(Tx、Rx、TRx)的链路性能,估算特定的射频电路在几种环境下的通信覆盖范围和链路裕量。该Excel®表格还可用于估算100MHz至10GHz载频范围的其它射频系统的链路裕量。

2019-08-22 07:00:30

收到一条错误消息,指出JTAG电缆已拔下。FLASH可以自己编程而无需扫描链中的FPGA吗?如果是这样,我需要设置IMPACT软件的特殊设置吗?我该怎么做才能调试问题?谢谢!

2020-05-28 13:42:00

)。使用新PCB我遇到了以下问题:1.即使链中有2个器件(Flash和FPGA),JTAG也只检测FPGA。2.我可以选择修改JTAG链。这次我制作了硬件,使JTAG链中只有闪存。现在JTAG检测到闪光灯并且

2020-06-10 10:20:24

通过FPGA器件本身间接的将数据烧录到Flash等外部配置芯片中。另一种下载配置是将配置数据流直接下载到配置芯片中。由于JTAG方式灵活多用,尤其是在线调试非常快速便利,因此我们的FPGA核心板电路中就

2016-08-10 17:03:57

,希望在访问并发上能支持较高的能力,同时可以控制精准度、实时调控、TPS直接压测模式,甚至是大脉冲; 3、希望基于PTS完成全链路压测,需要PTS能方便快捷的提供全局流量的模拟和构造能力; 4、对高可用

2018-01-30 14:13:04

我使用两个独立的位文件在JTAG链中配置了两个FPGA。在这种情况下,完成总是设置为低,尽管影响说“程序成功”。我将完成引脚连接到LED,在那里我看不到LED发光。附加了日志文件。请提出解决方案

2019-05-22 10:32:24

大家好,我们将使用的 MCU 属于 STM32U5 系列。调试探针将是 SEGGER J-Link Base。多个 MCU 使用典型的 JTAG 菊花链连接通过 JTAG 连接

2022-12-20 07:08:46

你好,我在JTAG链中有两个器件 - xc7k160t和一些IR长度= 30的定制ASIC器件。我有以下情况:1.在Vivado 2016.4中 - 当ASIC处于RESET状态时,我看到JTAG链

2020-06-05 15:39:32

海, 我的电路板由2个Kintex-7 fpga和两个独立的BPI闪光灯(微米级闪光灯)组成。如何使用单JTAG连接器(菊花链)progaram 2 fpga?theertha

2020-05-29 13:47:54

大家好,如果两个FPGA连接在单个JTAG链中。那么DONE和INIT引脚的推荐连接是什么。两个FPGA的INIT引脚(也是DONE引脚)是应该连接在一起还是应该分开?Xilinx是否为此推荐了任何

2019-01-10 11:00:55

接入调试端口,而不会干扰JTAG链路的逻辑。在微处理器码调试期间获得微处理器JTAG端口的全部控制,而能够用JTAG调试工具。假如没有测试工具连接到JTAG和编程接头,则固件工程师除希望有到微处理器的链

2019-05-05 09:29:32

我有与FPGA初始化有关的问题,LED INIT改变状态RED和GREEN。因为我无法配置JTAG链.....

2019-09-25 08:17:32

我自己的位文件下载到v5中,但是很失望地发现jtag链无法读取FPGA的器件ID。 swothes sw6和sw3设置为11001010和00010101。和其他设置我需要配置?非常感谢 !

2019-08-16 09:13:46

多个 DSP、FPGA、CPLD 和其他逻辑器件,使得它们可以通过单个 JTAG 连接器进行控制。菊花链常用于具有多个 JTAG 器件的电路板,它可以将 TDI 和 TDO 引脚连接在一起以形成一个

2018-10-11 11:16:23

多片fpga组成jtag链的时候如何加载?

2023-08-11 09:10:26

移植到FPGA上,只有一个JTAG接口。再进行MCU调试的话,是采用其他扩展引脚定位为MCU的JTAG调试?还是使用FPGA的uart串口接口了?

2023-08-11 13:41:00

供了相应的Tcl程序包。有了这套工具,使用sld_virtual_jtag 和相应的Tcl命令,我们就可以构建自己的虚拟JTAG链路,并进行自定义的JTAG调试了。 一、 相关文件 后面的链接

2018-07-03 00:53:26

方法是通过发送Message,即DSP端程序执行时将日志信息以message方式发送到GPP,再由GPP来显示。

4.另外一种方法是通过仿真器来调试DSP端程序,但是能不能同时调试GPP端程序呢,请各位达人给出一点建议,谢谢。

2018-06-21 20:16:33

本帖最后由 一只耳朵怪 于 2018-6-21 15:55 编辑

JTAG调试的下载器选用TI有配套的么?JTAG口在电路设计上可以如FPGA的JTAG口一样设计为2.54间距的排针么

2018-06-21 04:41:08

本帖最后由 一只耳朵怪 于 2018-6-14 08:47 编辑

以前都是使用CCS3.3来进行调试的。现在由于想用新的片子,如F28377,所以准备升级下调试软件平台。先试试CCS4.12,但是发现不会设置同时调试两个片子。有没有知道的,来指导下,谢谢了。

2018-06-13 10:38:00

JTAG调试原理(推荐):ARM JTAG 调试原理

2009-05-27 08:59:49 21

21 JTAG调试原理(推荐):温度循环监测仪

2009-05-27 10:38:59 54

54 JTAG调试原理(推荐):这篇文章主要介绍ARM JTAG调试的基本原理。基本的内容包括了TAP (TEST ACCESS PORT) 和BOUNDARY-SCAN ARCHITECTURE的介绍,在此基础上,结合ARM7TDMI详细介绍了的JTAG调试原

2009-05-27 10:44:50 147

147 这篇文章主要介绍ARM JTAG调试的基本原理。基本的内容包括了TAP (TEST ACCESS PORT) 和BOUNDARY-SCAN ARCHITECTURE的介绍,在此基础上,结合ARM7TDMI详细介绍了的JTAG调试原理。这篇文章主要是

2009-07-14 23:19:49 82

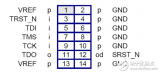

82 JTAG电路设计规范:本技术设计规范根据国家标准和原邮电部标准以及国际标准IEEE STD 1149.1 系列标准编制而成。

目前,使用的芯片中越来越多的CPU、EPLD、FPGA、DSP 以及一些

2009-09-19 07:40:57 93

93 嵌入式JTAG调试方法步骤

嵌入式系统JTAG调试步骤1. 将PC与调试器Multi-ICE用并口连接;调试器与开发板用14或20针的JTAG线连接。2. 依次打开调试器

2010-03-01 16:24:20 34

34 目前通讯电子产品的芯片、单板、系统的复杂度不断提高,物理尺寸却在不断缩小,JTAG电路的设计也随之成为关系到单板可测性、稳定性和可靠性的重要因素。 JTAG测试接口在集成

2010-08-02 16:42:07 0

0 JTAG技术是一种嵌入式调试技术,芯片内部封装了专门的测试电路TAP(测试访问口),通过专用的JTAG测试工具对内部节点进行测试和控制,目前大多数ARM器件支持JTAG

2008-08-24 13:10:39 8144

8144

JTAG调试快速入门

提要:本文介绍 AVR Studio Debug:调试运行方式及QuickWatch实时查看变量的数值。

以下的degug方式,英文版来自 AVR St

2008-10-31 21:58:10 2055

2055

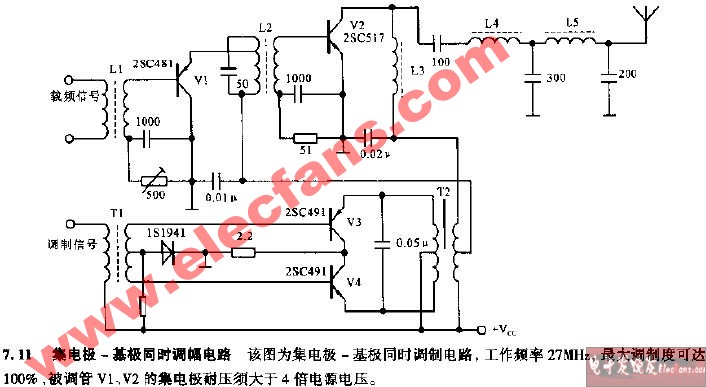

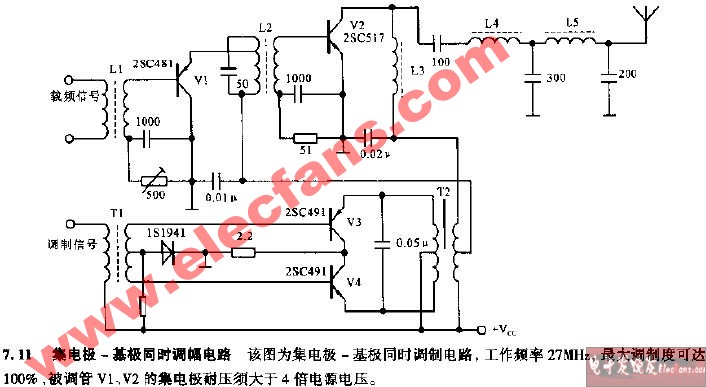

集成极-基极同时调幅电路

2009-03-19 20:17:30 649

649

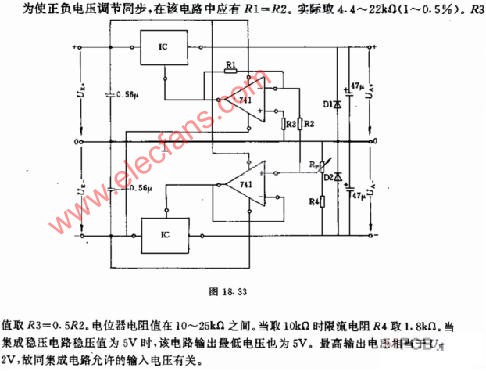

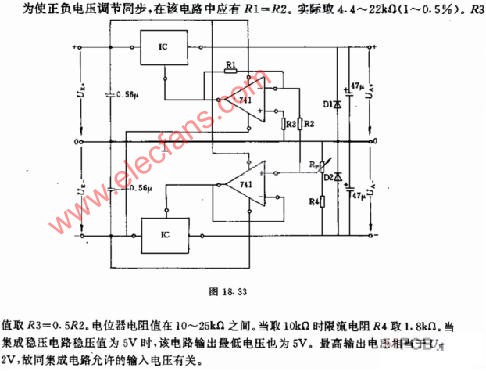

正负电压可同时调节的稳压电路图

2009-05-13 21:34:43 3366

3366

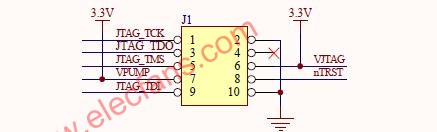

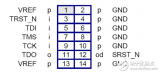

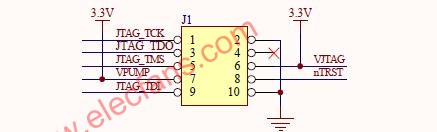

JTAG调试接口电路

注:VPUMP和VJTAG需要接3.

2010-03-17 09:25:56 2554

2554

基于JTAG仿真器的调试是目前ARM开发中采用最多的一种方式。大多数ARM设计采用了片上JTAG接口,并将其作为测试、调试方法的重要组成。

JTAG仿真器通过ARM芯片的JTAG边界扫描

2010-06-30 15:20:03 3001

3001

本内容提供了ARM JTAG调试头和Altera下载线合并电路 详细列举了电路原理图

2011-03-31 17:19:22 209

209 随着 FPGA 的设计速度、尺寸和复杂度明显增长,使得整个设计流程中的实时验证和调试成为当前FPGA 系统的关键部分。获得FPGA 内部信号有限、FPGA 封装和印刷电路板(PCB)电气噪声,这一

2011-06-10 15:42:28 28

28 ARM处理器采用一种基于JTAG的ARM的内核调试通道,它具有典型的ICE功能,基于ARM的包含有Embedded ICE(嵌入式在线仿真器)模块的系统芯片通过JTAG端口与主计算机连接。

2011-08-16 09:51:08 2370

2370

这篇文章主要介绍ARM JTAG调试的基本原理。基本的内容包括了TAP (TEST ACCESS PORT) 和BOUNDARY-SCAN ARCHITECTURE的介绍,在此基础上,结合ARM7TDMI详细介绍了的JTAG调试原理。 这篇文章主要是总结了

2011-11-15 17:35:39 0

0 Altera JTAG下载和调试接口电路图如下图所示:

2012-08-15 14:25:22 13966

13966

电子发烧友网站提供《H-JTAG调试软件下载.exe》资料免费下载

2012-12-18 13:15:34 57

57 在调试FPGA电路时要遵循必须的原则和技巧,才能降低调试时间,防止误操作损坏电路。通常情况下,参考以下步骤执行 FPGA硬件系统的调试。 1、在焊接硬件电路前,首先要测试电路板

2013-01-16 11:59:58 4665

4665 基于FPGA的惯性平台测试保护电路设计..

2016-01-04 17:03:55 7

7 IAR+H_JTAG调试FLASH说明及例程。

2016-02-18 15:11:44 4

4 ARM JTAG 调试原理对于了解jtag结构由很好的帮助。

2016-03-10 14:08:48 10

10 H-JTAG 用户使用手册简单介绍了 H-JTAG 和 H-FLASHER 的基本使用和配置,手册同时也提供了一

些简单的例子供用户参考

2016-05-03 15:15:08 6

6 电路设计[FPGA]设计经验,有需要的下来看看

2016-05-20 11:16:35 46

46 基于FPGA的串口通信电路设计

2017-01-24 17:30:13 33

33 的桥接的,难道FPGA内部有专用的电路去实现这一功能吗? 其实不是的。FPGA内部并没有设计(预留)专用的电路去实现JTAG到Flash的转换,在我们通过JTAG烧写Flash时,电脑其实是先要预下载

2017-02-08 02:40:11 6513

6513

DSP和FPGA的HDLC协议通讯电路设计

2017-10-19 14:46:11 7

7 , FPGA)进行远端升级,本文提出了一种基于XVC (Xilinx visual cable)协议,通过以太网,利用ARM 微控制器控制FPGA 的JTAG 接口对其进行远程更新与调试的方法。该方案附加电路少,易于拓展,同时也提高了更新可靠性。

2017-11-16 20:13:02 12514

12514

JTAG(JointTestActionGroup,联合测试行动小组)是一种国际标准测试协议,主要用于芯片内部测试及对系统进行仿真、调试,JTAG技术是一种嵌入式调试技术,它在芯片内部封装了专门

2018-01-11 09:45:50 28818

28818

为了能够实现HPS与FPGA之间的通信接口,衍生出了AXI bridge协议。AXI bridge协议能够处理带宽适应和时钟控制,支持HPS与FPGA之间双向的逻辑和数据交互。

2018-05-02 17:30:00 6627

6627

如何在预加载器中调试HPS SDRAM

2018-06-20 00:44:00 3023

3023

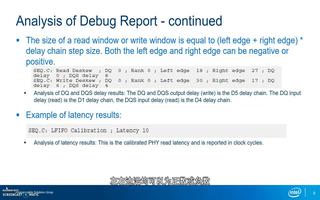

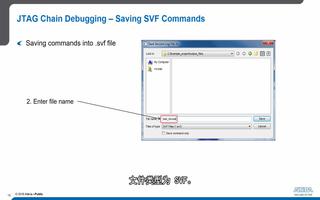

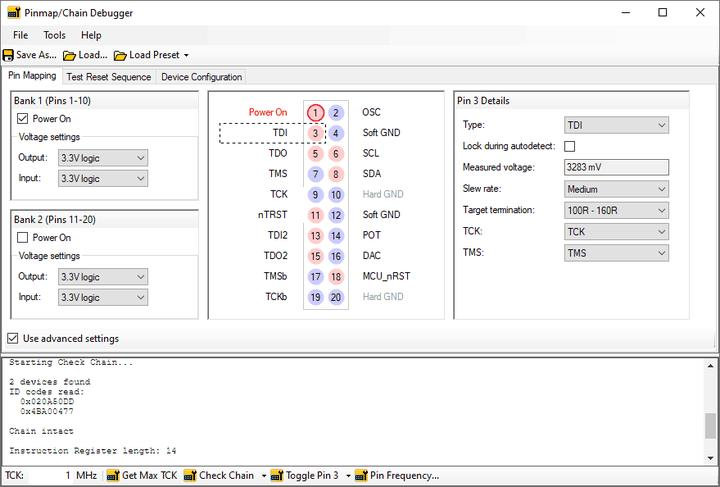

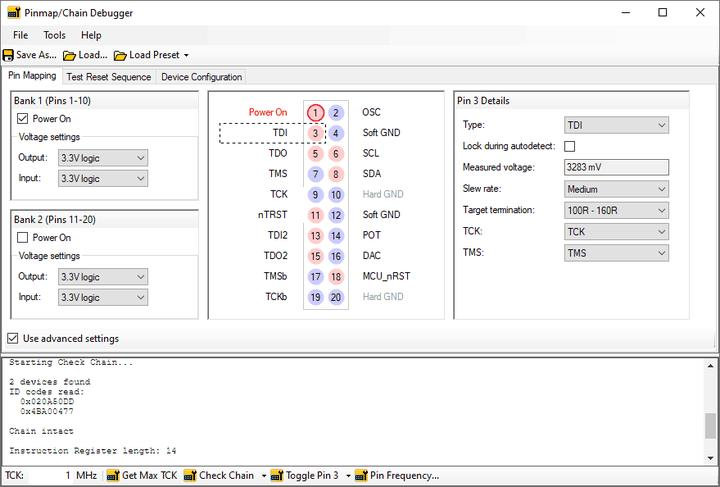

JTAG 链调试程序工具

2018-06-20 01:00:00 3687

3687

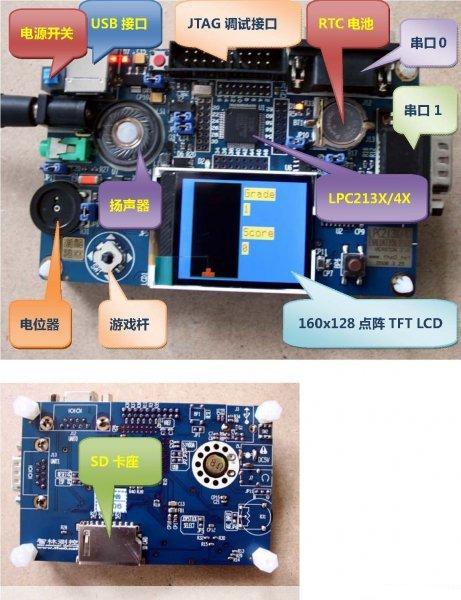

本文档的主要内容详细介绍的是FPGA教程之FPGA硬件最小系统设计的详细资料说明包括了:1.FPGA最小系统概念以及硬件系统的构成,2.FPGA主芯片电路设计,3.JTAG下载与调试接口,4.高速

2019-04-04 17:18:48 101

101 中国大学MOOC

本课程以目前流行的Xilinx 7系列FPGA的开发为主线,全面讲解FPGA的原理及电路设计、Verilog HDL语言及VIVADO的应用,并循序渐进地从组合逻辑、时序逻辑的开发开始,深入到FPGA的基础应用、综合应用和进阶应用。

2019-08-06 06:08:00 3083

3083 产品名称:Jtag调试小板

2019-11-13 09:53:10 2071

2071

对Xilinx ZYNQ-SOC处理器的调试。JTAG-HS3可通过Xilinx 2x7连接器链接到目标板上,同时该产品所有的Xilinx开发工具,包括iMPACT™,ChipScope™和EDK。

2019-11-13 17:12:33 5009

5009

本文档的主要内容详细介绍的是FPGA的硬件电路设计教程和FPGA平台资料简介包括了:FPGA技术概述;主流FPGA器件介绍;VIRTEX-5 FPGA电路设计;V4LX160 FPGA平台介绍;

2020-07-06 18:11:22 158

158 JTAG是Joint Test Action Group的缩写,是IEEE 1149.1标准。使用JTAG的优点:JTAG的建立使得集成电路固定在PCB上,只通过边界扫描便可以被测试。

2020-08-27 14:18:48 2860

2860 本文档的主要内容详细介绍的是FPGA JTAG工具设计的教程说明。

2020-12-31 17:30:55 18

18 赛灵思公司的FPGA芯片具有IEEE 1149.1/1532协议所规定的JTAG接口,只要FPGA上电,不论模式选择管脚M[1:0] 的电平,都可用采用该配置模式。JTAG模式不需要额外的掉电

2020-12-31 17:30:55 13

13 开发板(在本文中将其简称为“FPGA开发板”)和专用 JTAG 调试器(在本文中将其简称为“JTAG 调试器”)。

2021-03-23 10:00:28 41

41 利用FPGA的在系统下载或重新配置功能,可以在电路设计和调试时改变整个电路的硬件逻辑关系,而不需要改变印制电路板的结构。

2021-05-12 10:46:10 25

25 FPGA CPLD数字电路设计经验分享.(电源技术发展怎么样)-FPGA CPLD数字电路设计经验分享

2021-09-18 10:58:03 51

51 使用Jtag Master调试FPGA程序时用到tcl语言,通过编写tcl脚本,可以实现对FPGA的读写,为调试FPGA程序带来极大的便利,下面对FPGA调试过程中常用的tcl语法进行介绍,并通过tcl读FIFO的例子,说明tcl在实际工程中的应用。

2022-02-19 19:44:34 2272

2272 对FPGA进行上板调试时,使用最多的是SignalTap,但SignalTap主要用来抓取信号时序,当需要发送信号到FPGA时,Jtag Master可以发挥很好的作用,可以通过Jtag Master对FPGA进行读写测试

2022-02-16 16:21:36 1900

1900

实用电子电路设计与调试数字电路教材资料免费下载。

2022-04-07 14:46:38 26

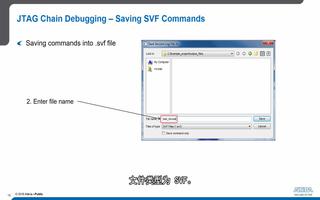

26 JTAG链调试器(JTAG Chain Debugger),随XJTAG的安装包一起安装,是一个功能强大的工具,旨在帮助您解决JTAG链的问题。

2023-07-19 14:41:07 319

319

因为目前软件的限制,RISCV的逻辑不能同时共用JTAG,所以如果想要同时去调试逻辑和RISCV的话,可以通过RISCV的soft Jtag来实现。soft Jtag就是通过GPIO来实现的软件

2024-02-23 16:16:12 110

110

电子发烧友App

电子发烧友App

评论