1.引言

本文所介绍的数据采集系统是基于ARM的信号处理系统中的一部分,该信号处理系统用于导弹的数字式自动驾驶仪的开发研究中。整个系统由信号放大、信号滤波、信号采样、高速数字信号处理等部分组成。其中,数据采集系统是一个重要的环节,它的高速性和准确性直接影响到整个信号处理系统的性能。传统方法是应用CPU通过软件控制模数转换,这样必将频繁中断系统的运行从而减弱系统的数据运算能力,数据采集的速度也将受到限制。因此,本文利用可编程逻辑控制器CPLD,由硬件控制模数转换和数据存储,从而最大限度地提高系统的信号采集和处理能力。

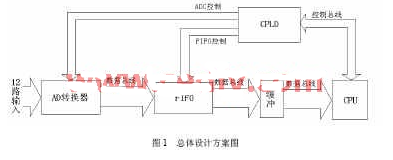

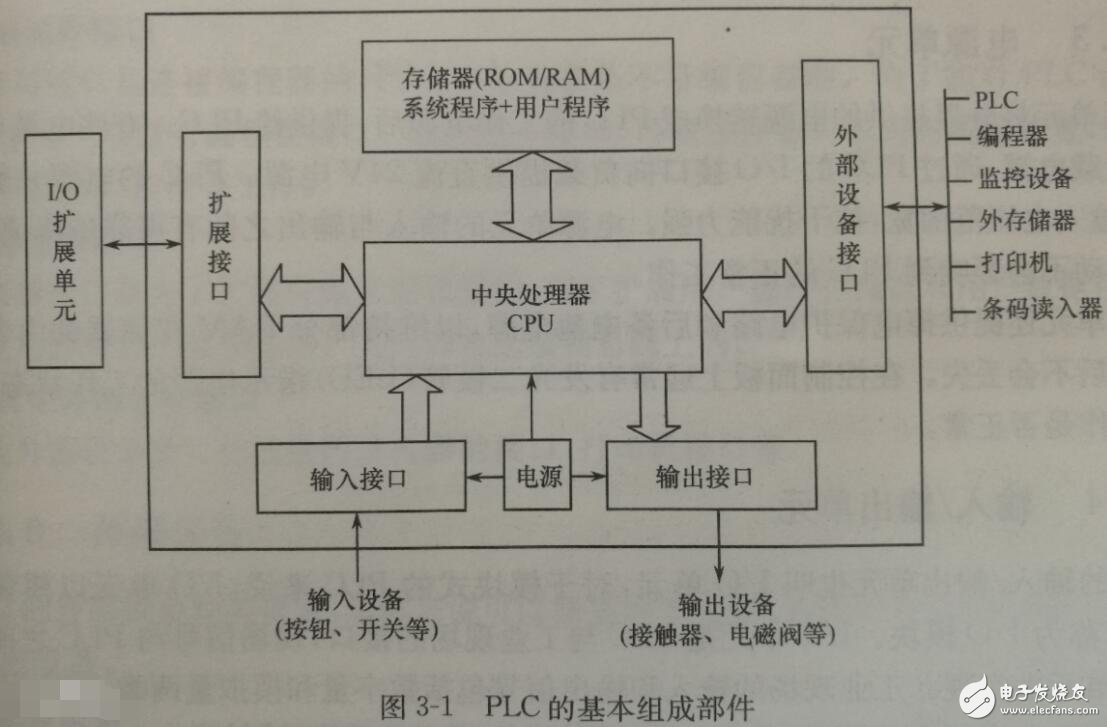

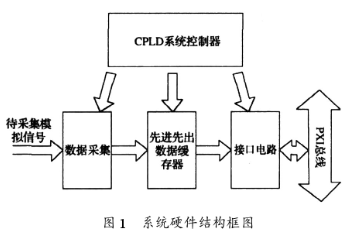

2.系统总体设计方案

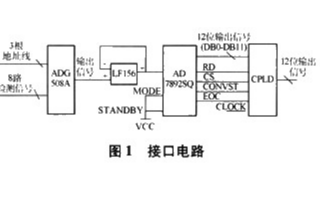

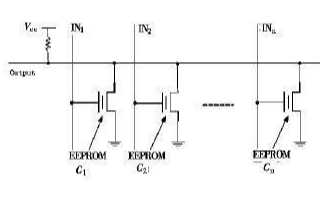

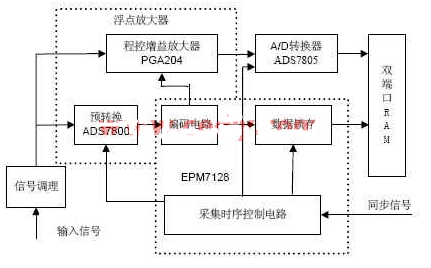

数据采集系统的总体设计方案如图1所示。基于Verilog HDL设计的自动状态机由硬件控制A/D转换以及自动向FIFO中存储数据,当采样数据达到要求时,向CPU申请中断,ARM系统启动DMA完成数据读取。待CPU取走数据后,给状态机一个复位信号,同时对采集到的数据进行高速处理。这期间数据采集不中断,从而实现连续的实时数据采集和实时数据处理。数据采集系统由A/D芯片AD7656、逻辑控制芯片EPM7128、FIFO芯片CY7C425以及缓冲74LVT245组成,控制逻辑用Verilog HDL语言描述。

3.硬件设计

3.1 A/D转换芯片

系统的A/D转换芯片采用AD7656,一个AD7656芯片拥有6个16位逐次渐进模数转换器,在5V电压供电下采样率为250kSPS。芯片中的采样保持放大器最大处理输入频率为8MHz。转换过程和数据获取由CONVST信号和内部时钟控制,三个CONVST管脚可以控制三对独立的模数转换器同时采样。AD7656根据内部参考电压2.5V可提供±10V或者±5V的双极性模拟量输入范围,或者根据外部参考电压提供不同范围的双极性模拟量输入信号。

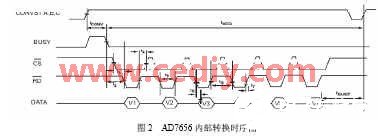

AD7656的内部转换时序图如图2所示。将三个CONVST管脚连接在一起后,即可对六个A/D转换器同时进行采样。CONVST的上升沿触发A/D转换,转换时间为3µs。转换过程中,BUSY信号保持高电平不变,直到转换结束时,BUSY信号由高变低,系统进入跟踪模式,转换结果存于输出数据寄存器中。当片选信号 保持低电平不变时,连续六个读信号 低电平能够依次读出六个A/D转换器的转换数据。

3.2 FIFO存储器

系统的FIFO存储器采用CY7C425,它是CYPRESS公司采用CMOS工艺制造的1K×9位可以实现先进先出算法,可以进行异步读写操作的双端口存储器。它提供全空 、全满 、半满 状态标志,用以防止数据溢出或不足。扩展逻辑电路允许多片FIFO进行数据宽度和存储深度的扩展而不会增加额外的时间延迟。

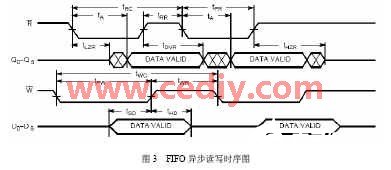

CY7C425的异步读写时序图如图3所示。当写信号 为低电平时发生写操作,A/D转换的结果通过写操作不断存入FIFO中,存入一定数量的数据后,再通过读信号 将FIFO中的数据依次读入CPU中。采用两片CY7C425扩展为16位1024字的高速异步FIFO存储器,数据处理速度达到50MHz,可以实现数据的高速写入和高速读出。

3.3 状态机模块

状态机FSM完成自动A/D转换和数据存储,控制芯片是EPM7128。此状态机由系统时钟驱动,控制A/D转换器的转换、FIFO的复位及写数,并产生中断信号通知CPU读取数据。由于系统使用了两片AD7656,而不同芯片的个体会有差别,同一器件也会有温漂、时漂还有老化的问题,如果采用中断方式取数,很有可能会引起各个通道A/D采样率不一致并且单个通道A/D工作时采样率也不恒定。因此,可以不管BUSY信号,只需要把各段的时序留够足够的裕量就可以了,譬如AD7656的转换时间是3µs,那么,只要状态机保持CONVST至少3µs的高电平,这样就可以完全确定A/D转换的结束。这样控制器就可以不需要检测A/D的BUSY信号,同时也能很准确地保证采样速率了。

系统复位时,转换信号CONVST及FIFO复位信号MR保持低电平不变,此时不进行数据采集。系统复位后,CONVST上升沿触发转换开始,系统进入采样保持阶段。3µs后,待A/D转换结束,连续产生12个A/D读脉冲,可以依次读出12个通道的转换结果。取数的同时产生FIFO的写脉冲,可将读出的数据连续写入FIFO中。为利于CPU中处理软件的编写,CPLD中设置了一个计数器,可以进行32(2的5次方)次采样。最后发送中断信号到CPU,CPU通过DMA方式将数据全部读入内部存储器,数字滤波通过取和以后右移5位即可进行。

4.Verilog HDL描述

电子系统设计中一般遵循自上而下的设计思路,对系统进行设计、描述与仿真。考虑到模块的通用性、移植性,常常使用硬件描述语言来描述数字系统,如Verilog HDL、VHDL、AHDL语言等。其中Verilog HDL语言具有结构清晰、文法简明、功能强大、高速模拟和多库支持等优点,被近90%的半导体公司使用,成为一种强大的设计工具。

4.1 用Verilog HDL语言描述自动状态机

自动状态机有两个输入信号和七个输出信号。输入信号中CLK由CPU的输出频率提供,产生50MHz的时钟频率,RST由CPU提供,负责复位状态机。CONVST产生A/D转换器的转换启动信号;ADC_CS、ADC1_RD、 ADC2_RD分别是两个A/D转换器的片选信号以及读信号;FIFO_WR和 FIFO_MR控制FIFO的读数和复位;中断信号INT通知CPU在DMA方式下取数。程序如下:

module fsm(RST, CLK, CONVST, ADC_CS, ADC1_RD, ADC2_RD, FIFO_WR, FIFO_MR, INT);

input RST, CLK;

output CONVST, ADC_CS, ADC1_RD, ADC2_RD, FIFO_WR, FIFO_MR, INT;

reg CONVST, ADC_CS, ADC1_RD, ADC2_RD, FIFO_WR, FIFO_MR, INT;

parameter ST0=8‘b00000000, ST150=8’b10010110, ST152=8‘b10011000, ST153=8’b10011001,

ST155=8‘b10011011, ST156=8’b10011100, ST158=8‘b10011110, ST159=8’b10011111,

ST161=8‘b10100001, ST162=8’b10100010, ST164=8‘b10100100, ST165=8’b10100101,

ST167=8‘b10100111, ST168=8’b10101000, ST170=8‘b10101010, ST171=8’b10101011,

ST173=8‘b10101101, ST174=8’b10101110, ST176=8‘b10110000, ST177=8’b10110001,

ST179=8‘b10110011, ST180=8’b10110100, ST182=8‘b10110110, ST183=8’b10110111,

ST185=8‘b10111001;

reg[7:0] COUNTER;

reg[4:0] CN;

always @(posedge CLK)

if(!RST)

begin COUNTER《=0; ADC_CS《=1; ADC1_RD《=1; ADC2_RD《=1;

FIFO_WR《=1; FIFO_MR《=0; CONVST《=0; CN《=0;INT《=0; end

else if(CN》=5’b11111)

begin INT《=1; COUNTER《=0; ADC_CS《=1; ADC1_RD《=1;

ADC2_RD《=1; FIFO_WR《=1; FIFO_MR《=0; CONVST《=0; end

else

begin

if(COUNTER《8‘b11001100)

COUNTER《=COUNTER+8’b00000001;

else

begin CN《=CN+5‘b00001; COUNTER《=0; end

case(COUNTER)

ST0: begin CONVST《=1; FIFO_MR《=1; end

ST150: begin ADC_CS《=0; ADC1_RD《=0; FIFO_WR《=0; end

ST152: begin FIFO_WR《=1; ADC1_RD《=1; end

ST153: begin FIFO_WR《=0; ADC1_RD《=0; end

ST155: begin FIFO_WR《=1; ADC1_RD《=1; end

ST156: begin FIFO_WR《=0; ADC1_RD《=0; end

ST158: begin FIFO_WR《=1; ADC1_RD《=1; end

ST159: begin FIFO_WR《=0; ADC1_RD《=0; end

ST161: begin FIFO_WR《=1; ADC1_RD《=1; end

ST162: begin FIFO_WR《=0; ADC1_RD《=0; end

ST164: begin FIFO_WR《=1; ADC1_RD《=1; end

ST165: begin FIFO_WR《=0; ADC1_RD《=0; end

ST167: begin FIFO_WR《=1; ADC1_RD《=1; end

ST168: begin FIFO_WR《=0; ADC2_RD《=0; end

ST170: begin FIFO_WR《=1; ADC2_RD《=1; end

ST171: begin FIFO_WR《=0; ADC2_RD《=0; end

ST173: begin FIFO_WR《=1; ADC2_RD《=1; end

ST174: begin FIFO_WR《=0; ADC2_RD《=0; end

ST176: begin FIFO_WR《=1; ADC2_RD《=1; end

ST177: begin FIFO_WR《=0; ADC2_RD《=0; end

ST179: begin FIFO_WR《=1; ADC2_RD《=1; end

ST180: begin FIFO_WR《=0; ADC2_RD《=0; end

ST182: begin FIFO_WR《=1; ADC2_RD《=1; end

ST183: begin FIFO_WR《=0; ADC2_RD《=0; end

ST185: begin FIFO_WR《=1; ADC2_RD《=1; ADC_CS《=1; CONVST《=0; end

endcase

end

endmodule

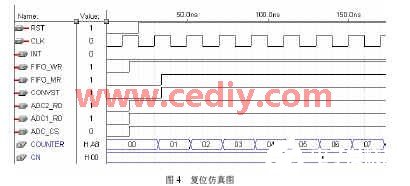

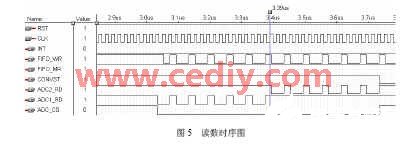

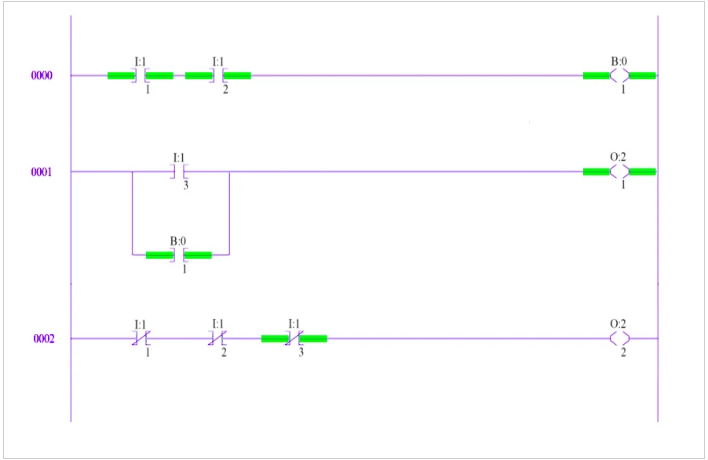

4.2 仿真图形

图4为状态机复位时的仿真图形。由图可以看出,当按下复位键时,A/D转换信号CONVST保持为低电平,A/D转换器不采集数据。同时,FIFO复位信号FIFO_MR也保持低电平不变,可将FIFO中的数据清空。当复位信号变高后,在外部时钟CLK的第一个上升沿,CONVST电平升高,开始A/D转换(存在时延)。

图5为状态机从A/D转换器将数据读入FIFO中的时序图。由图可知,3µs(A/D转换器的转换时间)后,分别通过对ADC_CS、ADC1_RD、ADC2_RD、FIFO_WR信号的控制,实现将12路通道的数据依次读入FIFO中的操作。

5.结束语

本文提出的自动数据采集系统采用CPLD芯片,用硬件描述语言设计自动状态机,实现硬件控制数据采集和存储。目前采集系统应用于开发数字式自动驾驶仪的ARM实验应用板上,省去了ARM监控A/D芯片的时间,使信号处理系统能够高效地工作。通过调整状态机中的采样次数或采用转换速率更高的A/D芯片可进一步提高系统的数据采集速度。

责任编辑:gt

电子发烧友App

电子发烧友App

评论