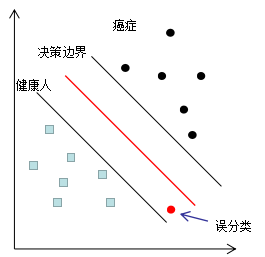

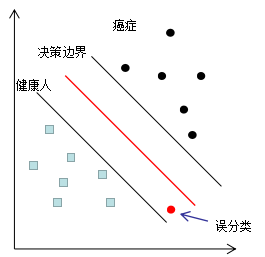

Adaboost 算法是Freund 和Schapire 于1995 年提出的,全称为Adaptive Boosting。它是 Boosting 算法的改进,意为该算法通过机器训练与学习不断自适应地调整假设的错误率,这 种灵活性使得Adaboost 算法很容易与实际应用联系起来。

2019-08-28 07:05:11

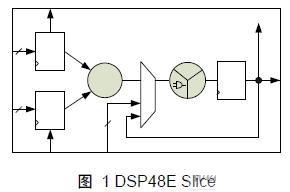

FPGA的方案选择 幸运的是,需要高性能DSP功能的便携式设备设计者还有其它选择。最近FPGA开始达到了应用所要求的成本竞争力。优选的FPGA方案可用来处理计算量繁重的高端DSP算法,同时还可

2011-02-17 11:21:37

VIRTEX-5FPGA - DC and Switching Characteristics - Xilinx, Inc

2022-11-04 17:22:44

你好我正在尝试使用Virtex 5,XUPV5,LX110T的VGA,但我的显示器屏幕上没有任何东西(没有屏幕)。相同的代码正在使用spartan 3e,现在我正在使用USER_CLK(100

2019-08-26 14:03:48

使用Virtex5就可以了。我尝试了Xilinx ISE 10.1.02和9.2.04i - 结果相同。我读了AR#31574。我认为这不是我的情况。我使用“-ignore_keep_hierarchy”选项

2020-06-01 16:50:55

Virtex5无法正确读取XCF32P。 Impact可以编程到PROM和VIRTEX5,但是当Virtex5上电时,看起来PROM只在D0上输出串行数据,D1..D7为高电平(3.3V

2020-05-27 13:35:05

类型为'ABC_sig_div_16_5_2clk'的逻辑根块'ABC_sig_div_16_5_2clk'未展开。目标'virtex5'不支持符号'ABC_sig_div_16_5_2clk'。我在

2018-09-28 11:35:48

嗨,我正在使用virtex5,我想设置rocketIO。我红了很多文档和用户指南,但因为有太多的东西我迷路了,我不知道如何开始。感谢向导,我能够生成IP核,但是在我失去了实现IP核之后。在生成的例子

2020-06-04 11:19:14

嗨,我正在一个项目中工作,我需要直接使用我的设计ICAP_VIRTEX5。我记得2年前曾读过关于这个街区的事情,但现在我再也找不到了。此外,我不只是谈论Virtex5的HDL文档或其中一个

2020-06-17 16:35:39

嗨,我想在FPGA中捕获串行ADC样本。我将ADS5281(12位,50Msps)连接到Virtex5 SX95T。ADC时钟和数据馈入Virtex5中的iDDR。如果adc时钟低至120 MHz

2020-04-17 09:26:34

18 幅图像的速度每秒处理 3,015 幅图像。† 这些数字表明,英特尔 Stratix 10 FPGA 在处理大批量任务时完全可媲美其他高性能计算(HPC)器件(如 GPU), 在处理小批量任务时则比其他器件更快。

2019-07-17 06:34:16

? Spartan6是否包含基板高性能电容器,如Virtex5和6?具有推荐的旁路上限值的其他人的经验是什么?谢谢!以上来自于谷歌翻译以下为原文We're laying outa Spartan 6

2019-05-29 07:36:22

Stratix III FPGA与Xilinx Virtex-5的体系结构对比Stratix III FPGA与Xilinx Virtex-5的性能对比

2021-05-07 07:00:14

请问:C6000系列的DSP在矩阵求逆计算时,计算速度和功耗方面,与Xilinx Virtex5的FPGA相比,是否会有优势?

2018-12-25 11:20:12

产物。Xilinx Virtex-II 系列平台 FPGA 提供了现有任何可编程逻辑解决方案的最高性能和最高密度。基准测试程序表明,该系列产品在系统性能上比最相近的竞争器件高出 38%。尽管容量从四万到八百万系统

2013-09-06 16:28:27

你好,我使用Xilinx Virtex5,我安装了ISE Suit Desgin。系统生成器配置有Matlab R2013a。当我启动系统生成器时,matlab打开,几秒钟后它会自动关闭。有时它会给我一个错误:未知的软件异常0xc00000d。你能帮我解决这个问题吗?亲切的

2020-05-18 08:39:45

你好,我正在通过平台电缆USB使用带有iMPACT的Virtex5编程公司板。我正在使用JTAG模式,“初始化链”可以识别微处理器和FPGA并提示输入bsd / bit文件。提供这些后,我可以成功

2020-06-02 10:30:49

你好,我正在尝试在zynq设备上实现一个设计。我已经在Virtex5设备上实现了它,它的工作非常好。但是当我更改设备时,我在放置和路由阶段得到了以下错误。我更改了UCF文件,但我不明白这个错误

2018-10-15 11:52:53

为什么推出Virtex-5LXT FPGA平台和IP解决方案?如何打造一个适用于星形系统和网状系统的串行背板结构接口FPGA?

2021-04-29 06:18:31

嗨, 我正在开发一种设计,我们的主板有1个virtex5 fpga和9个从属卡,每个都有1个V5 fpga。我想同步所有9个从卡的操作。我还希望主卡和从卡之间的数据传输速率为300-400Mbps

2019-01-30 06:52:36

嗨,Actuallay我正在研究Xilinx大学计划的Virtex5评估委员会,我有两个问题:第一个是,以太网应用需要与Virtex5一起使用的硬件资源是什么,换句话说,如果我应该传输基于V5

2020-06-02 06:20:56

关于Virtex-5 FXT平台的知识点看完你就懂了

2021-05-06 06:48:57

各位前辈好!我在用Xilinx Virtex5 FPGA做通过千兆网和上位机通信,有几个问题想请教:1、tri-mode ethernet mac 和 virtex-5 embedded

2016-05-31 22:41:53

嗨,我正在开发一个项目,我们正在使用Virtex-5 FPGA从ADC捕获信号,样本存储在128K x 256 SRAM上,数据样本由PC采集。我相信Virtex-5为BRAM提供了一个选项,虽然我

2020-06-17 11:31:47

嗨我正在回读并擦洗XC5VFX130T,当在Virtex5中清除部分配置存储器时,DONE引脚的行为是什么?保持高电平还是取消激活?不管怎么说,还是要谢谢你!handoujack。

2020-06-16 16:11:39

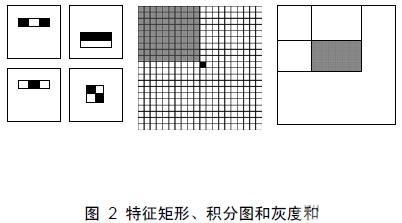

【作者】:郑夜星;林其伟;【来源】:《电视技术》2010年02期【摘要】:提出在增强层中引入一种快速的AdaBoost人脸检测算法,定位出人脸区域,进行位平面提升,优先传输。在基本层引入基于增强层

2010-04-23 11:23:20

的数据可以被写入 Virtex-5 FPGA 中的内置 FIFO36 模块。基于 CQ 的数据采集机制要求将读时钟(CQ 和 CQ)置于 clock-capable I/O (CCIO) 中,时钟从这

2019-04-22 07:00:07

嗨, 我使用的是Virtex-5 FPGA,DDR2 MIG,我的ISE版本是13.2。 我的phy_init_done信号没有被断言。我发现校准序列卡在阶段2.阶段3从未到达。请提供有关上述原因的信息?

2020-06-15 11:52:03

/Metastable-Delay-in-Virtex-FPGAs/ba-p/7996有Virtex4和Virtex5的测量。我正在寻找Virtex6和7Series部件的类似亚稳态参数测量。是否存在应用说明?我猜猜V6& 7应该比

2020-07-18 16:58:50

嗨,我有一个ml505 virtex5板。我已经编程了几个月,我的意思是我可以使用它。但今天我无法编程,因为我错误地清理了舞会和名为xc94144xl的东西。我在“冲击/边界扫描/初始化链”即正常

2020-07-13 09:47:28

是否可以将Spartan3 FPGA的3.3V LVCMOS o / ps连接到Virtex 5的2.5V LVCMOS输入,反之亦然。

2020-06-16 14:42:03

AdaBoost算法实现

2019-11-07 09:19:29

你好我在virtex5 FX200T中使用LogiCORE IP SerialRapidIO v5.6 ipcore。1)我的查询是提供的用户指南,ug503不包含任何模拟结果,任何人都可以帮我验证我的设计。2)如果可能,请参阅包含ipcore详细说明的文件。谢谢&问候,马杜

2020-03-17 09:46:07

大家好我们必须写一个vhdl解码器代码解码器特别是用状态机构建我们怎么知道对于一个FPGA的好工作有多少状态(例如virtex5 FX100t)?谢谢你的回答沙洛姆以上来自于谷歌翻译以下为原文

2019-01-17 09:18:12

大家好,我对FPGA技术还不熟悉,而且我正在学习。我对DDR2 SRAM感到困惑,当我创建一个程序时...说一个寄存器,fifo等,数据是存储在Virtex5部分还是存储在板上的SRAM内存中?谢谢!-Mike!

2020-05-27 12:20:31

嗨,我是学生 我尝试使用virtex5与部分重新配置教程UG702,但本教程设计为virtex6(ML605)所以我需要修复它 为virtex5创建新的综合和网表(从源代码复制.v文件并运行合成

2020-06-16 07:28:38

刚刚学习FPGA,不知道怎么用virtex5,想看看例程,网上找不到,想问问各位大神,能给给看看么

2014-12-03 21:56:05

请问有没有基于太空级Virtex FPGA的灵活高性能计算平台?

2021-04-15 06:01:10

大家好我正在使用Virtex5 FPGA,我在设计中添加了一个OFFSET IN约束,如下所示。NET“Sysclk”TNM_NET =“Sysclk”;TIMESPEC“TS_Sysclk

2020-06-13 19:23:05

“u_fifo_generator_v9_3”。引脚名称拼写错误可能导致此问题,缺少edif或ngc文件,块名称与edif或ngc文件名之间的大小写不匹配,或者类型名称的拼写错误。目标'virtex5'不支持符号'fifo_generator_v9_3'。你能帮我解决一下这个问题吗?

2020-04-26 12:14:08

你好朋友, 我已经获得了Virtex5 FPGA应用笔记XAPP856,根据图6和表3,我们不能使用DCM和BUFG驱动OSERDES来实现SFI-4.1。因为Virtex 5系列中的DCM最多可以

2020-06-10 12:48:08

我想通过virtex5配置9361,是不是只要用Verilog通过spi配置寄存器就可以使9361工作?

2018-12-13 15:08:43

谁有Virtex5 FPGA到TI公司64系列的EMIF设计文档??如果有的话,发给我一下,多谢啦

2012-11-22 15:24:57

【来源】:《电子设计工程》2010年02期【摘要】:<正>赛灵思公司与联华电子共同宣布,采用联华电子高性能40nm工艺的Virtex-6FPGA,已经完全通过生产前的验证

2010-04-24 09:06:05

我试图了解速度等级,我发现了很多相互矛盾的信息。在Virtex5数据表中,速度等级列为-1,-2和-3。这是什么意思?速度等级如何影响FPGA的选择?

2020-05-27 14:08:15

我在同一JTAG链上有一个带有8个器件的电路板:4个Xilinx XCF32P闪存,2个Xilnix Virtex-5 LX155和2个Broadcom PHY。4个Xilinx EPROMS和2个

2020-06-03 12:38:25

赛灵思多平台Virtex-4 FPGA的性能及应用

赛灵思(Xilinx)的Virtex-4现场可编程门阵列(FPGA)是首款基于ASMBL(Advanced Silicon Modular Block)架构的多平台FPGA系列。通过采用不同的平台(LX、FX

2009-06-26 08:11:39 41

41 Xilinx公司的Virtex-5 FXT FPGA器件在业界率先集成了嵌入式PowerPC 440处理器模块、高速RocketIO GTX收发器和专用XtremeDSP 处理能力。作为65nm Virtex-5系列的第四款平台,Virtex-5 FXT提供了极高的

2009-11-24 11:17:22 32

32 赛灵思宣布开始向市场交付针对高性能数字信号处理(DSP)而优化的65 nm Virtex-5 SXT现场可编程门阵列(FPGA)器件的首批产品。SXT平台创造了DSP性能的行业新纪录--550MHz下性能达352 GMAC

2009-11-28 14:08:02 23

23 Virtex-6 FPGA GTX收发 User Guide:This document shows how to use the GTX transceivers in Virtex

2009-12-31 17:05:28 25

25 Virtex-5FPGA系列器件自带的系统监测器模块为数字多普勒接收机中片上温度和供应电压的监测提供一种简单而高效的解决方案。在Xilinx ISE10.1开发平台中,利用Xilinx提供的系统监测器模

2010-02-11 11:09:59 24

24 Virtex-4 FPGA应用指南

使用Virtex-4器件的DDR2控制器(267MHz及以上)

DDR2SDRAM器件提供了比DDRSDRAM指标所要求的更好的新功能,并允许DDR2器件以666Mb/s的数据

2010-05-13 14:14:26 39

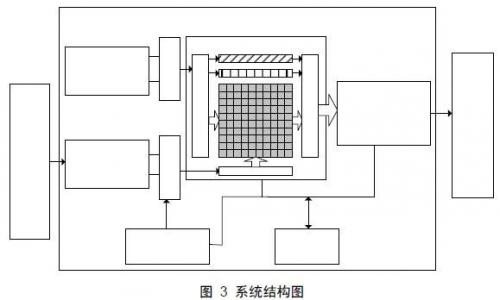

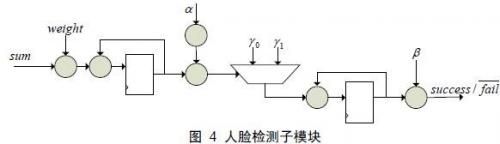

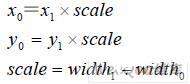

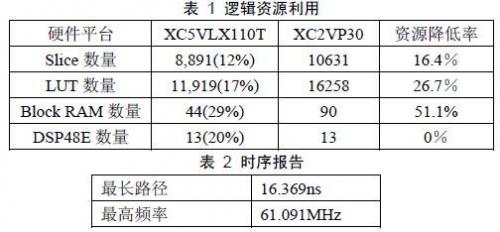

39 Adaboost算法采用由弱到强的级联型分类器用以快速检测人脸。但在实际应用中计算量巨大。在PC机上用纯软件实现该算法得到的目标检测速度也难以达到实时。本文论述了一种采用像

2010-07-17 18:11:57 22

22

针对传统模拟电路阈值检测方法存在的缺点,设计出采用高速A/D转换器和高性能Virtex5 FPGA实现激光测距系统。该系统可以大大降低系统误差,提高测距精度。

2010-12-17 16:29:11 47

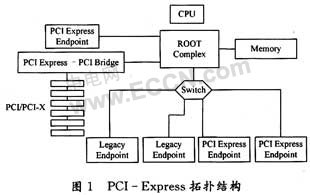

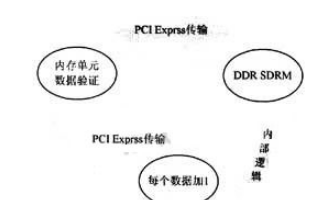

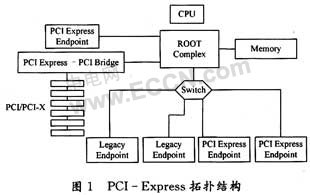

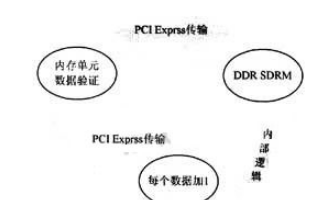

47 基于Virtex5的PCI-Express总线接口设计

PCI Express是由Intel,Dell,Compaq,IBM,Microsoft等PCI SIG联合成立的Arapahoe Work Group共同草拟并推举成取代PCI总线标准的

2009-10-05 10:25:20 910

910

赛灵思高性能40nm Virtex-6 FPGA系列即将转入量产

赛灵思公司(Xilinx, Inc.)与联华电子(UMC)今天共同宣布,采用联华电子高性能40nm工艺的Virtex-6 FPGA,已经完全通过生产前的验

2010-01-26 08:49:17 851

851 Virtex-6 FPGA ML605开发评估技术方案

Virtex-6 FPGA是Xilinx公司的目标设计平台,提供集成的软件和硬件,有利于设计集中力量进性产品创新. Virtex-6系列包括LXT, SXT和HXT子系列,适

2010-04-22 18:07:58 3615

3615

Discete-AdaBoost算法 1、给定训练集: ,其中 ,表示 的正确的类别标签, , 表示第i副图像的第j个特征值 2、训练集上样本的初始分布: 3、寻找若分类器 ht( ) (1)对于每个样本中的第j个特

2011-07-18 10:40:30 0

0 Virtex-7 2000T FPGA的容量是市场同类最大28nm器件的2倍,而且比赛灵思最大型Virtex-6 FPGA大2.5倍。虽然2000T由4个切片组成,但它仍然保持着传统FPGA的使用模式,设计人员可通过赛灵思工具流程

2011-10-26 09:11:30 2795

2795 由于Virtex-5 器件的基础架构与以往的FPGA 器件不同,因此,要为特定设计选择合适的Virtex-5 器件并非易事。大多数情况下,设计应采用类似的阵列大小(器件数量)并且比以前的目标器

2012-01-17 17:36:22 33

33 Virtex-5 器件包括基于第二代高级硅片组合模块 (ASMBL) 列架构的多平台 FPGA 系列。集成了为获得最佳性能、更高集成度和更低功耗设计的若干新型架构元件,Virtex-5 器件达到了比以往更高

2012-02-17 14:39:56 51

51 为解决北斗导航接收机干扰功率强、有效信号弱的不足,提出了一种基于功率倒置自适应算法的抗干扰设计方案。该方案以自适应天线系统为平台,采用FPGA处理器Virtex5芯片实现自适应

2012-03-20 10:48:17 68

68 针对GPS接收机有效信号弱,易受窄带干扰影响的不足,提出了一种基于FPGA的窄带干扰抑制算法的实现方案。该方案以Xilinx公司的Virtex5芯片为硬件平台,采用重叠加窗频域滤波算法和自

2013-09-23 15:16:43 45

45 基于AdaBoost_Bayes算法的中文文本分类系统_徐凯

2017-01-07 18:56:13 2

2 Virtex UltraScale™ FPGA VCU108 评估套件是评估 Virtex UltraScale 器件所提供前所未有高性能、高系统集成度以及高带宽的完美开发环境。该套件是需要海量

2017-02-08 14:19:11 478

478 部分可重构技术是Xilinx FPGA的一项重要开发流程。本文结合Virtex5 FPGA,详细讲解在ISE + Planahead上完成部分可重构功能的流程和技术要点。

2018-07-04 02:17:00 3419

3419

赛灵思Virtex® UltraScale ™ All Programmable FPGA 是高端FPGA 系列的扩展,可支持1Tbps 系统的实现。Virtex UltraScale 系列具有

2017-11-18 04:15:03 1797

1797

在FPGA系统设计中,要达到性能最大化需要平衡具有混合性能效率的元器件,包括逻辑构造(fabric)、片上存储器、DSP 和I/O带宽。在本文中,我将向你解释怎样能在追求更高系统级性能的过程中受益于Xilinx® 的Virtex™-5 FPGA构建模块,特别是新的ExpressFabric™技术。

2018-07-22 09:30:00 1628

1628

多类指数损失函数逐步添加模型( SAMME)是一种多分类的AdaBoost算法,为进一步提升SAMME算法的性能,针对使用加权概率和伪损失对算法的影响进行研究,在此基础上提出了一种基于基分类器对样本

2017-12-01 16:50:47 1

1 AdaBoost是数据挖掘领域最常见的提升算法之一。对传统AdaBoost将各个基分类器线性相加所存在的不足进行分析,并针对AdaBoost各个弱分类器的加权方式提出新的改进,将传统的线性相加改为

2018-01-04 16:58:00 0

0 商汤科技算法平台团队和北京大学高能效实验室联合提出一种基于 FPGA 的快速Winograd算法,可以大幅降低算法复杂度,改善 FPGA 上的 CNN 性能。

2018-02-07 11:52:06 8687

8687

Xilinx 公司Virtex5 系列的FPGA 具有多重配置的特性,允许用户在不掉电重启的情况下,根据不同时刻的需求,可以从FLASH 中贮存的多个比特文件选择加载其中的一个,实现系统功能的变换。

2018-12-04 08:37:00 4654

4654

400G和500G应用。Virtex UltraScale VU095器件可为有线通信、测试测量、航空航天与军用以及数据中心等多种不同应用带来前所未有的高性能、系统集成度和带宽。此外,赛灵思还新增

2018-09-13 16:52:00 994

994 ICHEC讨论了FPGA对HPC应用的适用性,并重点介绍了能够利用特定FPGA上所有DSP的器件的最佳数据模式。

利用Xilinx Virtex-7 FPGA和Kintex KU115,ICHEC充分利用了re

2018-11-20 06:42:00 2425

2425 了解如何将复杂的SoC平台映射到单个Virtex®-7 2000T FPGA

2018-11-23 06:38:00 2515

2515 集成学习的Boosting算法通过结合多个弱学习器组成强学习器,AdaBoost算法是Boosting算法中的一种,本文详细的总结了AdaBoost算法。

2018-12-29 16:08:08 2866

2866

本文详细总结了AdaBoost算法的相关理论,本文详细推导了AdaBoost算法的参数求解过程以及讨论了模型的过拟合问题。

2019-01-07 18:26:07 3830

3830

Virtex-II ProTM平台FPGA产品基于高性能的Virtex-IITM结构,为嵌入式系统设计提供了一个极灵活的解决方案。利用Virtex-II ProTM器件,嵌入式系统设计人员可以在单片器件内集成范围广泛的硬和软IP核心,其中的硬件和固件具有可升级能力,从而可延长产品的在市场生存时间。

2019-04-13 10:07:17 1064

1064

和x32的数据带宽。x1的通道能实现单向312.5 MB/s(2.5 Gb/s)的传输速率。Xilinx公司的Virtex5系列FPGA芯片内嵌PCI-ExpressEndpoint Block硬核,为实现单片可配置PCI-Express总线解决方案提供了可能。

2020-01-19 16:52:00 787

787

本文档的主要内容详细介绍的是FPGA的硬件电路设计教程和FPGA平台资料简介包括了:FPGA技术概述;主流FPGA器件介绍;VIRTEX-5 FPGA电路设计;V4LX160 FPGA平台介绍;

2020-07-06 18:11:22 158

158 xilinx公司推出的两种新Virtex-4 FPGA器件LX60和SX35.LX60是逻辑最佳LX平台的第二个器件,SX35是DSP最佳SX平台的第一个器件.和今年六月份提供的Virtex-4 LX25一起,Xilinx公司现在可提供三种革命性的FPGA系列.

2020-09-10 08:47:00 1846

1846 链路预测是复杂网络的重要研究方向,当前的链路预测算法因可利用的网络信息有限,导致预测算法的精确度受限为了提高预测算法的性能,采用改进的 Adaboost算法进行链路预测。首先根据复杂网络样本建立

2021-04-08 11:21:28 15

15 入侵检测系统在大数据量的情况下误报率高、泛化能力弱,且单一机器学习算法不能较好地应对多种攻击类型。为此,设计一个基于支持向量机(SM)与 Adaboost算法的入侵检测系统。依托 Snort系统

2021-05-25 16:35:43 6

6

![]()

电子发烧友App

电子发烧友App

评论