目前大多数仪器采用封闭式FPGA(现场可编程门阵列)和固定的固件实现仪器的功能。如果你曾见过示波器的拆解,你也许见过里面的FPGA。FPGA可以增加测试仪器的处理能力,如果你曾使用过仪器的开放式FPGA,你就会知道可以将自定义的测试功能编程进仪器中。

仪器供应商早就了解FPGA的好处,并且一直在充分发挥FPGA独特的处理能力优势来丰富的功能,比如:仪器

● 能够在示波器上完成预触发捕获

● 能够利用信号处理功能在矢量信号分析仪上产生I和Q数据

● 能够在高速数字仪器上实时进行图案发生和矢量比较

测试设备制造商现在开始向用户开放FPGA以提供更多特殊应用的优化。为了帮助理解为何这是一个好的转变,下面列出了在测试应用中使用FPGA的一些关键特性:

● 确定性,实时处理

● 真正并行的执行

● 可重配置

● 低延时

更进一步讲,利用开放式FPGA可以实现哪些以前不能实现的功能呢?为了描述这些可能性,下面将介绍一些利用开放式FPGA的常见测试应用。

测试系统加速

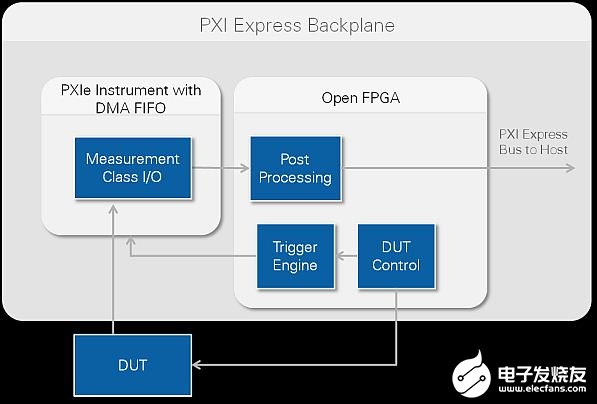

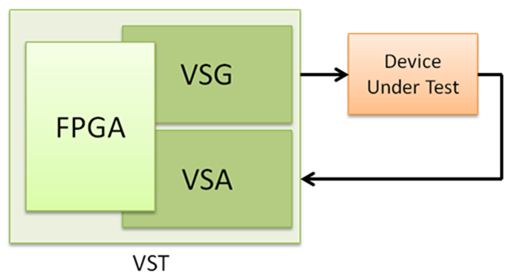

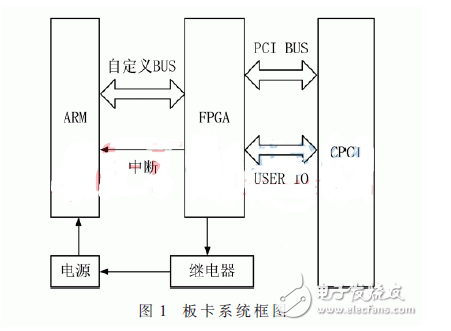

在大批量生产线的最终产品测试中,每一秒的测试时间都很宝贵。当产品测试速度与生产速度相匹配时,生产线的效率就是最高的。当两者速度不匹配时,就必须采用创新的技术来缩短测试时间。传统方法需要使用多台分开的台式仪器,它们通过以太网、USB或GPIB连接到一台PC主机。这种测试的速度相对较慢,因为待测设备的控制、测量以及通过数据总线的处理是分开进行的。另外一种方法是使用开放式FPGA来加速这个过程,如图1所示。

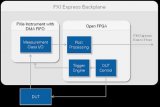

图1:在测试仪器中,开放式FPGA可以增加诸如触发和后处理等功能。

与使用外部通信总线不同,FPGA可以使用高速总线(如PXIe)连接仪器,并通过其配置端口(如I2C、SPI或另外的控制总线)连接待测设备(DUT)。这种应用中的FPGA可以控制待测设备,触发其它仪器开始捕获样本,甚至将这些样本处理成对主机来说有意义的结果。

低时延是加速这类应用的一个关键因素。FPGA没有操作系统,但所有的逻辑都是用硬件实现,并且这些硬件工作的时钟速率很高。这意味着响应只需花一个时钟周期捕获、一个时钟周期处理和一个时钟周期输出结果。当时钟速率为200MHz(时钟周期为4ns)时,完整的响应时间只需12ns。由于FPGA的确定性特点,12ns的响应时间不是只有一次,而是每次都是。因此FPGA不仅可以避免与使用主机有关的延时,而且能够最大限度地减小主机处理时的非确定性延时。

协议的处理

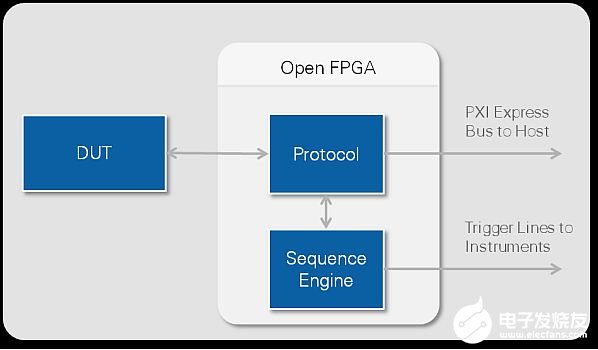

今天,并不是所有数字和MEMS设备都能用已知结果矢量进行测试。就拿脉冲密度麦克风(PDM)来说,如果给它一个激励信号,你不能期望每次测试得到的比特流是完全相同的,这是因为PDM是模拟设备。为了从这些类型的待测设备获得有意义的结果,在比较结果之前你首先需要用其特定的协议对数字流进行解码。借助开放式FPGA,你可以在FPGA上配置你的测试系统来实现PDM协议,不必再传至CPU进行解释。进一步拓展这个概念,今天你可以配置这个FPGA实现PDM协议,明天你又可以重新配置同样这个FPGA实现不同的协议,比如用于测试数字温度传感器、加速度计或MEMS设备的协议。

在图2中,协议不是在CPU上实现,而是在FPGA上实现。正因为此,测试系统现在自身就可以支持快速握手脚本,适应精确等待周期等协议行为,并根据通信内容做出决策。这种方法不仅能让你从待测设备接收更高层数据,比如在PDM麦克风场合中解码的模拟数据,而且允许你用更高层命令编写测试脚本。

图2:FPGA可以用来处理协议,知晓总线使用的协议内容。

闭环测试:功放

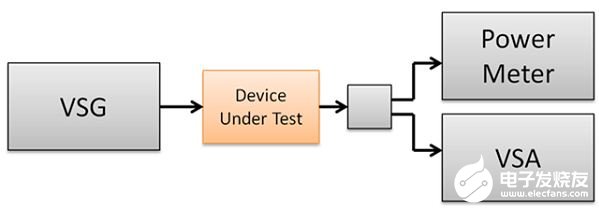

在无线通信系统中,信号在发往天线之前需要用功放IC增加信号的强度。功放的性能规格通常是在特定的输出功率电平点定义的。因此当功放工作在这个输出功率电平时对它们进行测试就显得非常重要。然而,功放的增益一般只是粗略的知道(比如±3dB),而且在器件工作范围内是非线性的。你越接近最大输出功率,增益就越低。基于这些理由,在开展任何性能测试之间你必须首先“调测”放大器的输出。调测输出经常被称为功率电平调整或功率伺服调整。基本原理是调整放大器的输入功率,直到你测得正确的输出功率。

测量功放的传统测试装置见图3所示。矢量信号发生器(VSG)产生一个激励波形给待测设备。功率计确保待测设备输出正确的功率电平。最后由矢量信号分析义(VSA)测量待测设备的性能——如误差矢量幅度(EVM)或相邻通道功率(ACP)。实际操作中需要针对各种中心频率和功率电平重复这些测量。

图3:用于测量功放输出的传统测试装置包含有矢量信号发生器、矢量信号分析仪和功率计。

必须针对每个想要测试的中心频率和功率电平调测功放的输出功率。调测过程一般遵循以下这些步骤:

● 根据估计的待测设备增益选取一个起始的矢量信号发生器功率电平

● 设置矢量信号发生器的功率电平

● 等待矢量信号发生器稳定工作

● 等待待测设备稳定工作

● 用功率计进行测量

如果功率在正确的范围内,退出。如果不在范围内,计算新的矢量信号发生器功率电平,回到步骤2重新开始

整个调测过程可能要花几百毫秒到几秒的时间,具体取决于待测设备类型、要求的精度以及使用的仪器。调测过程完成后就可以用矢量信号分析仪开展性能测量了。

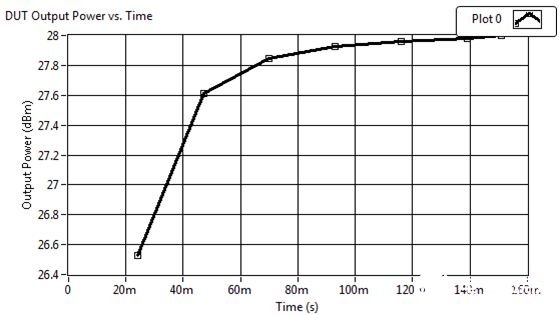

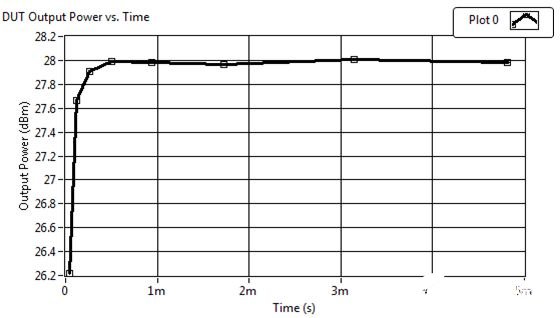

图4显示了使用传统方法将待测设备样品输出调整到平均输出功率为28dBm的过程。如果功率放大器的增益是线性的,并且符合数据手册中规定的典型增益,那么矢量信号发生器产生的第一个点就将产生28dBm的输出功率。然而放大器的实测输出功率只有26.5dBm,这就表明了功放典型增益指标的不精确性。随后调整矢量信号发生器的输出功率,由矢量信号分析仪捕获另外一个输出功率点。这次平均功率是27.6dBm,从中可以看出放大器增益响应的压缩过程。总之花了7步、大约150ms的时间才使放大器的输出达到想要的功率值。在这个例子中,待测设备的稳定时间是每步10ms。但不同待测设备的稳定时间是不同的,它将显著影响总的调测时间。

图4:传统的功放输出调测方法表明功率电平是渐次增加的。

矢量信号收发器(VST)是将矢量信号发生器、矢量信号分析仪和FPGA整合在一起的一种仪器。这种组合可以让你将功率调测算法转移到硬件中实现。即使没有图5中的功率计,你通常也可以执行系统校准步骤将功率计精度转嫁给矢量信号分析仪。

图5:矢量信号收发器将信号发生器、信号分析仪和FPGA整合在一起。

调测功放输出功率的步骤与传统方法是类似的,只不过调测环路在开放式FPGA中执行。在FPGA中执行环路可以显著缩短每次调整所需的时间。

通过使用开放式FPGA和硬件并在FPGA上实现控制环路,调测待测设备输出功率的时间将远远小于在主机电脑上执行控制环路的时间。对于本例中的待测设备来说,调测过程只用了5ms,而传统方法需要150ms。需要注意的是,基于硬件的方法所需的步骤数比传统方法多一步。但调测过程所需的总时间却明显减少。与图4相比,图6中的前几个步骤完成得很快(平均时间较短),然后点的间隔越来越大,因为调测环路正在收敛。

图6:使用基于硬件的调测方法后,功率电平上升的时间要短于传统方法。

信号处理

用户可编程FPGA最有用的应用之一是在仪器上减少必须传回主机进行后处理的数据量,从而释放通信总线用于其它数据传输,同时减少CPU的负担。用于这方面的常见方法包括复杂触发、滤波、峰值检测或对捕获的数据集执行快速傅里叶变换(FFT)。

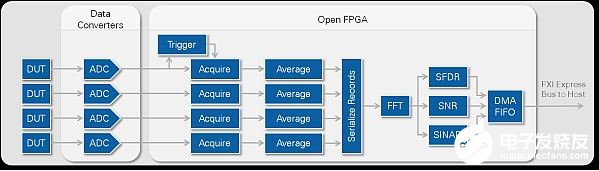

例如在图7中你可以看到有4个待测设备需要并行测试的应用。模数转换器(ADC)将样本传送给FPGA,但直到定制触发器启动捕获命令后数据才被捕获。在捕获数据时,FPGA会实时平均测量结果,然后将它们连续进行记录。然后在测量无杂散动态范围(SFDR)、信噪比(SNR)和信号噪声与失真比(SINAD)之前对记录进行快速傅里叶变换。这些结果只是来自ADC的的输入信号数据的一部分,接下来将通过直接存储器访问先入先出缓冲机制(DMA FIFO)上传给主机。

图7:开放式FPGA可以帮助你捕获数据、平均数据以消除噪声、将并行数据变为串行数据,然后执行数学、FFT和滤波器算法。

作为DSP中的一种基本功能,快速傅里叶变换被广泛用于许多测试应用。由FPGA实现这个功能可以为许多测试应用增添许多功能,比如频域触发器、数据精简、基于频率的闭环控制和图像处理等。图8显示了如何在上例中使用LabVIEW FPGA实现快速傅里叶变换。

图8:前述例子中的这个代码显示了快速傅里叶变换是在开放式FPGA的何处执行的。

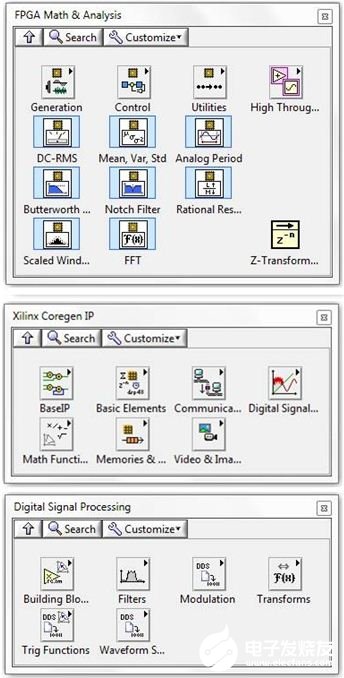

虽然本文只是提及了很少几个可以FPGA上实现的令人激动的数字信号处理功能,但实际上还有许多其它功能可以用来扩展FPGA在测试应用中可以实现的能力。这类处理功能可以在许多开放式FPGA上实现,图9显示了在国家仪器(NI)公司的硬件上可以通过LabVIEW FPGA实现的一些功能类型。

图9:在FPGA上可以实现的数字信号处理功能包括数学、滤波、三角函数和视频处理等。

随着开放式FPGA在整个测试与测量行业内逐渐流行起来,你将看到只有固定功能的仪器越来越少。相反,更多的仪器将变得可软件定义,与移动设备行业中引入“应用(app)”所经历的变革一样。测试应用不再受制于测试供应商开发的软件能力。它们将只受限于当时的硬件水平以及使用仪器的工程师的想像力。

责任编辑:gt

电子发烧友App

电子发烧友App

评论