老wu发现,很多硬件菌在设计PCB上的电源供应系统时,喜欢在各个电源轨之间加入磁珠隔离一下,据说能防止干扰。硬件菌们很喜欢加磁珠,貌似磁珠能包治百病,就好像我们觉得自己头疼、嗓子疼,感觉自己肯定是感冒了,就要马上嗑阿莫匹林抗生素一样,磁珠也被硬件菌给滥用了。

磁珠这玩意虽好,但也不能贪杯哟,硬件菌在决定服用磁珠之前,老wu建议先看看下这份 Altera 公司的铁氧体磁珠应用笔记。

这是一篇来自业界著名 FPGA 供应商 Altera 公司的FPGA 电源设计应用笔记,这份应用笔记提供了设计铁氧体磁珠滤波器网络来为Stratix® IV FPGA隔离共用电源轨的一些设计指南。

FPGA 技术的发展使数据速率提高到了 10 Gbps 以上。为了达到这种数据速率,FPGA 厂商一般要求提供多个隔离的数字和模拟电源层,以单独为 FPGA 的内核,I/O,敏感的锁相环 (PLL) 和千兆收发器模块供电。因此,电路板上电源分配系统的复杂性大大增加。

由于电路板空间、层数以及成本预算均有限,电路板设计人员发现在这些系统限制内设计其 FPGA 电路板越来越困难。对于 Stratix IV GX 和 GT 系列千兆位收发器 FPGA 系列,一种常用的简化电源设计的方法是,对于具有相同电压要求的部分,能够共用电源轨,并保持彼此之间的隔离,避免电源噪声干扰。常用的策略是使用铁氧体磁珠。

本应用手册介绍了如何正确选择磁珠以及一些设计方面的考虑,例如:anti-resonance、避免 LC 谐振效应、传输阻抗分析和直流IR压降最小化,同时还要满足去耦的目标阻抗要求。另外,还介绍了某些情况下使用 PCB 布局结构来替代铁氧体磁珠功能的秘技。PCB 结构与铁氧体磁珠的性能对比仿真结果,可用于评估验证 PCB 结构滤波器网络的效果,同时可以了解其诸多局限性。

铁氧体磁珠的选择

一般而言,铁氧体磁珠分为两类:

高Q值铁氧体磁珠——一般用作谐振器,不得用于电源隔离电路中

低Q值铁氧体磁珠——也称作吸收铁氧体磁珠,损耗较大,可构成较好的电源滤波器网络,因为设计它们的目的是吸收高频噪声电流并将其以热的形式散发掉。这种铁氧体磁珠在宽高频带下具有高阻抗,从而使其成为理想的低通噪声滤波器。

厂商一般会给出铁氧体磁珠的阻抗-频率曲线图的特性,并说明额定最大直流电流和直流电阻。这取决于铁氧体磁珠的设计和所用材料,阻抗曲线图中的幅度也在一个较宽的频谱范围急剧变化,从而对正确选择铁氧体磁珠带来麻烦。

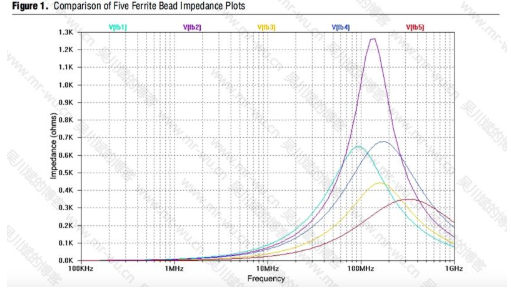

图 1 显示了 1 GHz 频率范围内 5 条交错在一起的铁氧体磁珠阻抗曲线的例子,旨在对比可用于电源噪声滤波的各种低Q值铁氧体磁珠的性能情况。

铁氧体磁珠建模与仿真

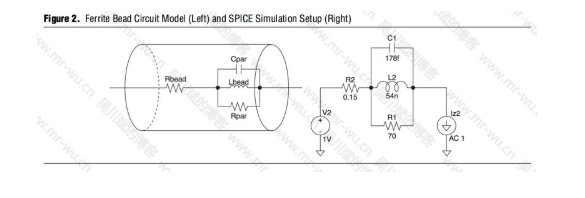

铁氧体磁珠厂商通常提供其器件的等效 SPICE 电路模型,以用于系统仿真。当无法从厂商那里获得铁氧体磁珠模型的情况下,可以将铁氧体磁珠建模成一个由 R、L和 C 元件组成的简单网络,如图 2 所示

尽管该模型为 first-order approximation,但是您仍然可以将其有效地用于 sub-GHz 的仿真。

Rbead 和 Lbead 为铁氧体磁珠的直流电阻和有效电感。

Cpar 和 Rpar 为铁氧体磁珠相关的并联电容和电阻。

低频条件下,Cpar 为开路,而 Lbead 为短路,从而只有 Rbead 作为铁氧体磁珠的直流电阻。随着的频率增加,Lbead 的阻抗开始随频率 (jωLbead) 线性上升,而 Cpar 的阻抗随频率 (1/jωCpar) 反比例下降。铁氧体磁珠的阻抗-频率曲线图的上升斜率主要由 Lbead 的电感决定。

从某个高频点开始,Cpar 的阻抗开始占主导,而铁氧体磁珠的阻抗开始下降,从而降低其电感效应。这种情况下,阻抗-频率曲线图的下降斜率主要由铁氧体磁珠的寄生电容 Cpar 决定。Rpar 有助于减缓铁氧体磁珠的 Q 因子。然而,过大的 Rpar 和 Cpar 值会增加铁氧体磁珠的 Q 因子,并降低其有效带宽。形成高Q铁氧体磁珠,导致电源分配网络 (PDN)上出现不期望的瞬态振铃响应。

要想观察这些参数对铁氧体磁珠频率响应产生的影响,您可以使用 SPICE 来仿真用于隔离的铁氧体磁珠的交流响应。图 2(右)显示了用于获取一个铁氧体磁珠样本的交流响应的 SPICE 电路设置, 其中DC电阻为 0.15Ω,有效电感为 54nH,并联电容和电阻分别为 178fF 和 70Ω。

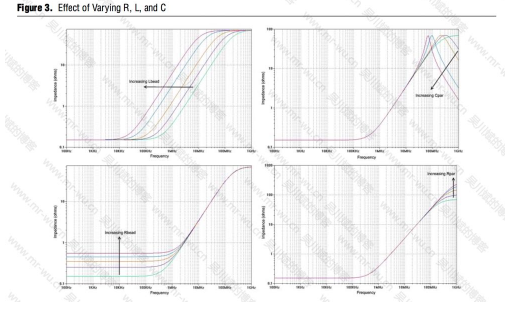

图 3 显示了 SPICE 中,施加一个 1V 电源和 1A AC电流负载,100 Hz 到 1 GHz范围内扫描的交流分析,得到的该铁氧体磁珠的特征阻抗-频率曲线图。在一些厂商没有提供 SPICE 模型的情况下,通过在模型中单独改变每一个 R、L 和 C 元件,可用曲线拟合方法来近似描述某个特定的铁氧体磁珠。

Stratix IV GX 设计实例

对许多应用而言,高速时钟、数据以及其它 I/O 开关速率可达到数百兆赫到几千兆赫。每一个开关信号相应的基本频率和谐波很容易污染敏感的电源层面,从而导致电压纹波和输出抖动增高,特别是在它们与其它噪声较大的数字电源层共用时。例如,在 Stratix IV GX 器件中,0.9V VCC核心电压被用于向 FPGA内核中的的数字逻辑单元 (LE)、存储器单元以及 DSP 模块等供电,这些模块有很大噪声。另一方面,0.9V VCCD_PLL 被用于向产生时钟倍频且对噪声更敏感的 PLL 供电。尽管在 PCB 上将 VCC 与 VCCD_PLL 电源层合并很简单(由单个电源稳压器供电),但是这样做会使内核耦合噪声对 PLL 性能产生负面影响。

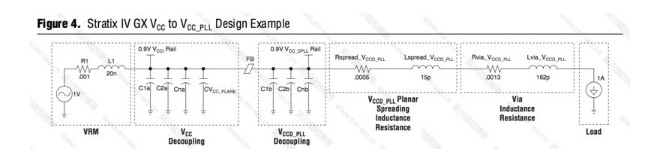

图 4 显示了 Stratix IV EP4SGX230KF40 器件的一个设计实例,其使用一个铁氧体磁珠隔离 VCC 和 VCCD_PLL。本例所选用的铁氧体磁珠为莱尔德科技 (Laird Technologies) 的 LI0805H121R-10。

VCC 电源层去耦(由 C1a 和 C2a 到 Can 表示)设计是通过 Altera 的 PowerPlay 早期功耗估算器 (EPE) 和 PDN 去耦工具实现从直流到25 MHz的频带内达到 9 mΩ 的阻抗目标。同样地,VCCD_PLL 去耦(由 C1b 和 C2b 到 Cnb 表示)的目的是,利用相同的目标阻抗方法在至少 70 MHz频带内达到 0.45Ω 目标阻抗。

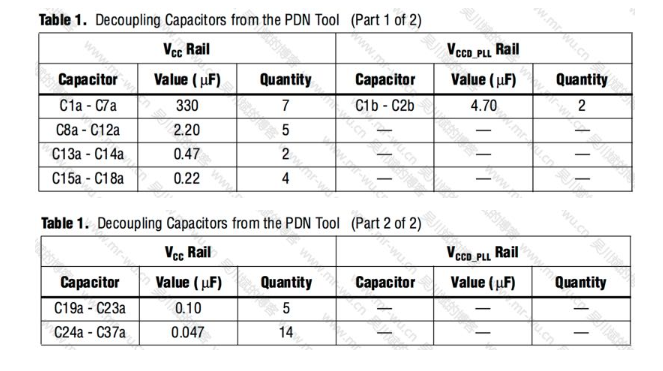

表 1 对通过PDN 去耦工具得出的每个电源层面要达到各自阻抗目标所需的去耦电容进行了总结。该 PDN 工具估算得到的平面扩展电阻和电感以及 BGA 过孔电阻和电感,也都包括在 SPICE 界面中,旨在给出一个扩展至器件 BGA 焊球的完整 PDN 状况。

反谐振 (Anti-Resonance)

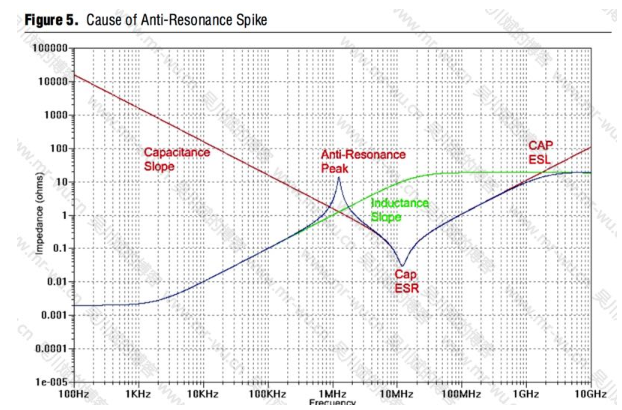

使用铁氧体磁珠时,注意可能出现的反谐振峰值,其可能会导致超出目标阻抗限制的阻抗曲线。下降的电容特性斜率与铁氧体磁珠的上升的电感特性斜率交错在一起时,便会出现这些反谐振峰值,如图 5 所示。

如果目标阻抗较低,这些峰值极易超出目标阻抗限制。使用 SPICE 或者类似的电路仿真器来确保这些反谐振峰值不会超出目标阻抗。

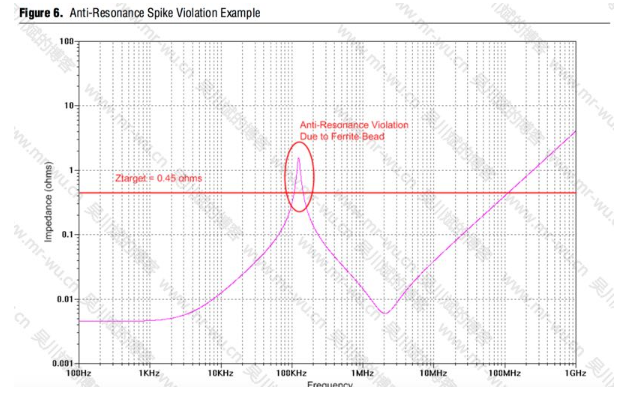

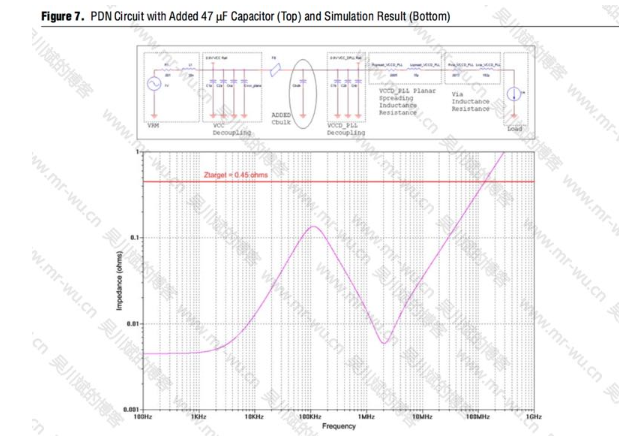

就上述 Stratix IV GX VCC 到 VCCD_PLL 隔离例的子而言,PDN 工具没有体现出铁氧体磁珠的效应。因此,SPICE 被用于验证使用铁氧体磁珠后是否会引入不期望的反谐振从而改变 PDN 特性曲线。

在SPICE中,将一个稳压器源建模成一个简单的电阻-电感串联网络,驱动一个 1A 的负载,并将其运用到建模的 PDN 电路上。在100Hz 到 1GHz频谱范围内做AC扫描来仿真该电路,以获得以 Ω 为单位的去耦网络阻抗曲线图。如图 6 所示,PDN 工具估算得到的 VCCD_PLL 电源的去耦电容器以及选用的莱尔德科技 LI0805H121R-10 铁氧体磁珠一起在124 KHz 处会引起一个约为 1.5Ω 的严重的反谐振峰值。因其超出了 0.45Ω 的 VCCD_PLL 阻抗目标,必须解决该问题。

要想消除这种低频反谐振峰值,可为 VCCD_PLL 增加一个大容值的Bulk去耦电容,如图 7(顶部)所示。图 7(底部)显示了为 VCCD_PLL 电源层增加一个 47μF 大电容后的 PDN 曲线图。该增加的Bulk去耦电容有助于减轻这种反谐振超标。

LC 谐振振荡

使用铁氧体磁珠的另一个问题是 LC 谐振振荡。只要您在 PDN 电路中使用电感和电容,存储于电感和电容中的能量就会在这两种能量存储元件之间来回转移,从而可能导致不需要的电路振荡。这种负面影响表现为在时域的电压过冲甚至电压振铃。

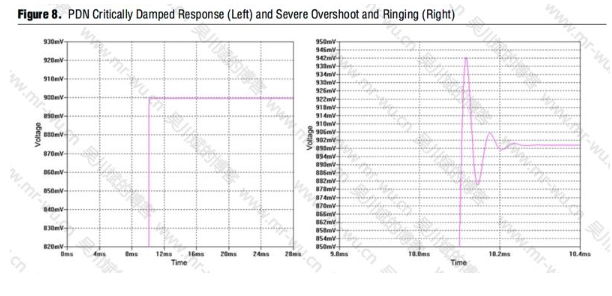

使用一个具有瞬态分析的 SPICE 仿真器或者类似工具,来对您的设计进行检查,看是否所有的过冲或振铃都得到了较好的抑制并且在容许限制范围内。前面的 Stratix IV GX VCC 到 VCCD_PLL 例子中,莱尔德科技的 LI0805H121R-10 铁氧体磁珠没有引起电压过冲或振铃,如图 8(左)所示。如果出现过冲或振铃,对于 0.9V VCCD_PLL 电源而言,请确保其在 ±30 mV 操作规范以内。通常情况下,如果铁氧体磁珠的电感非常高,如图 8(右)的假设情况所示,则过冲或振铃会更加严重,从而导致器件的失效或者错误运行。如果出现严重的过冲或振铃,请选择更低电感值的铁氧体磁珠。

传输阻抗

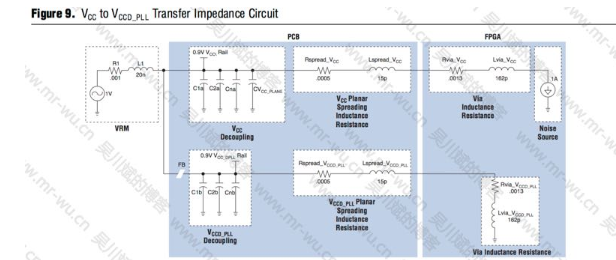

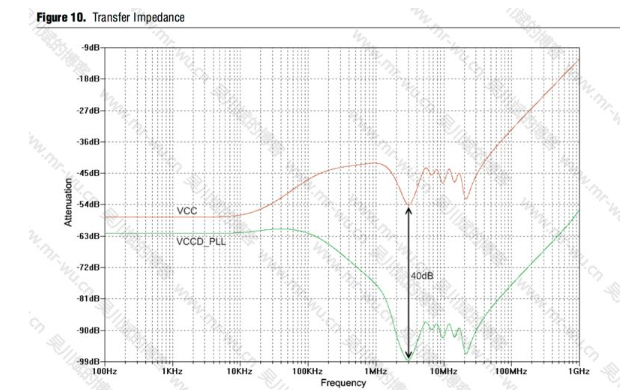

评估电路噪声抗扰度的一种常用方法是分析其传输阻抗。要确定上述例子 VCC 到 VCCD_PLL 隔离的传输阻抗,您可以从铁氧体磁珠的 VCC 端来仿真 PDN 电路,通过加上1A的电流源,以对 FPGA 器件中来自 VCC 电源的模拟噪声进行评估,如图 9 所示。

图 10 显示了VCC电源层铁氧体磁珠前和隔离的VCCD_PLL电源在FPGA 器件 BGA 球栅上的最终传输阻抗。由于铁氧体磁珠和 VCCD_PLL去耦网络的作用,在3 MHz以上频段上,VCCD_PLL 比 VCC 低大约 40 dB。

尽管该应用手册给出的例子均专门针对 VCCD_PLL 电源层面,但是 Stratix IV GX 和 GT 器件的其它一些电源,例如:VCCL_GXB 、VCCAUX 和 VCCA 等,也都可以受益于文中描述的相同隔离技术和分析方法。

DC 电流和 IR 压降考虑因素

铁氧体磁珠可通过的电流量由其产品说明书中规定的最大额定 DC 电流决定。超出该最大额定电流就会损坏铁氧体磁珠。但是,甚至低于该最大额定 DC 值的电流也会导致铁氧体磁珠极大地降低其效果,因为铁氧体磁珠的芯材可能会变得饱和。

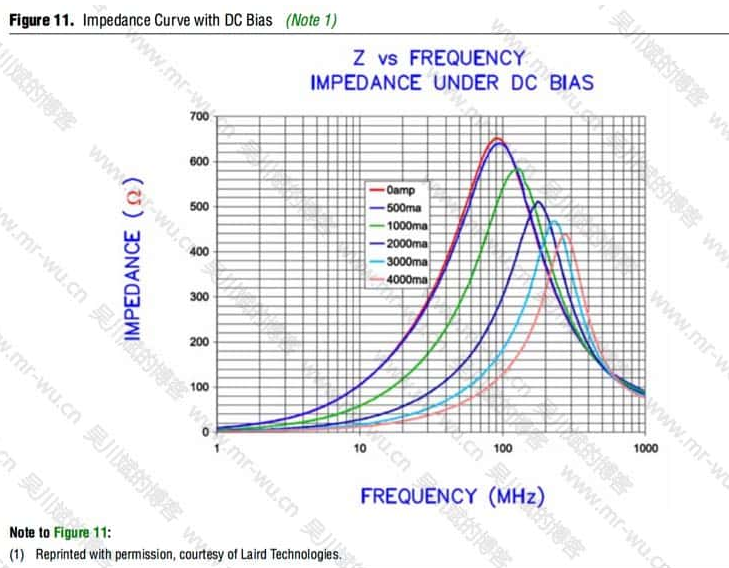

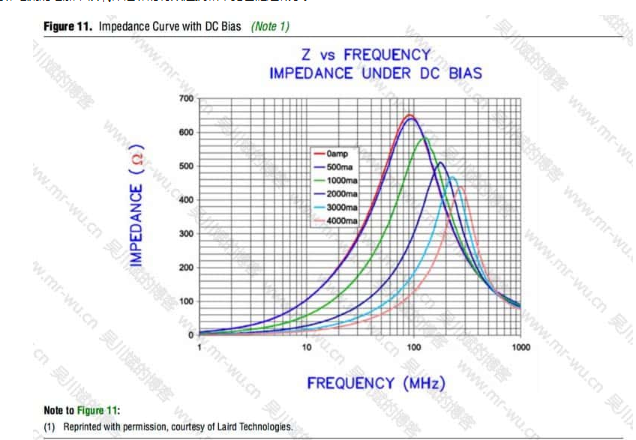

图 11 显示了改变 DC 电流偏置条件下铁氧体磁珠的阻抗-频率曲线例子。随着通过铁氧体磁珠电流的增加,铁氧体磁珠的有效阻抗和带宽也随之减小。

为了避免内核饱和与铁氧体磁珠性能下降,请选择额定 DC 电流两倍于目标电源所需电流的铁氧体磁珠。另外,选择一个低 DC 电阻铁氧体磁珠来使相关 DC IR 压降最小化。确定所有压降都不会使目标电源降至 FPGA 建议操作环境以下,具体规范见器件产品说明书。

PCB 结构

使用磁珠的另一种方法是构建一个小电感 PCB 布局结构,来连接两个隔离电源层。这种方法要求精确的建模并提取PCB 结构相关的 DC 电阻和 AC 环路电感,并利用 SPICE 仿真来检查结构滤波器性能,以代替铁氧体磁珠。DC 电阻决定了由于该结构走线长度带来的压降。AC 环路电感有助于提供两个互联电源层的隔离。

在下列例子中,Altera 使用 Ansoft Q3D Extraction 软件来建模、评估并调节几种 PCB 结构,其对隔离 Stratix IV GX VCC 和 VCCD_PLL 电源层面很有效。利用 Q3D,可抽取出每种结构的 DC 电阻和 AC 环路电感。之后,在 SPICE 中对这些值进行重新仿真,以获得与前面铁氧体磁珠性能相对比的结构性能。

例子1:直线走线结构

在图 12 所示直线走线结构中,一条 20 mil 宽、1 oz 铜厚的电源走线被用于代替铁氧体磁珠来连接考虑中的两个电源层。采用这种结构的走线可以承载约 3.7A 的电流。您必须设计走线,来处理期望的电流负载。直接影响走线电感的参数主要是走线的长度、距离参考层的高度,以及走线下方挖空 (cutout) 面积的大小。

一般而言,走线长度越长,走线离参考层越远,或者挖空面积越大,走线电感越大。因为这些因素会带来更大的电流回流面积。但是,每一个参数过大都会占用宝贵的电路板空间。更好的拓扑结构是使用一种盘绕走线方法。

示例 2:盘绕走线结构

为了尽可能增大走线环路电感同时最小化电路板空间使用,可使用一种盘绕走线结构,如图 13 所示。 因为绕组中的电流在绕组的并联走线部分总是以相同方向流动,因此没有电流抵消发生,并且在一个较小区域实现最大电感。但是,使用盘绕结构要求一个逃逸过孔(逃逸过孔这个名字比较奇怪,老wu不解释,看图你就会秒懂),以允许走线能够走到另一个层。正因如此,需考虑过孔的电流承载能力。一般而言,一个 1 mil 孔壁厚度、12 mil 直径的过孔可通过大约 2.5A 的电流。

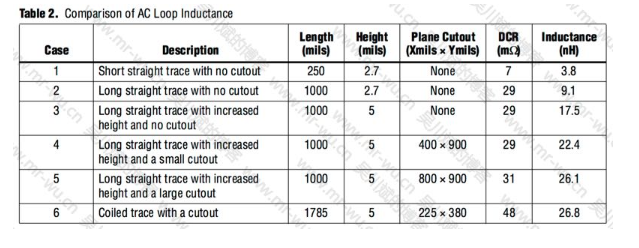

表 2 列举了通过 Q3D 得到的不同直线及盘绕走线长度、距参考层高度以及层挖空面积大小情况下对 DC 电阻和走线电感的影响。在给定走线宽度条件下,DC 电阻主要取决于走线的长度,如表 2 所示。

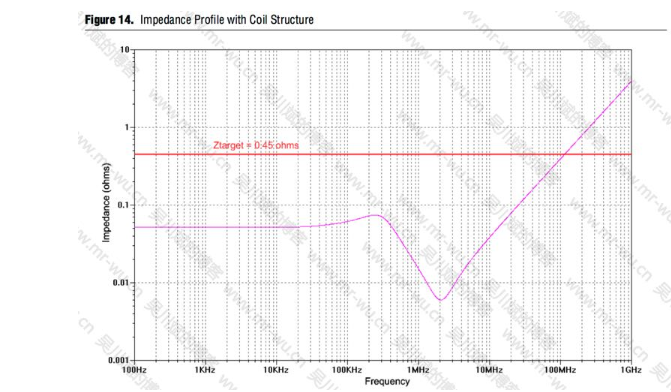

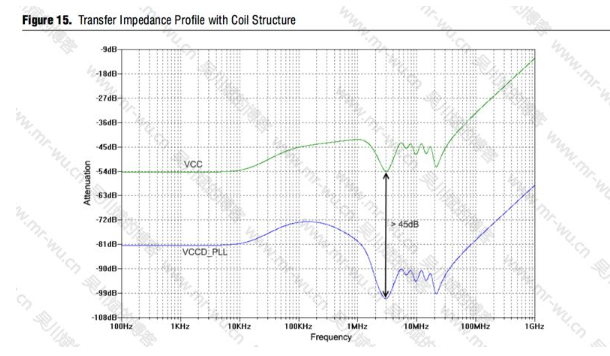

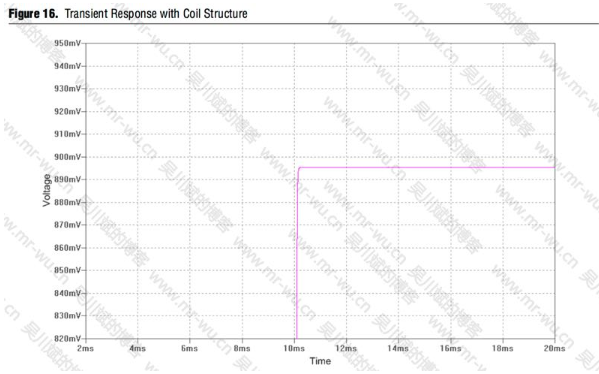

仿真结果

使用 Q3D 从盘绕走线结构提取的 48 mΩ DC 电阻和 26.8 nH AC 环路电感,并在前面 VCC 到 VCCD_PLL SPICE 例子中再次仿真这些值,可得到下列阻抗曲线(请参见图 14)、传输阻抗(请参见图 15)和瞬态响应(请参见图 16)的结果。这三幅图表明,如果结构的 DC 压降保持在产品说明书规定的建议器件操作环境范围内,则您可以使用盘绕走线PCB 布局结构来代替铁氧体磁珠。 (老wu注 一个磁珠多少钱,相应的通过绕线产生的等效于磁珠的走线的多层板pcb增加的成本多少钱?真的有人会用这种纠结的用法吗?除非你找不到同等规格的磁珠咯)

EMC 标准

但要注意的是,这种结构会成为强辐射源,其可能会影响联邦通信委员会 (EMC) 和其它国际监管机构颁布的电磁标准 (EMC) 规定。把这种结构放在两个地层之间,并用过孔联结在一起,可帮助屏蔽辐射。Altera 还没有对这些结构进行额外的 EMC 标准仿真和测试,其超出了本应用手册的范围。

设计建议

Altera 对您的设计提出如下建议:

选用一个铁氧体磁珠或设计 PCB 滤波结构,使其可以承载去耦电源所需的电流负载。

为了避免内核饱和,选择一个额定电流至少两倍于目标电源预计电流的铁氧体磁珠。

需最小化铁氧体磁珠或 PCB 结构的 DC 电阻,以减少 DC IR 压降

确定所有压降都没有导致目标电源低于器件的建议操作环境。

使用 SPICE 或其它类似工具,以确保所有铁氧体磁珠或 PCB 电感结构带来的反谐振峰值均没有超出目标阻抗限制。

如果出现反谐振超标,向电源层添加大的Bulk去耦电容来减少或消除峰值。

使用 SPICE 或其它类似工具对有过大电压过冲或振铃的 PDN 电路进行瞬态响应分析,这种过冲或振铃可能会超出器件建议操作环境。

使用 SPICE 或其它类似工具对被隔离的电源相对于未滤波的父电源层的传输阻抗进行分析,以获得充分衰减。

结论

Stratix IV GX 和 GT 系列高性能 FPGA 要求多个电源为器件内各种电路模块供电。为了让器件达到最大额定性能并具有最低抖动,某些敏感电源层要求非常洁净的电源。要在系统设计限制范围内满足这些电源要求,您可以将铁氧体磁珠或自定义 PCB 结构用作滤波器元件来隔离一些共用电源。本应用手册介绍了如何选择正确的铁氧体磁珠以及如何设计 PCB 结构,来满足基于 Stratix IV GX 及 GT 的 PDN 设计的一些电源滤波器要求。

电子发烧友App

电子发烧友App

评论