作者:侯超;郑悦;姚惟琳;王涛

引言

自“天链一号”中继卫星成功发射后,可为对地观测实时转发遥测、遥感数据,极大提高了各类卫星的使用效益和应急能力。之后的众多卫星都开始增加数传中继终端设备以通过中继卫星实现数据实时下传。数传中继天线作为卫星有效载荷终端,在伺服控制下驱动二维天线机构在一定角度范围内绕卫星X、Y轴转动,完成对目标的捕获跟踪。

由于整星对中继天线在指向精度、速度稳定度、可靠性以及寿命等方面的要求,中继天线机构驱动控制器一般为特殊定制产品[1],其功能、性能的表现直接影响到整星任务执行。随着整星任务多元化及运载能力限制,卫星所承载荷的种类、数量致使有效终端的重量尺寸成为考核机构驱动控制器设计的又一指标。

目前在轨中继天线机构驱动控制器多采用“MCU+FPGA”的控制架构,MCU负责通信和控制参数的分配,FPGA负责信号采集和电机驱动。基于航天器安全可靠性考虑,针对此架构,要单独为MCU设计看门狗电路以防止程序跑飞,另外,MCU航天多采用80C32单片机,受其运算速度、可用接口数量、数据总线宽度、顺序执行以及内部无ROM存储空间的种种约束,致使该驱动控制器硬件设计繁琐拖沓,而且7.2万门的反熔丝FPGA资源利用率又不超过50%,资源利用不充分。本文研究的目的是使用单片7.2万门反熔丝FPGA实现串口指令控制二维数传中继天线步进电机的细分驱动,并且在功能、性能、安全可靠性上完全覆盖并优于传统设计。

1 系统架构

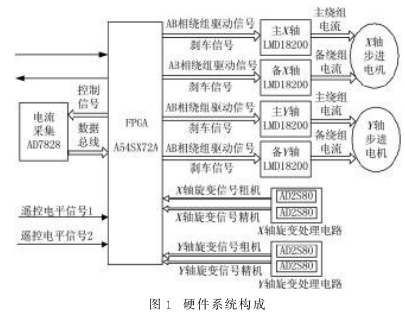

如图1所示,硬件系统采用一片FPGA作为核心控制器件,AD7828用于电机A/B绕组电流采集、主备控制线路各两片LMD18200芯片用于X/Y维步进电机驱动、4片AD2S80芯片用于两维旋转变压器角度信号解码,由FPGA实现串口通信。

考虑到航天型号可靠性要求,FPGA选用7.2万门Actel公司具有抗单粒子翻转的反熔丝器件A54SX72A-CQ208B,步进电机选用双绕组两相/四拍步进电机,主备两套驱动线路互为热备份,当一路驱动线路故障时可以通过遥控指令使FPGA切换至另一路驱动线路。为防止双绕组电机在主绕组工作时,电机备绕组与备份驱动线路存在电流回路形成感应电流,导致电机转动时产生抖动,所以FPGA在使用主份驱动线路时,及时向备驱动线路的LMD18200输出刹车信号。

在中继执行对接任务时,要求二维天线的角位置分辨率为0.005 5°,所以选择双通道旋转变压器加专用RDC芯片解码电路进行角度位置高精度转换[2]。在本文中对每轴机构双通道旋变输出的正余弦信号分别采用2片AD2S80芯片进行粗、精通道RDC转换,FPGA采集并进行粗、精通道数据组合纠错后最终获得当前机构角度位置。

2 FPGA设计结构

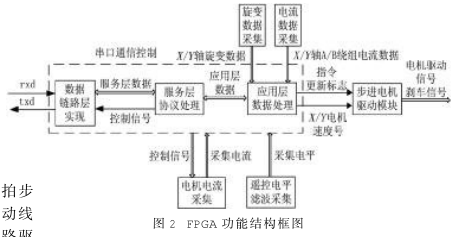

FPGA由电平采集电路、旋变数据处理电路、电机驱动电路、异步串口通信电路、AD转换控制电路组成,见图2。其中串口通信功能作为整个FPGA控制流程的发起,电机驱动则作为功能流程的最终实现。

采集模块实现两路电平遥控信号的采集和数字滤波,其结果输出给串口通信控制模块,由该模块收集并参与控制。

旋变数据采集模块主要实现二维机构双通道旋变数据的采集和耦合,由串口通信模块发起角度采集请求,本模块实现角度采集。

电流数据采集模块实现X/Y轴步进电机A/B相绕组电流的采集,通过FPGA控制切换采集通道并发起AD转换,并根据AD时序获得当前绕组电流数据,由串口通信模块发起采集请求和收集采集电流数据。

电机电流采集实现两台步进电机主备各8路绕组电流的AD转换和采集,由串口通信模块发起电流采集请求,本模块实现AD转换和采集控制。

串口通信控制模块主要实现解串/串行器,服务层拆/组帧及校验,应用层数据判别/填充、采集模块数据调度等功能。将指令中的速度挡与采集模块收集的信息(位置、主备绕组切换、使能开关等信号)进行比较,最终获得电机的执行速度号,输出给电机驱动模块。

步进电机驱动模块输入为电机驱动的速度挡(含指令要求电机转动方向),FPGA按照256细分正弦PWM斩波方式驱动两相/四拍步进电机转动。

本文重点介绍旋变数据处理、串口通信控制处理以及电机驱动功能的实现,采集滤波功能、AD转换采集较为成熟,这里不作介绍。

2.1 旋变数据处理

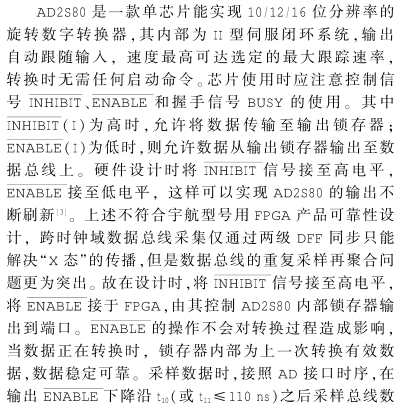

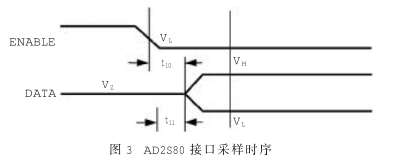

据,此数据稳定。

中继天线两维机构均采用双通道多级旋转变压器,粗、精机极对数比为1:N。粗通道执行0~360°的粗测量,精通道则执行0°~(360°/N)范围内的精测量,双通道输出数据实际上是将粗通道角度数据与精通道角度数据进行拼接获得[3]。

粗通道AD2S80选取数据位数n是按照极对数N来确定的,一般参照式(1)选择:

通过这种方法选取的高n位粗通道数据比精通道AD2S80转换输出的数据权值高,在n之后的粗通道数据与精通道数据权值相同。精通道AD2S80选取位数一般是和分辨率要求有关。

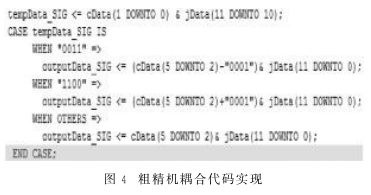

在粗、精组合中,由于粗、精机械轴之间齿轮间隙产生的传动误差、两个旋转变压器安装不同心等工艺因素、电气零位误差以及RDC转换误差,使得粗、精在直接组合时存在模糊区间,该模糊区间发生在选取的粗通道读数存在多“1”或少“1”的情况[2],所以在直接输出双通道数据之前先要通过精通道来校准粗通道。纠错时,将精通道高两位jData与粗通道权值相同的两位cData进行比较,比较结果用于修改粗通道中权值比精通道权值高的数据,对其进行加“1”、减“1”或无操作[4]。代码实现方法见图4。

将纠错后的粗通道数据与精通道数据进行拼接输出即为双通道旋转变压器转换后的角度位置数据,此角度位置数据为当前机构的绝对角位置。

在实际使用中,二维机构安装会引起机械零位和电气零位偏差,即机构处于零位时,通过旋变输出的电气角度不为零,此时需要FPGA对获得的绝对角度位置进行零位偏差修正,从而获得当前机构的相对角度位置,输出给串口通信控制模块,用于当前指令状态参数反馈以及对电机是否过界的判断。

2.2 FPGA异步串口通信功能

串口通信控制模块实现两部分功能:一是实现异步串口指令接收和发送,二是向电机控制模块输出电机控制参数。

FPGA实现串口接收状态机,实时采样串口接收总线rxd,当接收到起始位(低电平有效)时,对起始位电平宽度计数,当满足波特率要求时,则认为起始位正确。状态机跳转到接收数据状态,对每一位均进行宽度校准,在符合波特率定时条件下,对每一位数据进行三次采样,进行三取二获得当前采样真实数据,并按照字节排序进行移位获得字节数据。对采样位数计数,当满足协议要求的一次串行传输数据位数要求时,状态机则跳转到接收校验位状态。相同于数据区采样,对校验位也进行三次采样二次求同获得校验位数据,并在下一时钟将数据位与接收到的校验位进行比对,获得校验正确标志,此时状态机跳转到接收停止位状态。对停止位宽进行判断,获得停止位正确标志,状态机设置为IDLE。当停止位正确标志有效且校验正确标志有效时,此时才能将一次串行传输数据存放到FPGA内部的字节接收缓冲区。图5为综合后字节接收状态机。按照通信协议要求,对接收的字节按照帧格式拆帧、判断合法性后方可获得当前串口指令数据,执行指令内容,并按照要求反馈状态信息。

通过对串口指令的解析,获得指令要求的电机速度号,FPGA内部实现一个113挡速度号对应的电机细分定时寄存器、占空比、转向信号和停转标志的表,将查找结果输出给电机驱动模块。这里的细分定时寄存器的值为对应速度下步进电机运行一个脉冲周期(4步)进行256细分,每一个细分Δt的FPGA晶振周期计数值。

例如FPGA晶振为24 MHz,电机速度为100°/s下的细分定时寄存器n的计算方法:步进电机为两相四拍电机,步距角为1.8°,则电机速度为100 °/s时的一个脉冲周期为1.8°×4/100=0.072 s,则一个脉冲周期需要FPGA晶振计数为N=0.072/FPGA晶振周期=1 728 000,那么一个细分Δt对应的细分定时寄存器的值n=N/细分数=1 728 000/256=6 750。

2.3 电机驱动功能

电机驱动采用LMD18200-2D芯片,内部包含2个独立背对背的H桥电路,可用于一台两相四拍步进电机A/B相绕组的驱动使用。LMD18200芯片提供双极性驱动方式和单极性驱动方式,相较于双极性的功率损耗大、电流波动大以及在设计时必须添加死区防止开关管直通的问题,本设计采用单极性驱动方式:FPGA输出的极性信号决定电机AB绕组的换向(电机转向),极性信号的周期决定电机转动的速度,输出PWM信号的占空比决定电机的力矩。为保证天线机构稳定驱动,FPGA采用256细分正弦PWM斩波输出方式。

根据串口通信模块输出的电机驱动控制参数,即细分定时寄存器、占空比、转向信号以及停转标志,在电机驱动模块中实现:在每个细分时间Δt(细分定时寄存器的值)内,对应细分点的面积与该细分时间内多个PWM脉冲导通面积之和一致即为实现方式。

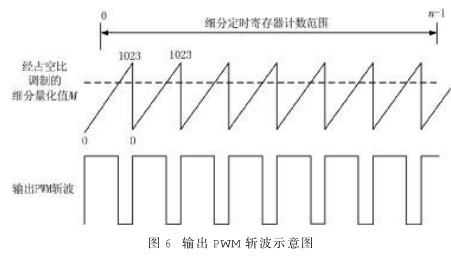

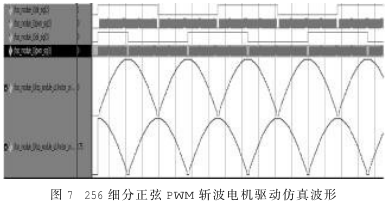

具体为:FPGA内部维护两张256×8 bit的正/余弦细分表,具体数值为正/余弦量化值。FPGA根据24 MHz晶振分频获得24 kHz的非对称三角波信号,通过在每个细分定时寄存器的计数范围内,与具体细分点量化值(通过占空比调制)进行比较,当调制值大于三角波对应时刻的计数值时,则输出PWM斩波为导通,否则关断。图6为输出PWM斩波示意图。图7为仿真实现波形。

3 试验结果

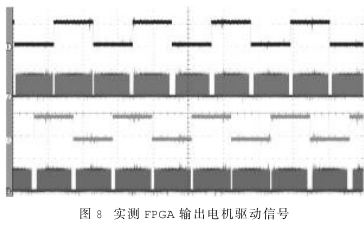

本设计采用Actel公司反熔丝FPGA,工作频率为24 MHz,开发环境为LiberoIDE,仿真软件为Modelsim。整个设计逻辑资源使用为79.90%,实现最高频率为39.607 MHz。布局布线后,将配置文件固化到目标器件中,并连接二维数传天线进行驱动指向控制测试,控制系统功能、性能指标均满足要求。图8为实测FPGA输出电机驱动信号。通道1为A相极性信号,通道2为A相PWM斩波信号,通道3为B相极性信号,通道4为B相PWM斩波信号。经过LMD18200功率放大后,输出到电机绕组上,电机逆时针转。

4 结论

本设计将串行器/解串器、通信协议处理、AD转换控制电路、旋变采集电路以及步进电机斩波控制电路集成到FPGA内部,具备二维天线各113挡速度驱动,对步进电机实现高达256微步的细分,提高天线运行平稳度,指向精度优于1.2′。使用的反熔丝FPGA芯片,一经固化,上电复位后直接运行,不需要对其进行看门狗监控以及设置软件陷阱,同时可抗空间单粒子效应,本设计已在某空间飞行器伺服控制系统中得到应用,目前在轨工作正常。另一方面,使用单片FPGA取代传统“MCU+FPGA”机构,最大化利用FPGA器件资源,提高产品集成度,减少单机体积,使驱动控制电路简化约50%,有利于航天器产品小型化设计。

责任编辑:gt

电子发烧友App

电子发烧友App

评论