,是近年信道编码领域的研究热点,目前已广泛应用于深空通信、光纤通信、卫星数字视频和音频广播等领域。LDPC码已成为第四代通信系统(4G)强有力的竞争者,而基于LDPC码的编码方案已经被下一代卫星数字视频广播标准DVB-S2采纳。

2020-03-03 10:30:27 1404

1404

的灵活性和较低的差错误码特性,可实现并行操作,译码复杂度低,适合硬件实现,吞吐量大,极具高速译码的潜力,在码长较长的情况下,仍然可以有效译码。 目前常用的信道编码体制有BCH码、RS码、卷积码、Turbo码和LDPC码等。其中BCH码和RS码都属于线性分组码的范畴

2020-11-02 13:56:16 39198

39198

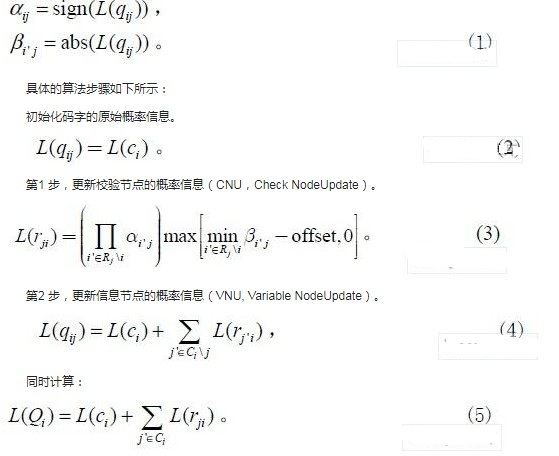

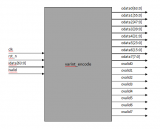

800Mbps准循环LDPC码编码器的FPGA实现引言低密度校验码肠 ,码 由于其接近香农限的纠错性能,使得其成为当前信道编码的研究热点。 码面临的一个关键问题是其较高的编码复杂度和编码时延。 形耐

2012-08-11 11:44:45

,用FPGA实现VGA接口协议可在显示器上显示文字、图型等;★PS/2鼠标,键盘接口:标准鼠标,键盘接口,提供的例程用VHDL实现在数码管上同时显示键盘扫描码和ASCII码,也可结合SOPC编程使其显示

2009-10-23 15:15:24

:配备:★RS-232串口:用于与计算机的数据通信;★VGA接口:直接VGA与显示器对接,用FPGA实现VGA接口协议可在显示器上显示文字、图型等;★PS/2鼠标,键盘接口:标准鼠标,键盘接口,提供

2009-11-02 18:55:54

EP2S60F484I4N特价 EP2S60F484I4N货期EP2S60F484I4N 价格EP2S60F484I4N国宇航芯特价订货EP2S60F484C4N国宇航芯特价订货

2020-01-06 09:07:44

本帖最后由 eehome 于 2013-1-5 09:53 编辑

鑫锐科技长期从事CPLD解密研究,经众多芯片解密成功案例验证,可为广大需求客户提供EP610PC快速、准确、有效的解密服务

2012-09-29 12:55:26

的设计技巧,分析和验证设计实例,综合各种设计手段、分析方法、优化和验证方法;基本实验I2C的设计与测试RSIC-CPU的设计与测试LDPC编码器设计M序列设计高级加密标准AES设计PS2键鼠接口设计与实现异步fifo的设计与实现

2012-09-13 20:07:24

论坛里面的大神们,有没有已经完成LDPC码编译码算法的FPGA实现,本人目前在做这方面的项目,时间比较紧,紧急求购IP核。。

2012-04-16 23:43:28

LDPC码入门资料!

2013-09-21 13:20:43

最近,需要使用fpga实现iec-61850-9-2报文编码,设计中涉及到的 字段非常多,以至于逻辑特别复杂,占用资源太多,设计的频率上不去。有没有哪位同道做过fpga报文编码类的设计,请不吝赐教。

2013-11-12 23:20:19

如题,Altera的FPGA芯片EP2C8Q208开发板没驱动,u***驱动不了,怎么办呀,求助

2013-10-28 12:18:14

编码调制终端设备中广泛应用作接口码型,在速率低于8 448 Kb/s的光纤数字传输系统中也被建议作为线路传输码型。 本文针对光纤通信传输码型的要求和CMI码的编码原理,介绍了一种以EPM系列7064

2010-08-09 18:24:16

的要求和FPGA芯片设计的灵活性结合起来,采用Alter公司的CycloneⅡ系列FPGA芯片EP2C35F672C8,用VHDL语言编程,最后分别使用Quartus Ⅱ和Matlab软件开发工具验证实现

2010-05-28 13:38:38

HDB3码型变换实验 一、实验目的1、了解二进制单极性码变换为HDB3码的编码规则,掌握它的工作原理和实现方法。2、通过调测电路,熟悉并掌握调测电路的一般规律与方法,学会分析电路

2009-10-11 09:00:20

:Broacast Services:内置BCH编码、LDPC编码、比特交织、星座映射及基带成型滤波支持所有DVB-S2定义的编码率:1/4, 1/3, 1/2, 2/5, 3/5, 2/3, 3/4, 4/5

2011-08-08 17:34:13

STC15F2K60S2的PWM怎么实现?基于STC15F2K60S2的智能循迹小车硬件电机控制代码分享

2021-09-24 07:11:46

的 MSB 位开始处理,K_BCH 位结束(K_BCH为定义的数据输入长度)。扰码序列的生成多项式为1+X14+X15,初始序列为100101010000000,扰码实现结构如下:2.matlab代码

2019-12-18 09:37:35

请教各位大仙,sof和jic文件烧录均正常,pof烧录失败,sof烧录后可正常工作,但jic烧录后无法正常工作,好像没有任何数据输出,这是为什么啊?fpga为EP2S60,配置芯片为epcs64,配置芯片也更换了,问题依旧。

2017-10-14 15:43:00

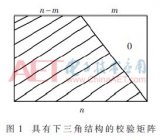

.基于该结构,本文实现了符合中国数字电视地面传输标准DTMB中LDPC译码器,在SMIC0.18um标准COMS工艺下,芯片面积约为8mm2;在时钟频率50MHz,迭代次数15次,8比特量化的条件下,吞吐率

2010-04-24 09:26:56

型。在高次脉冲编码调制终端设备中广泛使用CMI码作为接口码型,在速率低于8448kb/s的光纤数字传输系统中也被建议作为线路传输码型。

2019-08-29 06:41:21

基于FPGA的交织编码技术研究及实现中文期刊文章作 者:杨鸿勋 张林作者机构:[1]贵州航天电子科技有限公司,贵州贵阳550009出 版 物:《科技资讯》 (科技资讯)年 卷 期:2017年 第

2018-05-11 14:09:54

帧率提升、彩色空间转换等处理。FPGA器件具有可重复编程的灵活性以及并行处理能力,并且随着微处理器、专用硬件单元、DSP算法以及IP核的嵌入使其功能越来越强大。本系统的设计是基于Altera公司的EP2S60系列的开发板,板上集成两片SDRAM存储芯片、视频输入接口和VGA输出接口。

2019-09-29 08:46:06

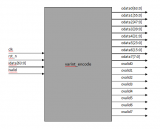

编码器实现指标分析LDPC码编码器实现编码器方案验证与优缺点分析

2021-04-30 06:08:10

本设计方案采用了一种改进的快速中值滤波算法,成功地在Altera公司的高性能Stratix II EP2S60上实现整个数字红外图像滤波,在保证实时性的同时,使得硬件体积大为缩减,大大降低了成本

2021-04-23 06:00:55

使用TMS320C6455芯片,FPGA采用ALTERA的高端FPGA芯片Stratix II EP2S系列EP2S60,板卡使用FPGA用于获取双通道数据采集,实现1路的Base CameraLink

2012-07-06 16:17:50

ALTERA的高端FPGA芯片Stratix II EP2S系列EP2S60,板卡使用FPGA用于获取双通道数据采集,实现1路的Base CameraLink输入,一路Base CameraLink

2012-06-13 11:39:49

ALTERA的高端FPGA芯片Stratix II EP2S系列EP2S60,板卡使用FPGA用于获取双通道数据采集,实现1路的Base CameraLink输入,一路Base CameraLink

2012-06-13 12:01:23

依据二分图构造LDPC码的算法矩阵及性能解析,看不出必然

2021-06-22 06:52:08

LDPC码是近年来发展较快且日趋成熟的一种信道编码方案,因其具有的优越性能和实用价值而被人们认知,但由于随机结构的LDPC码编译码器硬件实现较为复杂,具有的准循环特性QC_LDPC码已成为IEEE802.11n(WiFi)、IEEE802.16e(WiMAX)、(DVB—S2)等众多标准的信道编码方案。

2019-09-30 07:19:45

怎样去描述速率适配算法?如何快速实现FPGA的速率匹配?

2021-04-08 07:01:15

如何去实现一种基于stc15f2k60s2芯片的流水灯编程呢?

2021-10-25 06:48:41

本文介绍一种基于FPGA并执行IRIG-B标准的AC/DC编码技术,与基于MCU或者DSP和数字逻辑电路实现的编码方法相比,该技术可以大大降低系统的设计难度,降低成本,提高B码的精确性和系统灵活性。

2021-04-29 06:56:12

我使用68013A的16位从FIFO与FPGA通信。我通过68013A在PC和FPGA之间有两个连续的数据流。EP2被配置为四个缓冲的大容量,并且EP6被配置为等量缓冲的IN。为了共享FIFO的数据

2019-03-27 07:32:47

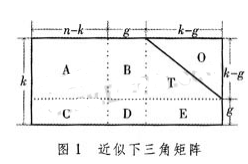

到了较多应用。中国移动多媒体广播(CMMB)中使用的就是LDPC纠错编码。在CMMB标准中,LDPC码长为9216,可支持1/2和3/4两种码率。作者通过深入分析CMMB中LDPC码校验矩阵的特点,采用

2019-08-23 07:22:50

FPGA芯片Stratix II EP2S系列EP2S60,板卡使用FPGA用于获取双通道数据采集,实现1路的Base CameraLink输入,一路Base CameraLink输出,2路Rs232

2012-06-18 11:39:48

标准中LDPC码的构造、编码及解码算法原理,结合MAT-LAB仿真对其算法有效性进行了分析比较。【关键词】:数字电视传输系统;;低密度奇偶校验码;;DMB-TH;;编译码器【DOI】:CNKI:SUN

2010-04-23 11:36:52

无线遥控器 常用的编码方式有两种类型,即固定码与滚动码两种,滚动码是固定码的升级换代产品,目前凡有保密性要求的场合,都使用滚动编码方式。下面简单介绍无线遥控器采用滚动码编码方式的优点: 1、保密型

2015-04-04 09:45:10

的动态 1 1.3 本文内容安排 2 2 CMI码编码译码原理 3 2.1 传输码应满足的基本要求 3 2.2 数字基带信号的码型设计原则 3 2.3 CMI码编码原理 4

2009-03-25 13:19:20

求EP2S60F672详细资料哪位大侠有啊,给我发一个

2009-08-11 22:14:25

LDPC码的通用编码方法有哪些?准循环LDPC码的快速编码方法是什么?

2021-04-25 07:16:26

Turbo码编码器的FPGA实现Turbo码译码器的FPGA实现Turbo码编译码器的性能有哪些?

2021-05-07 06:06:23

IJF编码是什么原理?如何实现IJF编码?采用FPGA和集成器件来实现IJF编码

2021-04-13 06:56:04

本文在SvstemGenerator中对LDPC码整个编译码系统进行了参数化的硬件实现,并构建了超宽带通信系统LDPC码硬件仿真平台,验证了LDPC码在UWB通信中的优异性能。

2021-06-03 07:01:58

出A、B信号的上升沿和下降沿。输入信号与其延时信号异或后,就可得到倍频信号。2 接口电路的FPGA总体方案及设计实现光电编码器的可靠性与精度直接决定了控制系统的可靠性与控制精度。控制系统精度不会高于

2019-06-10 05:00:08

800Mbps准循环LDPC码编码器的FPGA实现CCSDS星载图像压缩模块的FPGA设计与实现FPGA和Nios_软核的语音识别系统的研究RC4加密算法的FPGA设计与实现多FPGA系统中自定义

2012-02-02 17:26:14

最近想用音频编码解码芯片实现快速傅里叶变换的功能,选了一款芯片AD1701用mini开发板。但是FFT功能能不能实现这个问题?现在一直没有找到,也没有看到更多的其它算法,有没有大神给解答一下?

2018-12-20 09:19:48

基FPGA Cyclone II_EP2C5 EP2C8的频率计

基FPGA_Cyclone_II_EP2C5/EP2C8的频率计

功能描述:按4*4键盘上的1,2,3...号按键可依次测出 25000000Hz ,12500000Hz ....的分

2008-11-30 12:17:01 87

87 本文基于Altera的FPGA(StatixⅡ-EP2S30F484C3)架构,实现了码率为1/2,帧长为1008bits的规则(3,6)LDPC码译码器。所采用的最小-和算法相对于传统的和-积算法在不损失译码性能的前提下,

2009-06-06 14:12:20 31

31 LDPC原理与应用的主要内容:

第一章 绪论第二章 信道编码基础第三章 LDPC码概述第四章 LDPC码译码第五章 结构LDPC码的编码构造第六章 各种编码方法设计的LDPC码

2009-07-24 15:07:06 0

0 斑梨电子FPGA CycloneII EP2C5T144 学习板 开发板产品参数1. 采用ALTERA公司的CyclonellEP2C5T144芯片作为核心最小系统,将FPGA

2023-02-03 15:14:29

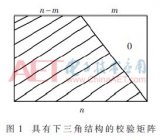

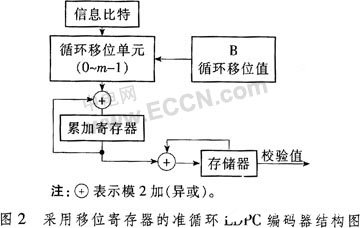

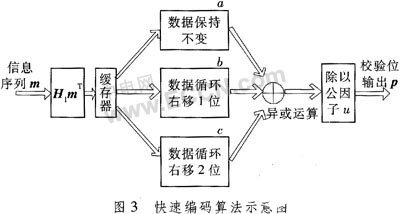

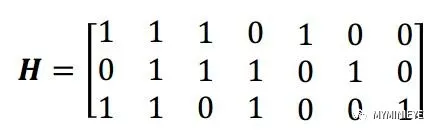

简述了LDPC码的研究现状及编码方法。在此基础上分析了目前常用的编码实现方式,并针对一类准循环LDPC码的特点,提出一种更简洁的快速编码算法及设计实现思路。

2009-12-02 16:25:14 22

22 Stratix II EP2S60 DSP Development Board

The Stratix® II EP2S60 DSP development board

2010-04-07 10:54:27 51

51 提出了一种基于IEEE802.16e的具有线性编码复杂度的LDPC码的硬件编码器结构,并且在TSMC的0.18?滋m工艺库的最恶劣情况下,通过Design Compiler工具综合可以达到385MHz的速度。

2010-07-06 16:59:28 23

23 本文针对A律13折线法的算法特点,提出一种并行数据处理算法,实现了编码的流水线操作。运用VHDL语言将其在FPGA中实现,借助quartus II6.0平台进行验证,并对验证结果进行分析,评估了系统

2010-07-28 17:32:50 21

21 低密度奇偶校验码(Low-Density-Parity-Checkcodes,简称LDPC码)是第四代通信系统强有力的竞争者,它是一种逼近香农限的线性分组码,译码的复杂度较低;但它的直接编码运算量较大,

2010-08-09 15:06:22 0

0 引言

低密度奇偶校验(Low Density Parity Check Code,LDPC)码是一类具有稀疏校验矩阵的线性分组码,不仅有逼近Shannon限的良好性能,而且译码复杂度较低, 结

2007-08-15 17:20:18 1616

1616

摘要: 在简单介绍算术编码和自适应算术编码的基础上,介绍了利用FPGA器件并通过VHDL语言描述实现自适应算术编码的过程。整个编码系统在LTERA公司的MAX+plus Ⅱ软

2009-06-20 13:40:24 1026

1026

一种输出格式可控的多码率LDPC编码器实现

0 引 言

目前,LDPC码已广泛应用于深空通信、光纤通信、数字音视频广播等领域。由于有着较Turbo码更优秀的性能,

2009-11-25 09:56:43 1379

1379 基于FPGA的LDP

2011-01-06 16:45:57 45

45 提出了一种基于FPGA并利用Verilog HDL实现的CMI编码设计方法。研究了CMI码型的编码特点,提出了利用Altera公司CycloneⅡ系列EP2C5Q型号FPGA完成CMI编码功能的方案。在系统程序设计中,首先产生m序列,然后程序再对m序列进行CMI码型变换。在CMI码型变换过程中

2011-01-15 15:44:04 67

67 本文设计实现了一种支持WIMAX标准的码长、码率可配置LDPC码译码器,通过设计一种基于串行工作模式的运算单元,实现了对该标准中所有码率的支持

2011-06-08 09:52:17 1766

1766

本文研究高速 数据传输 中的低密度校验(LDPC)码编码的原理、有效编解码算法以及基于低密度校验编码的编码调制系统的分析和设计方法。LDPC 码是一类能够达到Shannon 极限性能的线性分

2011-06-14 16:33:36 0

0 本文首先介绍了信道编码的发展历程,以及LDPC码的基本原理和摹本概念,然后从校验矩阵的构造方法、迭代译码算法以及性能分析等几个方面对LDPC码进行了讨论, 介绍了相关技术的主

2011-08-26 11:44:01 0

0 本文提出了一种用FPGA实现纠错编码的设计思想,并以Altera MAX+PluslI为硬件开发平台。利用FPGA编程的特点,用软件编程方法,很好的解决了纠错编码中存在的码速变换和实时性问题,实现

2011-11-10 17:10:59 61

61 根据IEEE802.16e标准中对LDPC码的定义,利用FPGA对编码器进行了实现。所采用的算法使用了线性复杂度编码,降低了逻辑资源占用量,并提高了编码速度。

2011-12-07 14:06:14 33

33 建了一个基于Altera 的EP2S60硬件处理平台,利用Altera提供的FFT IP核,在100 MHz系统时钟下,数据吞吐率可达100 Ms/s。

2012-02-27 11:21:13 30

30 以Altera公司的FPGA EP2S60为例,探讨了SOPC系统设计的综合优化方法。

2012-03-12 11:49:28 1204

1204

为实现某专用接口装置的接口功能检测,文中详细地介绍了一种34位串行码的编码方式,并基于FPGA芯片设计了该类型编码的接收、发送电路。重点分析了电路各模块的设计思路。电路采

2012-06-18 12:37:09 41

41 本系统的设计是基于Altera公司的EP2S60系列的开发板,板上集成两片 SDRAM存储芯片、视频输入接口和VGA输出接口

2012-12-16 10:07:31 1214

1214 800Mbps准循环LDPC码编码器的FPGA实现

2016-05-09 10:59:26 37

37 基于EP1C3的FPGA程序ledverilog

2016-11-18 16:05:02 1

1 咨询委员会(CCSDS) 也将其推荐为应用于深空通信的信道编码方式。香农指出,对于任何信道,只要采用随机性编、译码方式,编码长度接近无限大,在其信息传输速率不超过信道容量时,采用最佳的似然译码方案,必然存在一种编码方式的误码率可以任意小。LDPC 码之

2017-10-31 14:07:53 3

3 该文通过对低密度校验(LDPC)码的编译码过程进行分析,提出了一种基于FPGA 的LDPC 码编译码器联合设计方法,该方法使编码器和译码器共用同一校验计算电路和复用相同的RAM 存储块,有效减少

2017-11-22 07:34:01 3928

3928

为设计出可近容量限传输且能普适应用于慢、快衰落信道下的编码协作方案,研究了基于卷积LDPC码的编码协作。基于卷积LDPC码的凿孔算法构造出可2路传输的分码字,实现编码协作,并在第二帧分码字传输阶段引入了空时传输进一步提升编码协作的性能。仿真验证了所提方案的有效性。

2018-01-16 14:38:02 0

0 出了一种基于FPGA并利用Verilog HDL实现的CMI编码设计方法。研究了CMI码型的编码特点,提出了利用Altera公司CycloneⅡ系列EP2C5Q型号FPGA完成CMI编码功能的方案

2018-05-31 04:38:00 2334

2334

的重视。基于准循环LDPC(QC-LDPC)码结构特点,提出了一种支持多种码率QC-LDPC 译码器的设计方法,并设计实现了一个能够实时自适应支持三个不同H 阵的通用QC-LDPC 译码器。

2019-01-08 09:22:00 2787

2787

本文对2004年由王鹏提出的LDPC码迭代编码算法[11]进行改进,转变为适用于多元LDPC码的编码算法,称为多元迭代编码算法;2005年,Hu Xiaoyu提出了渐进边增长(Progressive Edge Growth,PEG)构造算法[12],该算法译码性能好,但编码复杂度较高。

2018-09-23 08:59:00 4416

4416

结构化LDPC码可进行相应扩展通过对编译码算法,优化编译码结构进行调整,降低了编译码嚣硬件实现中的关键路径迟延,并采用Xilinx公司的Virtex一4 VLX80 FPGA芯片实现了一个码长10 240,码率1/2的非正则结构化LDPC码编码器和译码器。实现结果表明:该编码器信息吞吐量为1.878 Gb/

2021-03-26 15:58:00 12

12 今天是画师第二次和各位大侠见面,执笔绘画FPGA江湖,本人最近项目经验,写了篇基于FPGA的Varint编码(压缩算法)实现,这里分享给大家,仅供参考。如有转载,请在文章底部留言,请勿随意转载,否则

2021-04-02 16:29:16 1580

1580

基于FPGA的800Mbps准循环LDPC码译码器

2021-06-08 10:31:31 26

26 电子发烧友网站提供《LDPC编码器解码器产品简介(v2.0).pdf》资料免费下载

2023-09-13 15:21:48 2

2

![]()

![]()

![]()

电子发烧友App

电子发烧友App

评论