初始化时存入数据。那在IP核rom中存放大量数据对FPGA有什么影响,比如我想存65536个16位的数,然后在64M或者128M的时钟下读出来。会不会导致FPGA速度过慢?

2013-01-10 17:19:11

,因为FPGA之间的高速互联特性,也可以方便地在不同FPGA、不同FPGA板卡间部署完整的相关应用方案。成本方面,高画质IP虽然通道数量上并不占优势,但是带来的bitrate的大幅降低,可以显著降低

2019-03-08 10:47:22

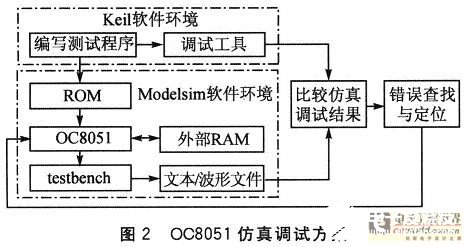

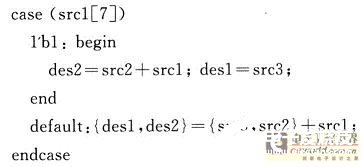

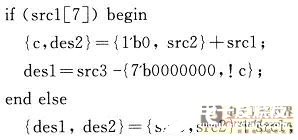

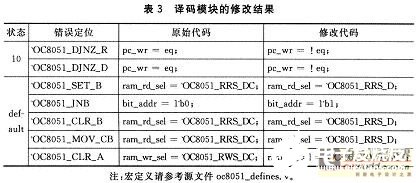

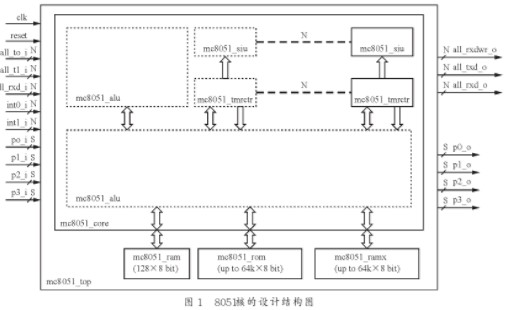

的基础上,给出了一种仿真调试方 案;利用该方案指出了其中若干逻辑错误并对其进行修改,最终完成了修改后IP核的FPGA下载测试。1 OC8051结构分析OpenCores网站提供的OC8051 IP核

2012-08-11 11:41:47

II中捕捉到LA的数据为1h,LD上的数据为1h后ConfigStart寄存器置高,配置开始。配置速度测试实验软硬件具体方案设计完毕后,软件在Visual C++6.0环境下实现并调试。硬件在

2020-05-14 07:00:00

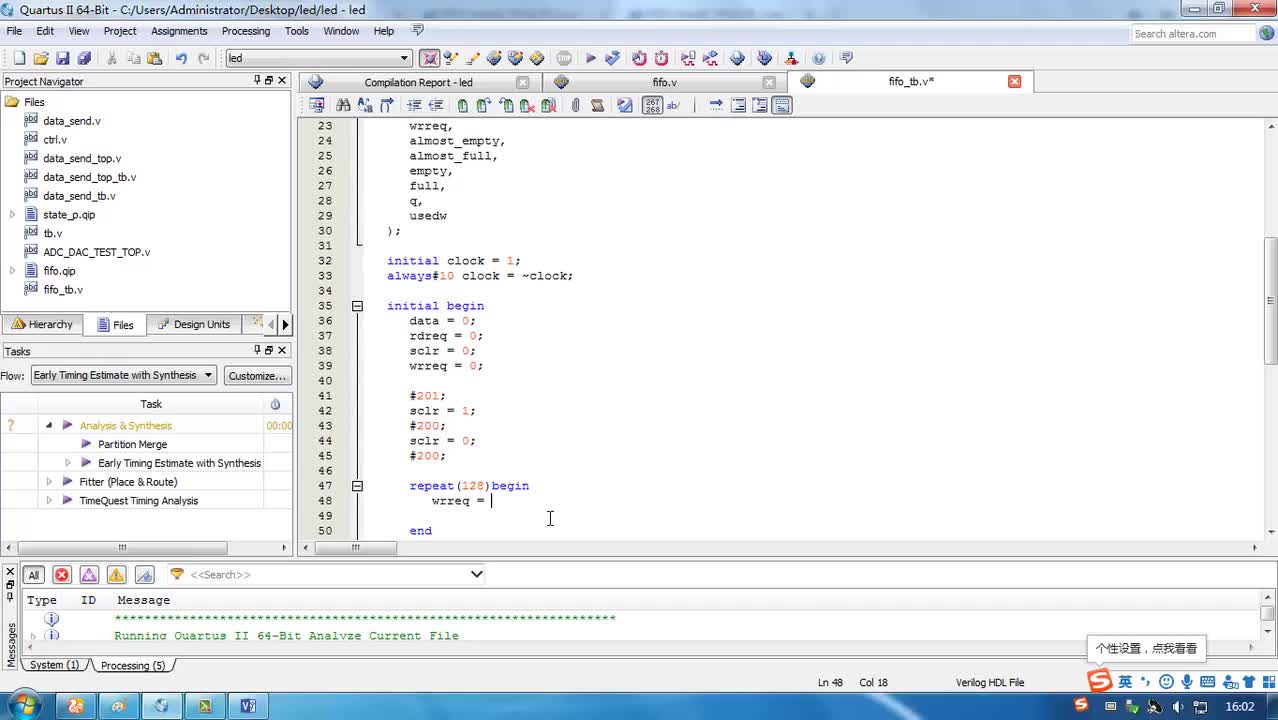

;wave->all items in design。这样就可以查看中间变量了。2.仿真带有ip核的工程总出错。大部分原因是因为你没有把支撑ip核的仿真的文件添加到工程中。对于verilog来说,要把

2017-04-15 21:46:29

FPGA嵌入8051单片机 IP核编程,编写的c语言矩阵键盘程序可以在stc89c54单片机上正常工作,但是下载到FPGA中8051单片机ip核的rom中,不能正常工作,求指教

2013-07-25 21:27:44

本帖最后由 jf_25420317 于 2023-11-17 11:10 编辑

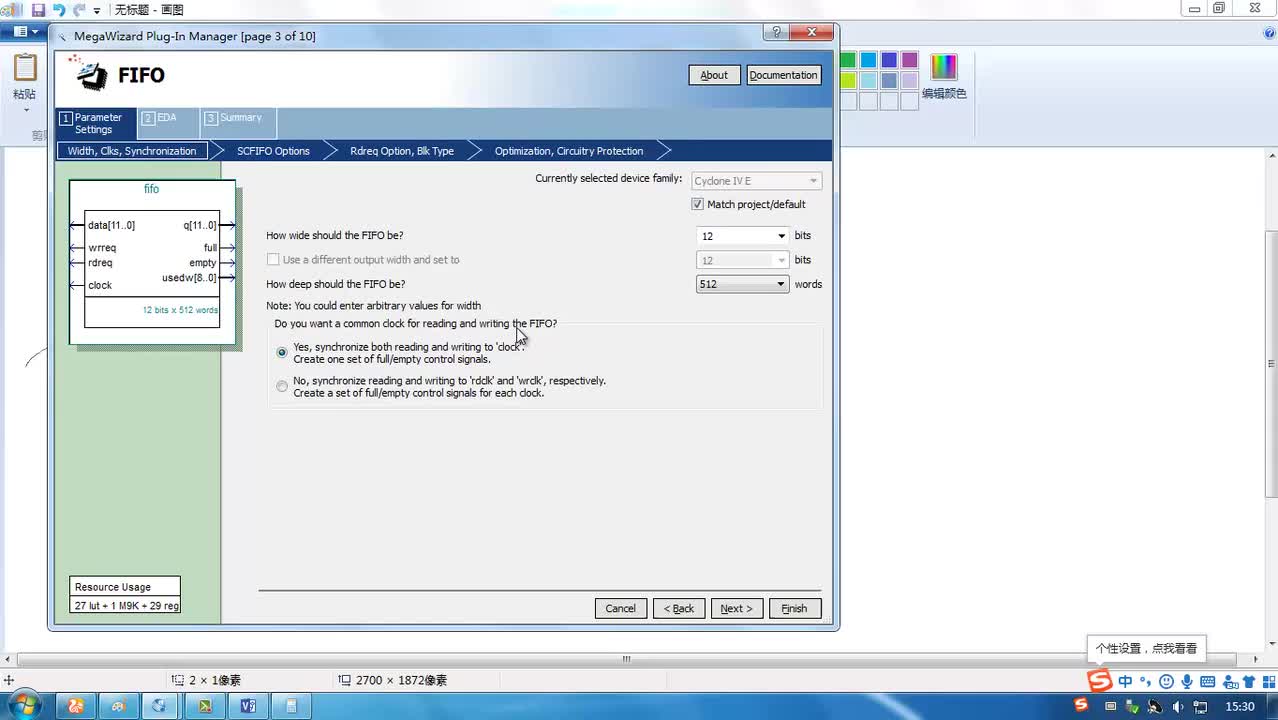

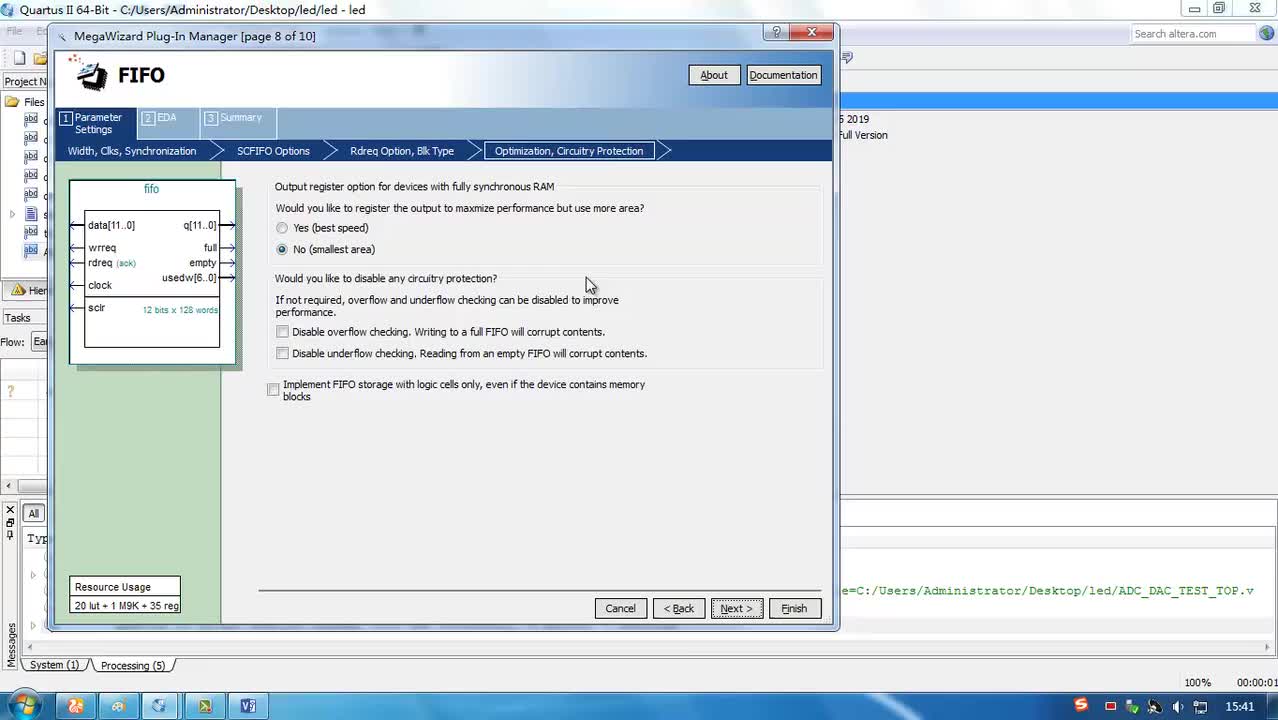

FPGA开发过程中,利用各种IP核,可以快速完成功能开发,不需要花费大量时间重复造轮子。

当我们面对使用新IP核

2023-11-17 11:09:22

哪位大神能给我发一下FPGA的8051核的完整工程文件,verilog语言的,或者教我怎么把这些文件搭建成一个工程,红包答谢,我企鹅2052341362

2017-03-14 13:22:11

有谁知道现在国内外有哪些公司卖FPGA的图像处理相关的IP核?

2015-04-28 21:34:24

是IP 核应用最广泛的形式。 固核(Firm IP Core) :固核在EDA 设计领域指的是带有平面规划信息的网表;具体在FPGA 设计中可以看做带有布局规划的软核,通常以RTL 代码和对应具体

2018-09-03 11:03:27

我使用fpga跑一个arm的软核,测试点亮一个led灯的程序。仿真结果与自己想要的结果是吻合的(顶层led的port是有输出的),但是下载到fpga开发板上后,运行就没有结果(连接顶层led的port测试没有输出)。请问如何去调试找出问题出在哪里?

2017-06-13 17:06:52

我调用了一个ip核 在下载到芯片中 有一个time-limited的问题 在完成ip核破解之后 还是无法解决 但是我在Google上的找到一个解决方法就是把ip核生成的v文件加到主项目文件中就是上面

2016-05-17 10:28:47

我研究了在设计中实现HDMI,DVI和Displayport的可行性。在这种设计中,FPGA将具有用于HDMI,DVI和DisplayPort的接收器,以接收来自外部源的信号。现在我不确定以下

2019-02-19 10:09:29

可以移植到不同的半导体工艺中去生产集成电路芯片。随着CPLD/FPGA的规模越来越大,设计越来越复杂,使用IP核是一个趋势。 本文研究了ATM流量控制的原理,并给出了一种IP核的实现方法,该IP核不仅可以用于独立芯片,还可以作为系统的一个子模块直接调用。

2011-09-27 11:54:25

功能也正常。现在将子板扣在VXI接口的母版上,只有在仿真模式下才正常工作,下载到FLASH之后,就不工作了,检查发现,DDR2的IP 核local_init_done信号一直不拉高, 有没有人遇到过类似问题,或者哪位大神帮忙分析一下原因?

2017-12-12 09:53:34

划分为几个主要模块,分别介绍各个模块的功能,用VHDL语言对其进行描述,用FPGA实现并通过了仿真验证。该IP核具有良好的移植性,可驱动不同规模的LCD电路。 关键词:LCD;驱动电路;IP 引言

2012-08-12 12:28:42

使用LabVIEW FPGA模块中的CORDIC IP核,配置arctan(X/Y)算法,配置完成之后,IP核只有一个输入。我参考网上VHDL CORDIC IP核,说是将XY合并了,高位X低位Y。不知道在LabVIEW中如何将两个值X、Y合并成一个(X、Y均为定点数)。具体情况如下图:

2019-09-10 20:07:07

8051Core 综合、编译应用。包括 Quartus II软件的基本应用,ROM、RAM 模块的生成,8051Core 的封装及应用测试。 附录 A 为 MC8051 IP Core 的指令集。 在阅读

2019-05-24 04:35:33

的SOPC系统中设计了LCD显示驱动IP核,并下载到Cyclone系列的FPGA中,实现了对LCD的显示驱动。

2019-08-06 08:29:14

很多人都说QUARYUSII中的IP核是收费的,不可以直接用的,其实不然,下面我以FIR滤波器的核的使用来给大家介绍IP核的使用,希望对大家有点帮助。 1.使用 (1)首先建立工程,这个就不

2019-06-03 09:09:51

Code + gcc环境编译后,那么就可以根据以下的环境搭建实现下载及在线调试了。目录一、软件下载二、搭建调试链接三、下载配置四、调试配置五、DEBUG调试一、软件下载OpenOCD:一个开源的片上调试器(Op

2022-01-25 08:03:30

USB_OTG_IP核中AMBA接口的设计与FPGA实现

2012-08-06 11:40:55

网上能找到的资料都是用altera的FPGA做的,有人用过xilinx FPGA搭建8051核吗?请与我联系

2017-06-03 14:59:23

最近在使用altera的FIR IP核做半带滤波器,quartus ii软件也破解了,firIP核也破解了,modelsin仿真也通过了,但是下载不了.sof文件到开发板,大家有用FIR IP核成功实现下板的经验吗,求大神指点呀。谢谢!

2018-05-11 16:01:15

在仿真fft ip核时 输出信号一直为0,检查了输入波形,应该没有问题,大家帮忙看看吧输入是由rom里面的mif文件产生的信号。

2017-11-21 10:44:53

有没有大神可以提供xilinx FPGA的FFT IP核的调用的verilog 的参考程序,最近在学习FFT的IP核的使用,但是仿真结果有问题,所以想找些参考设计,谢谢

2016-12-25 17:05:38

在较大工程中由于其局限性使用的越来越少,不推荐再学习;Verilog HDL为当今主流的设计方式;用IP核代替用户自己设计的逻辑,可以大大缩短开发周期,提供更加有效的逻辑综合和实现。Altera IP

2016-12-22 23:37:00

十、MC8051软核在FPGA上的使用本教程内容力求以详细的步骤和讲解让读者以最快的方式学会 MC8051 IP core 的应用以及相关设计软件的使用,并激起读者对 SOPC 技术的兴趣。本实验

2017-02-17 19:54:23

: (1) 在工程顶层中例化mc8051核(2) 在工程顶层中例化pll(3) 对工程进行分析和综合(4) 分配引脚(5) 编译并生成FPGA配置文件 (6) 使用USB Blaster配置FPGA打开

2017-02-17 22:17:50

8051Core 综合、编译应用。包括 Quartus II软件的基本应用,ROM、RAM 模块的生成,8051Core 的封装及应用测试。 附录 A 为 MC8051 IP Core 的指令集。 在阅读

2016-03-11 17:59:02

,手把手演示工程创建,IP核调用、Testbench编写以及仿真验证,让每一个0基础的朋友都能快速跟上节奏。另外,有一定基础的朋友,其实也可以观看,因为在设计中,我已经将很多的设计小技巧穿插在视频中了。请

2015-09-22 14:06:56

内建的示波器。SignalTapⅡ的使用要新建一个仿真调试文件。SignalTapⅡ可以设定信号的触发方式。其他请补充。另,FPGA的IP核并不是只有这几种,从新建IP核的界面可以看到,IP核还有很多。

2016-10-11 22:24:16

摘要针对FFT算法基于FPGA实现可配置的IP核。采用基于流水线结构和快速并行算法实现了蝶形运算和4k点FFT的输入点数、数据位宽、分解基自由配置。使用Verilog语言编写,利用ModelSim

2019-07-03 07:56:53

在较大工程中由于其局限性使用的越来越少,不推荐再学习;Verilog HDL为当今主流的设计方式;用IP核代替用户自己设计的逻辑,可以大大缩短开发周期,提供更加有效的逻辑综合和实现。Altera IP

2019-03-04 06:35:13

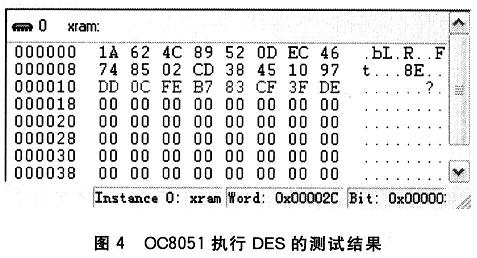

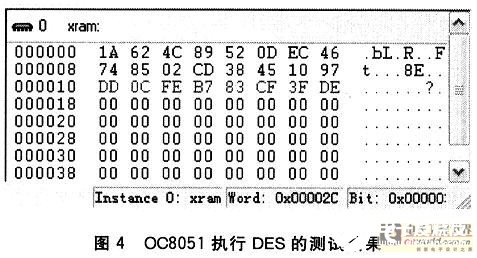

为机器码十六进制文件。将机器码作为RAM的初始化内容,即可进行仿真,在Modelsim软件中观察SoC工作时各个信号的波形。若将机器码通过工具下载到由FPGA实现的SoC中,那么就可以让SoC执行编写的程序

2022-04-01 17:48:02

最近研究凌阳的61单片机,可苦于61板是用并口实现下载,在线调试。可本人用的是本子并没有并口,每次都找台机下载是件非常的不方便。 于是在网上找了下凌阳单片机用USB实现下载的原理,可网上资料

2021-12-02 06:35:18

和朋友开发了几个基于 FPGA 的高速存储 IP 核,考虑到工业相机等应用场合需要有文件系统以方便做数据管理,所以将 NVMe 和 exFAT 两大IP核集成一起,可以实现将数据写入SSD后,拔下

2022-06-03 11:35:06

基于FPGA中8051 IP CORE 的数字电子钟设计求大神指导啊啊啊!

2015-05-05 22:49:09

基于FPGA的IP核8051上实现TCPIP的设计

2012-08-06 12:18:28

我毕业设计要做一个基于FPGA的IP核的DDS信号发生器,但是我不会用DDS的IP核,有没有好人能发我一份资料如何用IP核的呀。我的浏览器下载不了网站上的资料,所以只能发帖求帮忙了。

2015-03-10 11:46:40

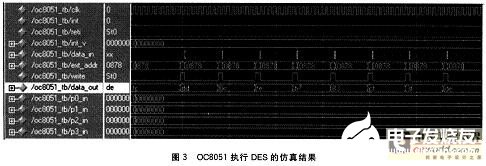

受到业内人士的青睐。本文在分析OpenCores网站提供的一款OC8051IP核的基础上,给出了一种仿真调试方案;利用该方案指出了其中若干逻辑错误并对其进行修改,最终完成了修改后IP核的FPGA下载测试。

2019-07-04 06:02:19

FFT IP核进行运算,输出FFT结果的实部和虚部分别存储在fft_result_real.txt和fft_result_image.txt文本中(仿真测试结果位于at7_img_ex05

2019-08-10 14:30:03

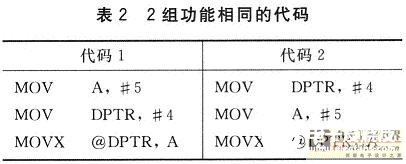

取出下一条指令。图3 取指令电路5、汇编汇编程序是为了调试软核而开发的,手工编写机器码很容易出错并且工作量很大。在调试过程中修改指令集时,汇编程序也要作相应的修改。所以要求编译器的结构简单性能可靠,在

2021-07-11 08:00:01

此提供了新的解决方案。IP核(IP Core)是具有特定电路功能的硬件描述语言程序,可较方便地进行修改和定制,以提高设计效率[3]。本文研究了基于FPGA的数据采集控制器IP 核的设计方案和实现方法,该IP核既可以应用在独立IC芯片上,还可作为合成系统的子模块直接调用,实现IP核的复用。

2019-07-09 07:23:09

核的分类和特点是什么?基于IP核的FPGA设计方法是什么?

2021-05-08 07:07:01

实现的RTL级设计,与具体实现工艺无关,相比于固核和硬核具有较大的灵活性,在FPGA中定制PCI接口软核实现PCI接口控制具有明显的优势:可以在单片FPGA中同时完成PCI接口和用户逻辑的设计,缩减成

2018-12-04 10:35:21

【摘要】:Viterbi译码器在通信系统中应用非常普遍,针对采用DSP只能进行相对较低速率的Vit-erbi译码的问题,人们开始采用FPGA实现高速率Viterbi译码。本文首先简单描述了

2010-04-26 16:08:39

工具,经面向硬件电路的仿真验证,本文的方法可实现OC-48接口(2.5Gb/s)上线速分组的IP碎片重组,并具有硬件开销小,可扩展性好的特点。关键词: IP碎片;FPGA;RLDRAM控制器;最大传输

2008-10-07 11:00:19

设计重用中的关键技术。如何保证IP核的高测试覆盖率,如何保证IP核在集成到SoC中后的可测试性.是该阶段分析的主要目标。所以在IP核实现之前.要检查IP核设计中是否违反了可测性设计规则; 低功耗分析

2021-09-01 19:32:45

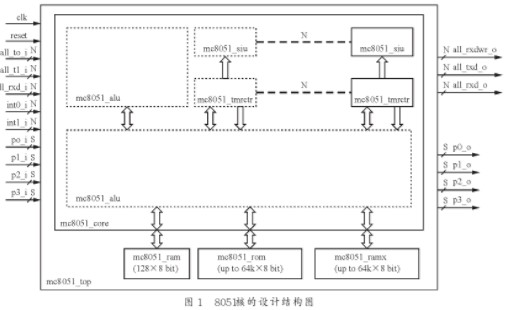

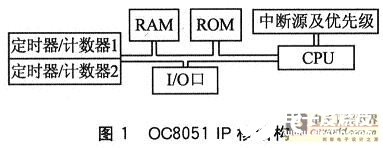

结构相同,采用CMOS工艺,因而常用80C51系列来指代所有具有8051指令系统的单片机。在80C51系列中,OC8051以架构清晰、取指带宽大、时钟效率高等诸多优点受到业内人士的青睐。

2019-08-13 07:34:07

(IntellectualProperty)核。IP核由相应领域的专业人员设计,并经反复验证。IP核的拥有者可通过出售IP获取利润。利用IP核,设计者只需做很少设计就可实现所需系统。基于IP核的模块化设计可缩短设计周期,提高设计质量。现场

2019-09-03 07:44:22

信号,所有的信号都是在时钟上升沿采样,是完全的同步设计。OCP接口信号包括数据信号、边带信号和测试信号。数据信号又分为基本信号、简单扩展信号、猝发信号和多线程扩展信号。所有IP核都需要基本数据信号中

2018-12-11 11:07:21

结构相同,采用CMOS工艺,因而常用80C51系列来指代所有具有8051指令系统的单片机。在80C51系列中,OC8051以架构清晰、取指带宽大、时钟效率高等诸多优点受到业内人士的青睐。

2019-08-13 06:10:46

本文在分析OpenCores网站提供的一款OC8051IP核的基础上,给出了一种仿真调试方案;利用该方案指出了其中若干逻辑错误并对其进行修改,最终完成了修改后IP核的FPGA下载测试。

2021-05-08 06:22:32

我的目标是实现一个给定的C算法是一个FPGA。所以,我最近得到了一个Zedboard,目标是实现该算法是PL部分(理想情况下PS中的顶级内容)。我在FPGA领域和编写VHDL / Verilog方面

2020-03-24 08:37:03

怎么才能在嵌入FPGA的IP核8051上实现TCP/IP的设计?

2021-04-29 06:51:27

的其它设计部分尽量不相关。为了满足上述的要求, 在FPGA中嵌入一个比较理想的选择, 而这个即通用又控制简单的IP核最好选择8051微处理器。

2019-08-26 06:27:15

在EDA软件中如何实现IP保护?在FPGA中如何实现IP保护?

2021-04-29 06:06:18

我在论坛下了8051IP核源代码,他是每个模块的代码。怎么把它综合到一个文件。弄成下图的样子

2015-04-24 15:15:18

中用测试脚本的形式,将matlab生成的1000个点cos数据time_domain_cos.txt文本导入,送给FFT IP核进行运算,输出FFT结果的实部和虚部分别存储在

2020-01-07 09:33:53

* b = 56。行为仿真验证.png (11.39 KB, 下载次数: 0)下载附件昨天 11:35 上传框图(Block Design)中调用IP核这里举一个简单的例子,通过调用乘法器IP核,产生

2018-05-16 11:42:55

基于RTD2271CW开发一款产品,datasheet中描述包含DW8051核,有哪位朋友知道市面上的C8051仿真器(比如EC5)是否可用于程序的仿真调试,和仿真器具体是怎么连接的,这个datasheet太坑人,竟然连个典型连接电路也没有。

2019-10-08 07:04:32

(Intellectual Property)核。IP核由相应领域的专业人员设计,并经反复验证。IP核的拥有者可通过出售IP获取利润。利用IP核,设计者只需做很少设计就可实现所需系统。基于IP核的模块化设计可缩短

2019-07-29 08:33:45

USB-Blaster的特性: 支持USB Blaster下载仿真调试,通过计算机的USB接口可对Altera的FPGA/CPLD以及配置芯片进行编程、调试等操作

2022-07-27 10:31:29

8051系列单机编辑调试仿真器(8051模拟器)

2009-08-05 08:21:02 177

177 在FPGA上对OC8051IP核的修改与测试

引 言

20世纪80年代初,Intel公司推出了MCS-51单片机,随后Intel以专利转让的形式把8051内核发布给许多半导体厂家,从而出

2010-01-07 11:23:57 1585

1585

文中在FPGA芯片中嵌入MC8051 IP Core,作为控制核心,利用Verilog HDL语言进行编程,设计了以MC8051 IPCore为核心的控制模块、计数模块、锁存模块和LCD显示模块等模块电路,采用等精度测量法

2013-01-07 11:17:31 4566

4566

MC8051_IP核简单指令的仿真步骤。

2016-05-06 11:47:41 0

0 在FPGA中植入8051后, 还可在上面实现简单的TCP/IP协议, 以支持远程访问或进行远程调试, 这只是在嵌入FPGA的8051上的一个应用。为了保证用户能够对8051实现不同的控制操作,设计时

2019-08-01 08:01:00 1229

1229

介绍了在大型工业模拟仿真系统中,利用FPGA和软IP核实现数据采集及收发控制的方案,并对其进行设计实现。重点阐述了在发送指令和采集接收两种数据流模式下.该IP核的控制处理逻辑及工作状态机的设计及实现

2018-11-07 11:14:19 20

20 在FPGA中植入8051后, 还可在上面实现简单的TCP/IP协议, 以支持远程访问或进行远程调试, 这只是在嵌入FPGA的8051上的一个应用。为了保证用户能够对8051实现不同的控制操作,设计时

2020-12-31 10:55:00 1186

1186

核的不同模块进行实体/块的仿真。前文回顾如何测试与验证复杂的FPGA设计(1)——面向实体或块的仿真在本篇文章中,我们将介绍如何在虹科IP核中执行面向全局的仿真,而这也是测

2022-06-15 17:31:20 389

389

电子发烧友App

电子发烧友App

评论