ALTERA常用主流芯片和配置芯片介绍,MAX7000S/AE, MAX3000A:5v/3.3vEEPOM工艺PLD,是ALTERA公司销量最大的产品

2011-12-05 17:42:11 10093

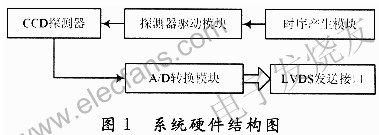

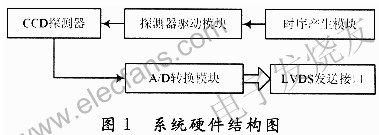

10093 电荷耦合器CCD具有尺寸小、精度高、功耗低、寿命长、测量精度高等优点,在图像传感和非接触测量领域得到了广泛应用。由于CCD芯片的转换效率、信噪比等光电特性只有在合适的时序

2012-02-29 11:32:44 9765

9765

本文在分析了 Sarnoff公司的 VCCD512H型帧转移面阵 CCD芯片的特性和工作过程后,结合整个 CCD相机电子系统的要求,完成了基于 FPGA技术的驱动时序发生器与数据缓存器的一体化

2019-01-04 07:55:00 3794

3794

的面阵CCD驱动时序发生器设计,基于CPLD的面阵CCD驱动时序发生器设计及其硬件实现,基于CPLD的线阵CCD驱动电路的设计,基于CPLD的线阵CCD驱动电路设计与实现,基于CPLD的线阵CCD驱动

2019-06-03 16:45:25

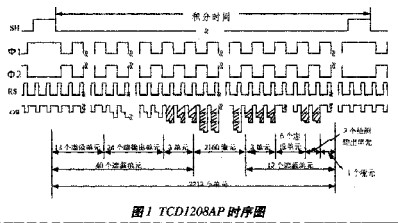

信号SHD、SHP,这两个信号的起始位置关系到CDS的输出,另外两个时钟是 CLPOB、PBLK;同时它还为CCD提供行驱动时序H1、H2和复位RG,H1、H2我采用的是默认设置值,RG我把下降沿延长

2018-11-02 09:33:14

TDI(Time Delayed and Integration)CCD(即时间延迟积分CCD)是近几年发展起来的一种新型光电传感器。TDI-CCD是基于对同一目标多次曝光,通过延迟积分的方法

2018-11-15 15:07:01

、Altera的MAX7000S系列和Lattice(原Vantis)的Mach系列等。将以查表法结构方式构成逻辑行为的器件称为FPGA,如Xilinx的SPARTAN系列、Altera的FLEX10K

2019-07-01 07:36:55

大家好...一世我正在使用XC95144xl CPLD从事系统内编程项目。一世想知道JTAG协议如何用于编程CPLD。我的意思是四个信号tck,tdi,tdo和tms如何实现“CPLD编程”。除了

2019-01-15 10:08:00

XILINX(spartan,virtex系列等)altrea(max,cyclone系列等)cpld/fpga芯片,全型号开发板及开发套件。并可提供ADI,TI的DSP,FREESCALE单片机等

2009-06-19 14:25:08

各位大侠,小弟CPLD/FPGA新手,遇到烧录不保存问题,详细描述如下:芯片型号:Altera MAX V 5M160ZE64Quartus版本:Quartus II 14.1问题描述:1

2015-07-21 10:40:23

、采用查找表的FPGA的工作原理第三节 Altera系列CPLD介绍一、MAX7000系列器件简介二、MAX7000系列器件的结构三、MAX7000系列器件功能描述第四节 Xilinx系列CPLD介绍······下载链接:`

2018-03-30 15:07:50

分析一款不错的基于CPLD的全帧型CCD图像传感器驱动系统设计

2021-04-29 07:09:48

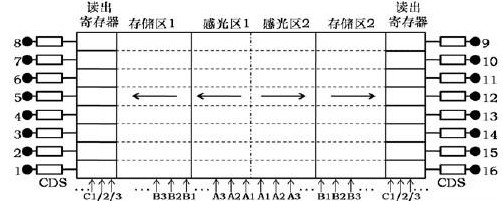

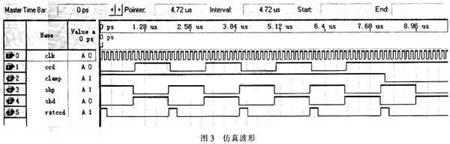

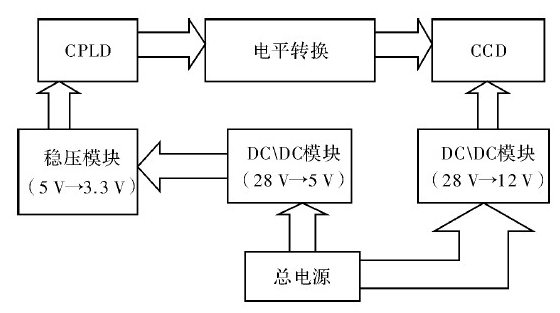

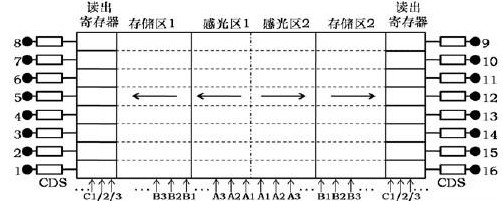

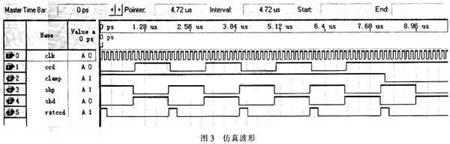

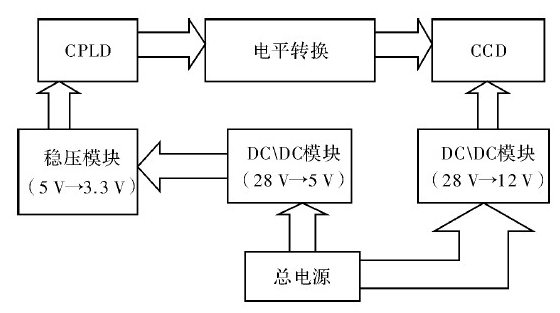

了基于可编程逻辑器件(CPLD)技术,将CCD驱动电路集成在一块芯片上,实现了CCD图像传感器的驱动电路,并且结合Ahera公司的EPM7160SLC84-10完成了硬件电路的设计。 1 全帧型CCD驱动

2018-11-15 14:54:53

独立的配置空间,可实现即插即用。这些优点使得PCI总线在数据采集、嵌入式系统和测控等领域得到广泛应用。实现PCI总线协议目前主要有专用接口芯片和CPLD实现两种方式。专用接口芯片使用简单方便、工作稳定

2019-05-29 05:00:02

本文介绍了一种采用专用CCD视频信号处理芯片和CPLD技术来设计的CCD视频信号处理电路,并采用USB接口技术实现数据传输。

2021-06-04 07:14:43

CCD驱动电路的实现是CCD应用技术的关键问题。以往大多是采用普通数字芯片实现驱动电路,CCD外围电路复杂,为了克服以上方法的缺点,利用VHDL硬件描述语言.运用FPGA技术完成驱动时序电路的实现

2019-10-21 06:05:17

直流电动机的PWM控制原理是什么?如何采用CPLD实现数字控制PWM信号?如何利用CPLD技术实现了逻辑和时序的控制?

2021-05-07 06:03:34

EPP技术和CPLD技术介绍应用CPLD及EPP技术对CCD信号像素级的高速采集

2021-04-08 06:11:10

本文在硬件电路设计上采用DSP 芯片和外围电路构成速度捕获电路,电机驱动控制器采用微控制芯片和外围电路构成了电流采样、过流保护、压力调节等电路,利用CPLD实现无刷直流电机的转子位置信号的逻辑换相

2021-05-12 06:44:08

动态重构其逻辑功能等特点。利用CPLD芯片和数字控制技术设计的时序电路,可将时序控制的精度提高到纳秒级,并且工作稳定,不受温度的影响,有利于系统定位精度的提高。

2021-05-06 09:44:24

CD 1501D CCD工作参数及时序分析基于FPGA的线阵CCD驱动时序及模拟信号处理的设计

2021-04-22 06:13:19

在以前CCD驱动电路的设计中采用AD9923A,由于CCD的驱动时序比较简单,而9923A寄存器配置相当复杂。现在要重新设计一种CCD驱动电路,并且CCD的驱动时序非常简单,所以想选择一款低端的专用ADC,能否推荐一款比较低端的类似9923A的CCD专用驱动芯片。

2018-11-29 09:14:32

给CPLD编程,使用MAX7000系列芯片,需要延时功能,延时时间1秒到几分钟,并可以外部进行调整延时时间,不知怎么处理,请教高手帮助!多谢!

2010-01-16 10:59:27

我想用CPLD实现两个芯片的时序匹配,CPLD的最小可调时序周期怎么确定?调整的过程是不是经过一次就延时一次?谢谢各位。

2012-08-22 20:19:25

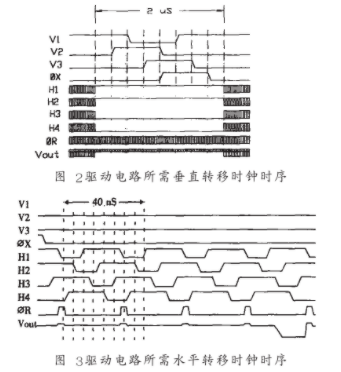

输出。在输出端得到与光学图像对应的一行行的视频信号。 2.3 基于CPLD的CCD时序发生器的实现 面阵CCD器件应用最重要的环节是驱动电路的设计与实现。CCD芯片所对应的原厂生产的专用驱动芯片虽然

2018-11-15 16:27:46

会对电路的实现产生何种影响?是否可器件有关系?问题2,请问如图一所示的试验电路,在MAX7000S及MAX3000A系列的CPLD中是否可以如此使用?如果不可以请问原因是什么?问题3,此电路下载

2011-11-22 09:22:54

本帖最后由 一只耳朵怪 于 2018-6-19 09:41 编辑

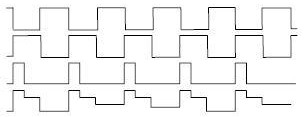

利用CPLD设计了一个CCD的驱动时序,CPLD输出的电平高低是0~3.3V,但是CCD要求是-8~6V,想问一下如何设计电平转化电路,是否有此类的电平转化芯片?不胜感激!!!

2018-06-14 13:25:02

过压保护控制芯片MAX4987AE资料下载内容主要介绍了:MAX4987AE引脚功能MAX4987AE内部方框图MAX4987AE典型应用电路

2021-03-30 07:02:53

产生方法, 结构简单、明确, 调试容易, 缺点是结构尺寸太大, 对于实现复杂的驱动时序有较大困难。 ( 4) 专用IC 驱动方法。这种方法就是利用CCD专用IC 来产生时序, 集成度高, 功能强

2018-11-13 11:13:20

高速数据采集系统的硬件结构MAX7000系列CPLD及其开发平台介绍CPLD在高速数据采集系统中的应用

2021-04-08 06:11:56

麻烦推荐一款AD,用来处理滨松的一款TDI CCD,不胜感激!

2018-08-02 06:39:02

用ALTERA 公司MAX7000 系列CPLD 芯片实现单片机与PC104 ISA 总线接口之间的并行通信,给出系统设计方法及程序源代码。包括通信软件和AHDL 设计部分。

2009-04-14 17:36:07 29

29 用ALTERA 公司MAX7000 系列CPLD 芯片实现单片机与PC104 ISA 总线接口之间的并行通信,给出系统设计方法及程序源代码。包括通信软件和AHDL 设计部分。

2009-05-14 13:24:39 14

14 详细介绍紫金山天文台红外实验室开发的CCD 相机系统的软硬件设计。根据柯达CCD 芯片KAF-0401LE 的时序要求, 用复杂可编程逻辑器件(CPLD)实现了CCD 的时序;采用相关双采样技术降低

2009-05-14 16:07:46 36

36 本文介绍了 MAX7000 系列CPLD 器件在DSP 接口电路中的应用,重点介绍了TMS3202××系列DSP 和存储器,LCD 接口的方法,并辅以VHDL 源程序的例子。关键词:DSP;MAX7000;CPLD;可编程

2009-06-29 08:57:03 43

43 针对TDI-CCD图像传感器中电荷包的转移损失问题,严格而详细地分析了TDI-CCD图像传感器中电荷包转移过程,建立了TDI-CCD图像传感器的电荷包总转移效率的数字模型。

2009-07-17 09:11:49 20

20 基于CPLD 和DSP 设计了线阵CCD 检测系统,CCD 的时序驱动由CPLD 实现,经过运放后的视频信号由TMS320F2812 进行采集和处理,此检测系统已成功应用于医药包装行业的数粒机系统,能够可

2009-08-13 14:53:46 22

22 针对Kodak 公司的前照明行间转移型面阵CCD KAI-0340,对其驱动要求进行详细的分析,设计满足CCD 所需偏置电压的供电模块;搭建CCD 时序脉冲驱动器电路;利用Xilinx 公司的可编程逻

2009-12-26 16:50:20 33

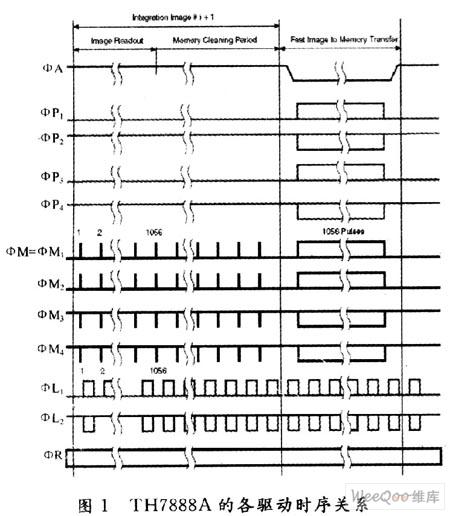

33 在分析了Sarnoff 公司的VCCD512H 面阵型CCD 图像传感器驱动时序关系的基础上,结合某CCD 相机电子系统的总体要求,完成了基于FPGA 驱动时序发生器与数据缓存器的一体化设计。选用X

2010-01-06 15:23:12 36

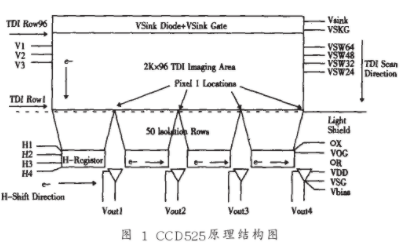

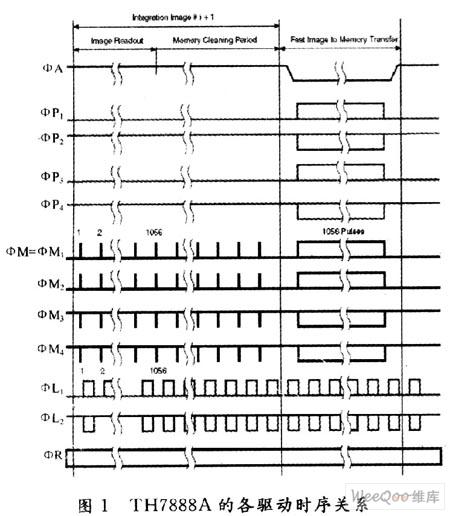

36 为解决TDI-CCD 作为遥感相机的图像传感器在使用中所面临的时序电路设计问题,文中较为详细地介绍了TDI-CCD 的结构和工作原理,并根据工程项目所使用的ILE2TDI-CCD 的特性,设

2010-01-12 09:54:50 21

21 基于CPLD的五相步进电机驱动器设计:介绍了一种基于CPLD 实现五相步进电机的驱动器的设计方案,可实现全步、半步控制。该方案具有体积小、成本低、功耗低和可靠性高等优点。

2010-01-14 18:42:35 101

101 基于CPLD 的全帧型CCD 图像传感器驱动系统设计刘凯波 曹剑中 王华伟 崔 巍来源:EDN China摘要: DALSA 公司的FTF4052M 22M Full-Frame 型CCD 是一款全帧型CCD 图像传感器。这里在分

2010-02-05 08:28:35 48

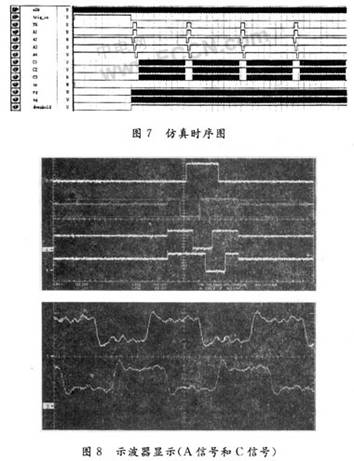

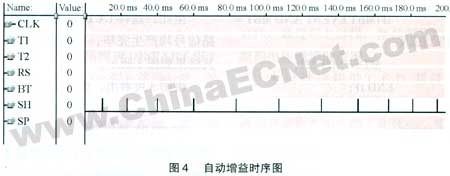

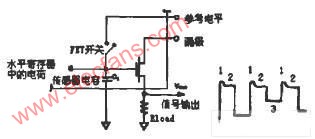

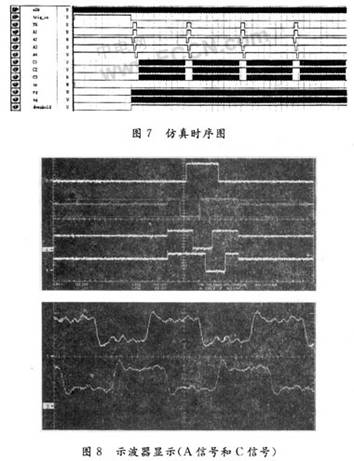

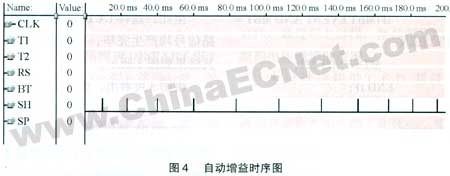

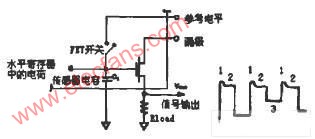

48 摘要本文介绍了一种基于CPLD并具有自动增益调整功能的CCD驱动电路。CCD输出的模拟电压值与其曝光时间有着密切的关系,根据这一原理,对CCD输出的模拟电压值进行A/D转换,由CPLD

2010-04-29 08:58:31 39

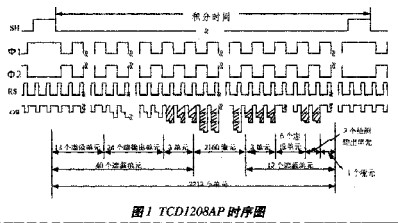

39 摘 要:本文以日本东芝公司的线阵CCD器件TCD1206SUP为例,在研究了线阵CCD器件工作原理和驱动电路波形的基础上,介绍了采用图形式层次设计方法,用复杂可编程逻辑器件(CPLD)设计线阵CCD

2010-07-15 13:42:30 68

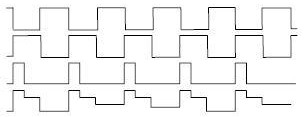

68 本文介绍了混合逻辑乘法器的设计实例,采用Altera公司的MAX7000AE系列的芯片及MAX+PLUSII开发系统实现,并给出VHDL的源程序及时序仿真波形。

2010-08-06 17:12:55 36

36 设计了一种基于DSP+CPLD构架的电能质量监测装置,该装置利用CPLD产生DSP外围器件的控制时序,丈中详细介绍了CPLD对DSP外围器件的逻辑接口设计,通过MAX+PLUSII对CPLD的控制时序进行

2010-08-26 16:06:20 31

31 摘要:本文就弥补以往用单片机产生线阵CCD驱动时序的不足进行了探讨;给出了使用AVR单片机产生驱动TCD1206线阵CCD的具体实例及相应程序。其定时关系精确,驱动频率达到推荐的速率

2010-09-14 21:30:44 109

109 介绍了高分辨率全帧CCD芯片FTF4027M的内部结构和驱动时序,利用CCD专用的集成芯片设计了该CCD芯片的驱动电路,其中包括驱动程序设置和所需偏置电压。实验结果表明:该驱动电路功

2010-11-13 17:33:22 0

0 摘要:用ALTERA公司MAX7000系列CPLD芯片实现单片机与PC104 ISA总线接口之间的并行通信,给出系统设计方法及程序源代码。包括通信软件和AHDL设计部分。CPLD(Complex Programmable Logi

2006-05-26 21:52:11 872

872

换体DMA高速数据采集电路的CPLD实现

介绍了换体DMA高速数据采集电路原理及其CPLD实现。用CPLD设计双端口RAM缓存、控制译码、时序逻辑电路,很好地解决了电路元件所占体积

2009-03-28 15:09:18 666

666

基于VHDL的XRD44L60驱动时序设计

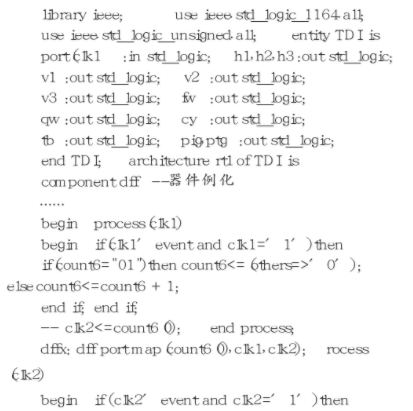

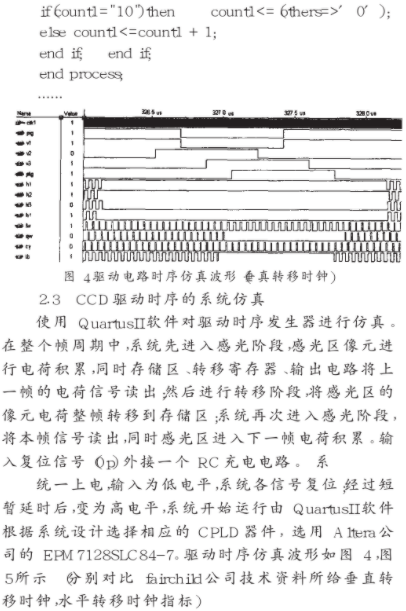

电荷耦合器件(Charge Coupled Devices,简称CCD)是一种光电转换式图像传感器。它利用光电转换原理将图像信息直接转换成电信号,实现非电量

2009-05-13 11:15:32 887

887

摘要:用ALTERA公司MAX7000系列CPLD芯片实现单片机与PC104 ISA总线接口之间的并行通信,给出系统设计方法及程序源代码。包括通信软件和AHDL设计部分。

关键词:CPLD

2009-06-20 13:34:28 1116

1116

基于CPLD的全帧型CCD图像传感器驱动系统设计

电荷耦合器件((2harge Coupled Devices,CCD)是20世纪70年代初发展起来的新型半导体集成光电器件。作为一种新型的MOS器件,与普

2009-10-25 10:16:08 635

635

基于CPLD的CCD驱动电路自动增益调整

ccd(charge couple device)是一种电荷藕合式光电转换器件。在物体位移测量系统中,常常以ccd作为位移传感器。当一

2009-12-14 14:04:39 750

750

本文设计了一种基于CPLD的可编程高精度CCD信号发生器。充分利用CPLD的可编程性.模拟出满足系统要求的CD信号,输出信号频率

2010-06-19 11:14:45 757

757

CCD驱动电路的实现是CCD应用技术的关键问题。以往大多是采用普通数字芯片实现驱动电路,CCD外围电路复杂,为了克服以上方法的缺点,利用VHDL硬件描述语言.运用FPGA技术完

2010-08-30 09:58:19 1289

1289

捅要:为了实现是弹武器瞄准自动化,本文设计了基于DSP和FPGA的高速高精确度双通道CCD图像采集系统,采用QUartuBn在AJtera的FPGA器件CYCLONEII上设计了CCD驱动时序电路,采用PsPICE设计了可以

2011-02-25 13:48:05 187

187 设计了一种以 线阵CCD 作为光电传感器的测隙装置。首先设计了测隙装置的总体方案,分析了方案的可行性;其次以CPLD为驱动利用Verlog-HDL语言设计了线阵CCD的工作时序,在对输出信号分

2011-08-10 16:41:58 44

44 采用MAXⅡ器件的EPM240T100C5N为控制核心,以TCD1500C为例,设计了基于CPLD的线阵CCD驱动电路,完成了硬件电路的原理图的设计,并实现了软件调试。通过QuartusⅡ软件平台,对其进行了模拟仿真。实

2011-11-03 15:24:40 129

129 CCD 芯片的驱动系统是数字航测相机的核心部分,它关系到整个相机的性能和技术指标。介绍了高分辨率全帧CCD 芯片FTF4052M 的内部结构和驱动时序,采用集成芯片设计了该CCD 芯片的驱动电

2011-11-04 16:54:38 74

74 为保证线阵CCD在图像测量中正常、稳定工作.必须设计出适合其工作的时序驱动电路。在分析TCDl501D线阵CCD驱动时序关系的基础上,通过分析CCD输出的图像信号1,给出了内、外相关双采

2011-11-07 15:08:43 148

148 针对面阵CCD KAI-1020 在高帧频工作模式下的驱动要求,以FPGA 作为控制单元及时序发生器,完成CCD 高帧频工作模式下的硬件及软件设计,仿真验证了驱动时序的正确性,完成了硬件电路的调试

2017-11-18 13:07:01 2181

2181

科学级CCD相机一般由高速CCD感光芯片、视频信号处理器、时序控制器、时序发生器、时序驱动器、外部光学成像系统等部分组成,本文分析了IL-E2型TDI-CCD 芯片的工作过程和对驱动信号的要求

2017-11-24 14:24:45 1982

1982

CCD驱动 电路的实现是CCD应用技术的关键问题。以往大多是采用普通数字芯片实现驱动电路,CCD外围电路复杂,为了克服以上方法的缺点,利用VHDL硬件描述语言.运用FPGA技术完成驱动时序电路的实现

2017-11-24 18:55:51 1523

1523

工作要求的CCD驱动方法才能保证测量结果准确。 在驱动CCD时要解决的两个主要问题分别是驱动时序的产生和输出信号的采集处理。在驱动时序产生方面,以往的研究大多只以成功驱动CCD为目的,因此扫描频率不高,一般采用器件的典型频

2018-01-24 14:12:43 0

0 在分析了SONY ICX415AL行间转移型面阵CCD的驱动时序的基础之上,提出了基于FPGA的驱动时序发生器的设计方案,并使用VHDL语言实现了该设计方案。整个设计充分结合了FPGA器件的设计简单

2018-05-22 10:21:00 2851

2851

CCD驱动电路的设计是CCD应用的关键问题之一。由于不同厂家生产的CCD的驱动时序不尽相同,同一厂家不同型号的CCD驱动时序也不完全一样,因此CCD用户必须面对驱动电路的设计问题。以往采用不同功能的数字芯片搭成的驱动电路,调试困难,灵活性较差。

2019-06-04 08:03:00 2306

2306

TDI CCD能在不牺牲空间分辨率和工作速度的情况下获得高灵敏度,这个突出特点使其 在高速、微光领域具有广泛的应用前景。在科研任务中,新型TDI CCD器件研制时间过长、 供货不及时等原因会严重影响科研生产任务的进度。

2019-05-06 08:22:00 2776

2776

本文主要介绍CCD传感器驱动电路的设计,包括驱动时序产生电路、电源变换电路和驱动器电路。其中,驱动时序产生电路向CCD传感器提供正常工作所需要的各种时序脉冲;电源变换电路向CCD提供正常工作时所需的各种直流偏置电压;驱动器电路用来提高驱动时序的驱动能力。

2018-12-30 09:47:00 7943

7943

本文档的主要内容详细介绍的是如何使用Verilog-HDL做CPLD设计的时序逻辑电路的实现。

2018-12-12 16:25:46 8

8 关键词:CCD , CPLD , 相机图像 , 信号模拟器 1 引言 多年来CCD 器件以体积小、重量轻、功耗小、工作电压低和抗烧毁等优点以及在分辨率、动态范围、灵敏度、实时传输、自扫描等特性

2019-02-12 09:01:01 385

385 CCD是一种广泛应用于成像系统中的光学传感器,TDI-CCD利用延时积分的方法,通过对同一物体多次曝光,实现增强型光能采集的目的。同时,根据像移补偿的速度,设计TDI-CCD的电荷转移速率,能够实现

2019-03-13 09:29:52 1751

1751 的面阵CCD驱动时序发生器设计,基于CPLD的面阵CCD驱动时序发生器设计及其硬件实现,基于CPLD的线阵CCD驱动电路的设计,基于CPLD的线阵CCD驱动电路设计与实现,基于CPLD的线阵CCD驱动

2019-05-16 08:00:00 16

16 主要讲述了PAL制视频时序信号的产生过程和PAL制彩色电视信号的合成方法,并以此为例介绍了一种低成本视频时序信号发生器的实现方案。文中讨论的视频时序信号发生器以Altera公司MAX II系列的CPLD为核心,只要根据需要修改CPLD中的信号形成程序,便可应用于其他非广播电视标准的视频系统当中

2019-05-24 14:14:29 32

32 线阵CCD一般不能直接在测量装置中使用,因此CCD驱动信号的产生及输出信号的处理是设计高精度、高可靠性和高性价比线阵CCD驱动模块的关键。

2019-09-18 15:43:43 2746

2746

为保证线阵CCD在图像测量中正常、稳定工作,必须设计出适合其工作的时序驱动电路。在分析TCD1501D 线阵CCD驱动时序关系的基础上 ,通过分析CCD输出的图像信号[1],给出了内、外相关双采样

2019-11-21 16:58:25 13

13 设计出高帧频的成像系统,以及能否实现两个CCD相机的同步采集。CCD工业相机的关键技术在于CCD驱动传输电路的设计,为了在实践中解决这两个问题,本文对CCD芯片的驱动脉冲和时序关系进行了详细的分析,设计出了基于FPGA的CCD驱动传输电路。

2019-11-26 15:35:15 21

21 介绍了CCD驱动电路的4种常用方式及其优缺点,详细阐述了基于高速超微型单片机C8051F300的CCD驱动电路设计,包括内部CCD驱动时序和外部输出同步信号的产生、像素输出电压的简单处理以及通过RS232接口在线调整CCD驱动频率等。系统克服了目前单片机方式在CCD驱动应用中存在的一些缺点。

2019-11-26 16:58:19 28

28 介绍了基于CPLD的线阵CCD数据采集系统的硬、软件构成,工作原理及设计方案。采用TOSHIBA公司近年来推出的高速线阵CCD芯片TCD1209D,针对其驱动时序的要求,选用XILINX公司的复杂

2019-11-28 16:23:00 19

19 本文在介绍了CCO工作原理、分析了CCD输出信号中混有的芥种噪声的基础上,提出几种产生CCD驱动时序方法,重点介绍了选用FGPA(现场可编程逻辑门阵列)来作为时序发生器的优点,并讲解了采用原理图

2019-12-06 15:36:00 21

21 首先简要陈述了提高线阵CCD遥感相机地面像元分辨力的几种有效途径,接着分析它们对相机灵敏度特性的影响。为了解决相机分辨力与灵敏度之间的矛盾,对几种高灵敏度CCD进行简要分析,其中重点对TDI

2020-04-20 17:59:00 22

22 TDI-CCD的工作原理与普通线阵CCD的工作原理有所不同,它要求行扫速率与目标的运动速率严格同步,否则就不能正确的提取目标的图像信息。当应用TDI-CCD对运动目标成像时,与其他视频扫描方法相比具有一系列优点,其中包括灵敏度高、动态范围大等。

2020-08-28 14:40:56 17803

17803 以加拿大Dalsa公司的全帧CCD图像传感器FTF4027M为例,在研究了全帧CCD结构和驱动时序的基础上,提出了基于现场可编程逻辑门阵列(FPGA)的驱动脉冲设计方法。选用FPGA作为硬件

2021-01-26 15:57:01 11

11 内外触发来实现的。在外触发模式下,利用外触发脉冲,可由用户控制CCD的曝光和信号输出时间;内触发时,可以调节CCD的积分时间和驱动频率。为提高信号输出质量,针对EMC问题给出了线阵CCD的外围驱动电路。实验结果表明,该方法调试方便、电路结

2021-03-01 16:51:00 9

9 内外触发来实现的。在外触发模式下,利用外触发脉冲,可由用户控制CCD的曝光和信号输出时间;内触发时,可以调节CCD的积分时间和驱动频率。为提高信号输出质量,针对EMC问题给出了线阵CCD的外围驱动电路。实验结果表明,该方法调试方便、电路结

2021-03-01 16:51:00 25

25 AD9847:集成时序驱动器的10位40 MSPS CCD信号处理器数据表

2021-04-15 09:38:37 5

5 AD9848/AD9849:集成时序驱动器的CCD信号处理器数据表

2021-04-15 21:19:26 14

14 ADDI9020:带V驱动器和精密时序发生器的60 MHz CCD信号处理器数据表

2021-05-08 18:50:37 3

3 Interline CCD 图像传感器的垂直时序优化

2022-11-15 20:36:34 0

0 CPLD的MAX系列器件库max-13.0.1.232

2022-12-21 17:26:11 4

4 电子发烧友网站提供《利用MAX II CPLD实现LCD控制器.pdf》资料免费下载

2023-11-10 09:36:39 0

0 TDI(Time Delayed and Integration)CCD(即时间延迟积分CCD)是近几年发展起来的一种新型光电传感器。

2024-03-19 14:47:53 128

128

正在加载...

电子发烧友App

电子发烧友App

评论