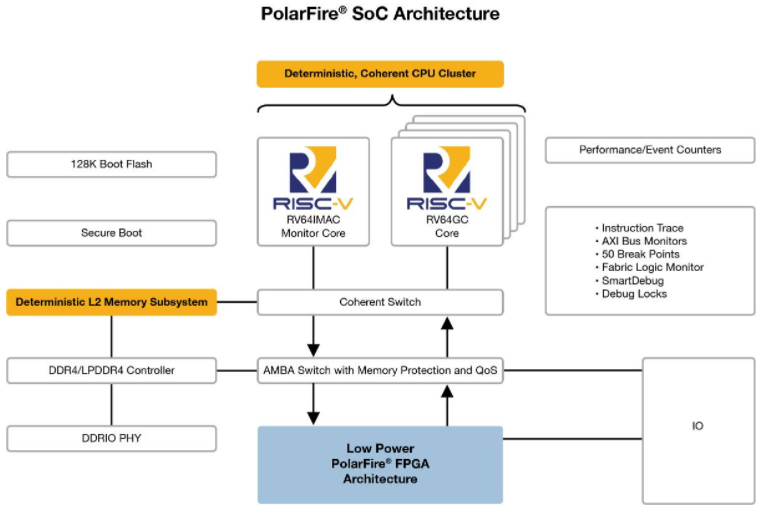

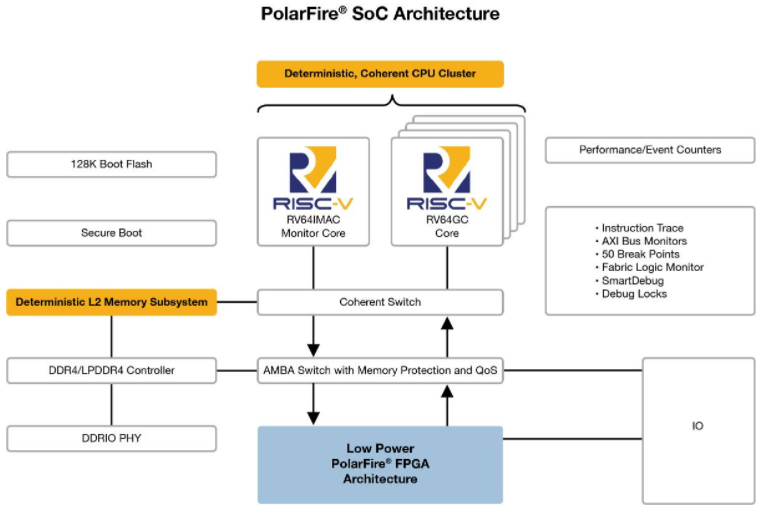

Microchip Technology Inc.(美国微芯科技公司)启动了PolarFire®片上系统(SoC)现场可编程门阵列(FPGA)早期使用计划(EAP)。

2019-12-11 16:55:15 1157

1157 的Zynq 7000, 找了一个HLS的教程,就开始了如下入门实验,体验高级语言综合设计IP。Vivado HLS是Xilinx 推出的高层次综合工具,采用C/C++语言进行FPGA设计。HLS提供了一些

2020-10-14 15:17:19 2880

2880

Microchip 今日推出经优化的耐辐射RT PolarFire FPGA,为新兴的高性能太空应用市场带来具备上述功能的新产品。

2019-10-23 17:04:10 822

822 Microsemi PolarFire FPGA视频和成像套件配备带有板载PolarFire FPGA的PolarFire视频与成像板以及一个双摄像头传感器板。

2019-11-08 11:23:33 923

923 Microchip开发系统高级总监Rodger Richey表示:“目前,许多MCU产品的功能安全工具成本非常高,Microchip推出的功能安全产品的价格仅为某些竞争性解决方案的三分之一,而且提供卓越的全球技术支持,助力客户加快产品上市并进一步简化开发流程。”

2020-01-21 00:27:00 3986

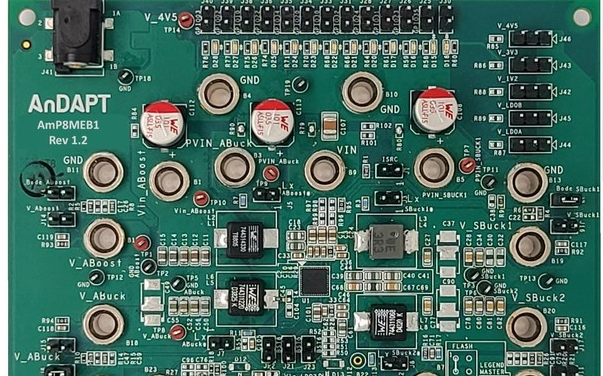

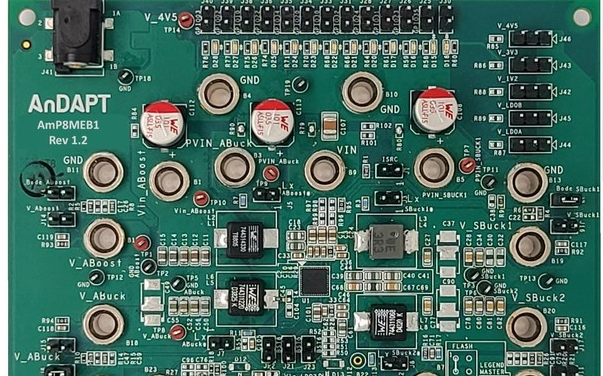

3986 AnDAPT现在支持使用集成、灵活和可编程的AmP电源管理IC为Microchip PolarFire FPGA供电。

2022-01-19 10:46:27 2192

2192

合集关键字 :Mi-V峰会;Microchip;Polarfire SOC FPGA;Mercury+ MP1; RISC-V 今年, Enclustra 发布了其首款基于 Microchip

2022-08-15 15:20:25 641

641

linux中高级开发工程师1. 精通linux环境c/c++应用编程,熟练makefile编写。2. 精通常用的数据结构算法,hash表、红黑树、自动机等。3. 精通linux下进程间通信、多线程开发、网络

2014-01-03 13:11:21

,一般将硬件初始化的工作交给汇编,比较复杂的操作交给C语言。③C语言具有很高的运行效率。2.嵌入式开发中的地位——开发工具3.高级语言中的低级语言:面向过程VS面向对象双系统C/C++ 工程师更稀缺C

2021-11-25 10:47:33

GPU 读取一款用 C++ 编写的软件一样。就是这么简单。

但为了优化该编程过程,您需要访问正确的平台。幸运的是,AMD 拥有完美的解决方案,这是一套开创性的工具,可在 FPGA 编程过程的每个环节为

2023-06-28 18:18:57

的高级语言(如C++和C++)的准入,这一点让众多软件工程师甘之如饴。与硬件描述语言(如VHDL和VerilogHDL)不同,它并不是由一小部分工程师掌握的工具。当然,它也有局限性:语言限制,就像非可合成

2021-07-10 08:00:00

`为客户提供完美的硅芯片解决方案是MICROCHIP坚持不懈的目标。但我们不只局限于提供硅芯片,还需要编程器、编译器、参考设计、函数库、应用笔记和评估板等支持工具,以助您最高效地完成评估和产品开发

2011-03-09 14:59:00

的设计工具和资源,以帮助开发人员采用和改进 RISC-V 应用程序设计。这些工具可与各种硬件套件结合使用——用于 PolarFire FPGA 的 PolarFire 评估套件和Icicle 套件

2021-09-07 17:59:56

、基于 RISC-V 的 PolarFire® SoC FPGA 打造,汇集了众多的 Mi-V 合作伙伴,助力加速不同行业的客户设计部署和商业应用。 设计人员现在可以开始开发和评估实时操作系统(RTOS

2020-09-25 11:39:42

Microchip提供了一系列高度集成的开发工具,可以简化应用程序的开发过程。这些工具分为核心开发工具和附属工具。基本开发工具主要有:•MPLAB®集成开发环境

2011-03-08 16:50:21

目前有一个算法库 用的c++ 用ccs在dsp上可以调试

现在希望把库放在8168的dsp上 需要将c++转换成c 有个工具

mmCC C++-to-C Translator、

不知道论坛里有没有 或者大家谁有

如果找不到mmcc

那么 8168上dsp用c调用c++库 有没有可行性

2018-06-21 13:14:22

开发c++应用程序。

这本书只涵盖了ARMC+t特有的信息。它旨在与ARM软件开发工具包2.11版本文档套件一起使用。

2023-08-08 06:29:26

模拟过程完成没有0错误,但在合成期间显示错误。我无法找到错误。我在合成期间在HLS工具中收到这样的错误“在E中包含的文件:/thaus / fact_L / facoriall

2020-05-21 13:58:09

、自然语言处理等核心算法,可助力开发者快速实现顺畅自然的智能语音交互体验。提供全栈式软硬件开发,兼容更多开发场景,支持用户自定义设 计,帮助开始者快速实现产品开发,打造专属 AI 语音产品。`

2020-06-28 17:55:59

TI CC2541开发套件

2023-03-25 01:27:25

`CPLD/FPGA高级应用开发指南第1章可编程逻辑器件与EDA技术第2章Xilinx CPLD系列产品第3章Xilinx FPGA系列产品第4章Xilinx ISE应用基础第5章FPGA高级

2013-06-02 10:13:17

这个名的本意是希望他成为C++编程语言的高效软件开发平台。然而,将Chromium裁剪成HiSDP并使之适合用于集团服务器环境下的软件开发还是经历了一些波折。最大的问题在于,Chromium的开发环境

2018-06-19 16:32:58

HiHope 满天星智能家居开发套件

2023-03-28 13:07:10

润和满天星系列Pegasus智能小车开发套件,基于海思Hi3861V100芯片,支持OpenHarmony轻量系统,实现巡线、避障功能通过寻迹模块获取路面轨道数据,运用寻迹算法使得智能小车可以按照固定轨道运行

2023-03-28 13:07:10

外设传感器,套件可通过积木组合的形式,实现多种应用场景,套件重点围绕智能回收站,有回收站定位人体红外、自动开盖、倾倒检测、满载上报功能等。套件配置OpenOCD JTAG调试工具方便开发者快速调试。

2023-03-28 13:07:10

意法半导体(ST)旗下全资子公司Portland Group公布该公司的Fortran、C和C++编译器及开发工具套件7.1版全面上市。PGI编译器和开发工具被广泛用于高性能计算技术(HPC),即以复杂现象的建模和仿真为主的科研计算领域,如海洋建模、天气预报、地震分析、生物信息分析技术等。

2019-07-17 07:18:38

加利福尼亚州,圣何塞— 2014年9月3日– S2C公司今日宣布TAI Player Pro 5.1版本正式发布。此次最新版本将帮助用户加速FPGA原型开发、提高工程师的生产力,以及实现最高的原型

2019-07-02 06:23:44

机器人设计及智能项目开发资料设计教程JAVA开发视频教程\培训视频教程C# .net开发视频教程\培训视频教程C++开发视频教程\培训视频教程汇集海量文档资料,技术开发资料,项目设计资料,硬件原理图PCB,软件源码包、开发工具包、开发设计技术文档等

2009-12-10 15:48:43

/C++的编程技巧者优先, 对图像信号处理、识别、编解码等算法有较好的基础;4、有良好的英文阅读能力; 5、具有良好的团队合作精神和刻苦钻研精神,责任心强,能承受一定的工作压力;6、有智能交通行业产品DSP开发经验者优先。工作地点:武汉有意向者请窗我:QQ:1940783351

2013-07-16 11:07:23

的高级语言(如C++和C++)的准入,这一点让众多软件工程师甘之如饴。与硬件描述语言(如VHDL和VerilogHDL)不同,它并不是由一小部分工程师掌握的工具。当然,它也有局限性:语言限制,就像非可合成

2021-07-06 08:00:00

者可以使用 C/C++ 语言来编写 FPGA 逻辑代码,而不需要了解寄存器传输级 (RTL) 语言或 FPGA 架构。

HLS可以提高开发效率和降低开发难度,因为 C/C++ 语言比 RTL 语言更高级

2023-10-13 20:11:51

/C++进行设计,然后由Vivado HLS编译器将C代码综合成HDL描述,最后再进行逻辑综合得到网表,这个网表最终会被映射到具体的FPGA器件上。就像C语言或者其他高级语言针对不同的处理器架构有着

2020-10-10 16:44:42

设计的综合。Vivado High Level Synthesis(即HLS,高层次综合)工具使用C、C++或System C语言在更抽象的算法层次描述设计,并将C代码综合成RTL级的HDL描述

2020-10-10 16:48:25

ap_none接口的IP核。在本章我们将通过呼吸灯实验,来学习如何使用Vivado HLS工具生成一个带有AXI4-Lite总线接口的IP核,并学习Vivado HLS工具C/RTL协同仿真平台的使用,以及在

2020-10-10 17:01:29

拼接算法试用计划:申请理由本人从事图像处理,图像编码算法有十年开发经验,熟悉xilinx FPGA的编程,曾设计过ISP算法,由于有监控场景需要宽幅图像,想借助发烧友论坛和米尔MYD-C7Z020平台

2019-10-30 17:03:31

库文件,甚至可以引进HDL程序,并进行仿真,最终生成网表文件,放到FPGA中执行。软件算法工程师不需要特别的培训,利用他们熟悉的C语言就可以直接进行硬件开发,减轻了硬件开发的瓶颈和压力。随着算法描述

2015-01-13 16:34:40

,我们一直在使用Vivado给我们提供的IP或者使用硬件描述语言制作 IP 。今天我们将讲解如何使用HLS-高级综合语言来创建属于我们自己的IP。我们将使用的工具称为Vitis HLS,此后称为 HLS

2022-09-09 16:45:27

将C、C++等语言转化成硬件描述语言,同时支持基于OpenCL等框架对Xilinx可编程逻辑器件进行开发,可加速算法开发的进程,缩短产品上市时间。HLS基本开发流程如下:(1) HLS工程新建/工程

2021-02-19 18:36:48

编写C或C++应用程序时,需要使用编译器工具链将其编译为机器代码。然后,您可以在基于Arm的处理器上运行此编译的可执行代码,或者使用模型对其进行模拟。

裸机编译编译器工具链包括以下组件:

•将C

2023-08-02 17:28:39

学习方向:嵌入式+人工智能嵌入式是一门技术学习目标1.嵌入式开发概述;(面向对象在嵌入式开发中角色)2.嵌入式Linux C++编程;(C++概述、C++学习方法、C++开发工具)3.C到C++升级

2021-12-24 07:32:38

。

Xilinx Vivado HLS (High-Level Synthesis,高层次综合) 工具支持将 C 、C++等语言转化成硬件描述语言,同时支持基于 OpenCL 等框架对 Xilinx

2023-08-24 14:40:42

。Xilinx Vivado HLS (High-Level Synthesis,高层次综合) 工具支持将 C 、C++等语言转化成硬件描述语言,同时支持基于 OpenCL 等框架对 Xilinx

2023-01-01 23:52:54

(High-Level Synthesis,高层次综合) 工具支持将 C 、C++等语言转化成硬件描述语言,同时支持基于 OpenCL 等框架对 Xilinx 可编程逻辑器件进行开发,可加速算法开发的进程,缩短

2023-01-01 23:46:20

(High-Level Synthesis,高层次综合) 工具支持将 C 、C++等语言转化成硬件描述语言,同时支持基于 OpenCL 等框架对 Xilinx 可编程逻辑器件进行开发,可加速算法开发的进程,缩短

2023-08-24 14:54:01

SDK 2017.4。Xilinx Vivado HLS(High-Level Synthesis,高层次综合)工具支持将C、C++等语言转化成硬件描述语言,同时支持基于OpenCL等框架

2021-11-11 09:38:32

::Blocks是一个开源的、跨平台的集成开发环境(IDE),支持C/C++等语言的开发,并且可以配合各种插件进行嵌入式开发。 7、PlatformIO:这是一款基于Python的开源工具,可以用来构建和调试嵌入式

2023-11-10 11:03:04

在《算法电路的合成:FPGA,ASIC和嵌入式系统》中,作者采用了一种新颖的方法来呈现用于合成算法电路的方法和示例,以更好地反映当今计算机系统设计者和工程师的需要。不像其他出版物,将讨论限制

2018-12-20 16:14:53

和生成比特流以对FPGA进行编程4 - 将比特流导入并阻塞到SDK中,基于此生成板级支持包(BSP)并与Zedboard连接。顺便说一下,SDK的目标是成为我在Vivado HLS中的测试平台吗?即在计算机中观察Zedboard产生的结果是否为例外情况。

2020-03-24 08:37:03

)是一个由自服务API、工具、文件和实例代码的集合,可轻松构建你自定义的Alexa skills,然后发布。机智云开源套件 Gokit 是一块标准的量产级嵌入式开发板,即代表了通用型智能设备。硬件集成

2017-03-31 11:54:05

。Vivado HLS作为该套件的一个组件,能帮助设计人员将采用C/C++语言开发的算法编译为RTL,以便在FPGA逻辑中运行。Vivado HLS工具非常适用于嵌入式视觉设计。在此流程中,您用C/C++

2014-04-21 15:49:33

你好,我有一个与switch语句的合成有关的问题。我开始使用Vivado HLS并且我已经创建了一个小的file.cpp,仅用于学习,但是当Vivado HLS合成文件时,我没有得到任何开关语句

2019-11-05 08:21:53

您好,我目前正在尝试使用Vivado HLS在FPGA上合成加密算法。我根据需要拆分了C ++代码并包含了一个测试平台,但是当我尝试模拟代码时,我得到一个错误,说找不到测试平台。我附上了错误图片和项目档案,希望有人能帮我找到解决方案。谢谢!LBlock_fpga.zip 48 KB

2020-05-15 09:26:33

进行编译的。本文仅验证了采用高级语言开发FPGA的可行性,还有很多优化工作待完善,仅以此文为大家提供一个新的视角,为软件开发人员利用FPGA进行算法加速做前期调研,欢迎感兴趣的同事共同交流。

2017-09-25 10:06:29

,10.1寸多触摸显示屏等整体硬件,一站式解决了开发者对硬件平台的选择与适配的问题。HarmonyOS2.0发布后,Firefly会继续深入HarmonyOS的生态。除了“HarmonyOS开发套件”,Firefly还推出了全国产化核心板系列,全面支持国内芯片与科技产业的发展,为客户持续创造价值。`

2021-06-03 13:59:55

的问题。 鸿蒙2.0发布后,Firefly会继续深入鸿蒙OS的生态。除了“鸿蒙开发套件”,Firefly还推出了全国产化核心板系列,全面支持国内芯片与科技产业的发展,为客户持续创造价值。

2021-06-03 14:47:15

,10.1寸多触摸显示屏等整体硬件,一站式解决了开发者对硬件平台的选择与适配的问题。HarmonyOS2.0发布后,Firefly会继续深入HarmonyOS的生态。除了“HarmonyOS开发套件”,Firefly还推出了全国产化核心板系列,全面支持国内芯片与科技产业的发展,为客户持续创造价值。`

2021-06-07 11:10:54

客户能够在小至 11 × 11 毫米的封装尺寸上实施解决方案。Microchip 的 PolarFire SoC FPGA Icicle 工具包非常适合智能嵌入式成像、物联网、工业自动化、国防、汽车

2021-03-09 19:48:43

Intel Agilex® F系列FPGA开发套件Intel Agilex® F系列FPGA开发套件设计用于使用兼容PCI-SIG的开发板开发和测试PCIe 4.0设计。该开发套件还可通过硬核处理器

2024-02-27 11:51:58

MIDI合成算法及其FPGA实现.

2012-04-16 13:57:38 44

44 Introduction to FPGA Design with Vivado High-Level Synthesis,使用 Vivado 高层次综合 (HLS) 进行 FPGA 设计的简介

2016-01-06 11:32:55 65

65 FPGA学习资料教程之Xilinx-FPGA高级开发工具,感兴趣的可以看看。

2016-09-01 15:27:27 0

0 HLS工具 以个人的理解,xilinx将HLS(高层次综合)定位于更方便的将复杂算法转化为硬件语言,通过添加某些配置条件HLS工具可以把可并行化的C/C++的代码转化为vhdl或verilog,相比于纯人工使用vhdl实现图像算法,该工具综合出的代码的硬件资源占用可能较多。

2019-10-12 17:34:00 1961

1961

高层次综合(High Level Synthesis, HLS)是Xilinx公司推出的最新一代的FPGA设计工具,它能让用户通过编写C/C++等高级语言代码实现RTL级的硬件功能。随着这款工具

2018-07-14 06:42:00 5868

5868 测试用的大量采样数据,完成对硬件系统原型的评估。对于I/Q压缩算法等类似高数据吞吐量的应用,采用Vivado HLS工具进行测试评估更加的方便。

2017-11-17 02:25:41 1267

1267

使用Xilinx Vivado HLS(Vivado 高层次综合)工具实现浮点复数QRD矩阵分解并提升开发效率。使用VivadoHLS可以快速、高效地基于FPGA实现各种矩阵分解算法,降低开发

2017-11-17 17:47:43 3293

3293

如果您正在努力开发计算内核,而且采用常规内存访问模式,并且循环迭代间的并行性比较容易提取,这时,Vivado® 设计套件高层次综合(HLS) 工具是创建高性能加速器的极好资源。通过向C 语言高级算法描述中添加一些编译指示,就可以在赛灵思FPGA 上快速实现高吞吐量的处理引擎。

2017-11-17 18:12:01 1647

1647 、边缘模糊等级和脉冲噪声等指标评估基于该算法图像处理效果。与传统时域算法作对比,对比结果表明该算法在处理效果和运算速度上的优异性。基于Zedboard开发板,运用Vivado HLS高级综合工具将算法的C程序综合成硬件IP,并搭建了包含ARM处理器和VGA等

2017-12-12 14:07:38 2

2 本文介绍了PolarFire FPGA主要特性,低功耗特性,可靠特性和安全特性,框图,以及PolarFire FPGA评估板硬件特性,框图,电路图和元件表以及PCB元件布局图。

2018-06-17 18:06:00 5573

5573

HLS,高层综合)。这个工具直接使用C、C++或SystemC 开发的高层描述来综合数字硬件,这样就不再需要人工做出用于硬件的设计,像是VHDL 或Verilog 这样的文件,而是由HLS 工具来做这个事情。

2018-06-04 01:43:00 7171

7171

高级综合( HLS)工具及其入门指南

2018-06-20 00:08:00 3952

3952

赛灵思公司推出 Vivado 设计套件 HLx 版本,为All Programmable SoC 和 FPGA以及打造可复用的平台提供了全新超高生产力设计方法。新版 HLx 包括 HL 系统版本

2018-08-17 11:43:00 2677

2677 美高森美公司(Microsemi ) 宣布提供低成本IGLOO 2 FPGA评测工具套件,为客户提供PCI Express (PCIe)兼容外形尺寸评测平台。这款功能齐全的工具套件可让设计人员快速评测美高森美最近发布的IGLOO2 FPGA器件的集成度、低成本、安全性、即时性和高可靠性特性。

2018-09-18 16:49:00 1399

1399 关键词:Actel , Fusion , 高级 , 工具 , 套件 爱特 (Actel) 正式付运Fusion高级开发工具套件,协助设计人员开发系统和功率管理应用。该工具套件带有Actel

2018-10-24 20:44:01 560

560 使用Spartan-6 FPGA消费类视频套件加速DTV设计中高级视频算法的开发。

与消费者部门主管Harry Raftopoulos近距离观看套件。

2018-11-28 06:15:00 1714

1714 Xilinx 战略应用高级工程师。专注于 C/C++ 高层次综合,拥有多年利用 Xilinx FPGA 实现数字信号处理算法的经验,对 Xilinx FPGA 的架构、开发工具和设计理念有深入的理解。

2019-08-01 15:30:49 1869

1869 接着开始正文。据观察,HLS的发展呈现愈演愈烈的趋势,随着Xilinx Vivado HLS的推出,intel也快马加鞭的推出了其HLS工具。HLS可以在一定程度上降低FPGA的入门门槛(不用编写

2019-07-31 09:45:17 6232

6232

Microchip启动了PolarFire片上系统(SoC)现场可编程门阵列(FPGA)早期使用计划(EAP)。

2019-12-16 15:16:21 631

631 Microchip启动了PolarFire片上系统(SoC)现场可编程门阵列(FPGA)早期使用计划(EAP)。

2019-12-26 15:39:03 1100

1100 ,Microchip Technology Inc.(美国微芯科技公司)宣布推出业界首款基于 RISC-V 的SoC FPGA开发工具包。这款名为Icicle 的开发工具包专为业界领先的低功耗、低成本

2020-09-24 09:37:29 3047

3047 基于RISC-V的SoC FPGA属于Microchip RISC-V生态系统,这是支持各种操作系统和生态系统合作伙伴的工具套件和设计资源组合。

2021-02-05 14:23:46 2222

2222 算法都是由开发人员使用C++语言原生开发的,而他们对底层FPGA硬件知之甚少或一无所知。为了支持这一重要的开发群体,Microchip Technology Inc.(美国微芯科技公司)推出了名为SmartHLS的HLS设计工作流程,成为其PolarFire FPGA系列产品的新成员。

2021-09-07 11:50:27 6446

6446 Vitis HLS 是一种高层次综合工具,支持将 C、C++ 和 OpenCL 函数硬连线到器件逻辑互连结构和 RAM/DSP 块上。Vitis HLS 可在Vitis 应用加速开发流程中实现硬件

2022-05-25 09:43:36 1930

1930 由于它是一个开放标准,为 PolarFire 设备开发的代码可以扩展和缩减 Microchip FPGA SoC 产品组合以及其他 RISC-V RV64GC 目标,而无需从头开始。

2022-06-01 10:18:56 1217

1217

在整个流程中,用户先创建一个设计 C、C++ 或 SystemC 源代码,以及一个C的测试平台。通过 Vivado HLS Synthesis 运行设计,生成 RTL 设计,代码可以是 Verilog,也可以是 VHDL。

2022-06-02 09:48:17 6129

6129 出于这个原因,Microchip 继续在其 PolarFire FPGA SoC 系列中进行创新——推出的具有 25K 逻辑元件和硬化四核 RISC-V CPU 的 MPFS025 SoC。

2022-07-10 15:42:15 907

907

HLS的FPGA开发方法是只抽象出可以在C/C++环境中轻松表达的应用部分。通过使用Vivado(Xilinx)或Intel(Quartus)工具,HLS工具流程基本上可用于任何BittWare板。

2022-08-02 09:18:32 1340

1340

1、HLS简介 HLS(High-Level Synthesis)高层综合,就是将 C/C++的功能用 RTL 来实现,将 FPGA 的组件在一个软件环境中来开发,这个模块的功能验证在软件环境

2022-12-02 12:30:02 2570

2570 推理解决方案的快速开发平台 》的在线研讨会。 VectorBlox平台是一款软件开发工具包(SDK),可实现基于PolarFire FPGA的机器学习(ML)推理。这款SDK有多种工具,无需对FPGA

2022-12-12 20:25:08 605

605 HLS (high-level synthesis)称为高级综合, 它的主要功能是用 C/C++为 FPGA开发 算法。这将提升FPGA 算法开发的生产力。 Xilinx 最新的HLS

2023-01-15 12:10:04 2968

2968 AMD Vitis HLS 工具允许用户通过将 C/C++ 函数综合成 RTL,轻松创建复杂的 FPGA 算法。Vitis HLS 工具与 Vivado Design Suite(用于综合、布置和布线)及 Vitis 统一软件平台(用于所有异构系统设计和应用)高度集成。

2023-04-23 10:41:01 652

652

。 这些新工具进一步扩大了Microchip FPGA全面的工具和服务工具包,支持成熟的PolarFire系列器

2023-06-08 08:05:02 403

403 。 这些新工具进一步扩大了Microchip FPGA全面的工具和服务工具包,支持成熟的PolarFire系列器件

2023-06-15 09:05:01 311

311 该项目包含使用高级综合 (HLS) 的 2D 中值滤波器算法的实现。该项目的目标是在不到 3 ms的时间内对测试图像进行去噪,同时消耗不到 25% 的可用 PL 资源。特征如下:

2023-07-03 09:06:43 466

466

安全当前已成为各垂直市场所有设计的当务之急。今天,有进一步证据向系统架构师和设计人员证明,使用Microchip Technology Inc.(美国微芯科技公司)的PolarFire FPGA

2023-09-05 11:50:01 291

291 安全当前已成为各垂直市场所有设计的当务之急。今天,有进一步证据向系统架构师和设计人员证明,使用Microchip Technology Inc.(美国微芯科技公司)的PolarFire® FPGA

2023-09-05 11:49:53 905

905 Microchip推出针对智能边缘设计的定制PolarFire FPGA和SoC解决方案堆栈,以加快开发速度,同时推动FPGA的采用。 为了加快智能边缘设计,Microchip Technology

2023-10-26 18:09:50 746

746

电子发烧友App

电子发烧友App

评论