电子发烧友网核心提示:本文为玩转赛灵思Zedboard开发板(3):基于Zynq PL的流水灯,内容精彩,敬请对电子发烧友网保持密切关注。基于Zynq PL的流水灯是使用PL做流水灯实验,目的是为

2012-12-05 14:25:41 12770

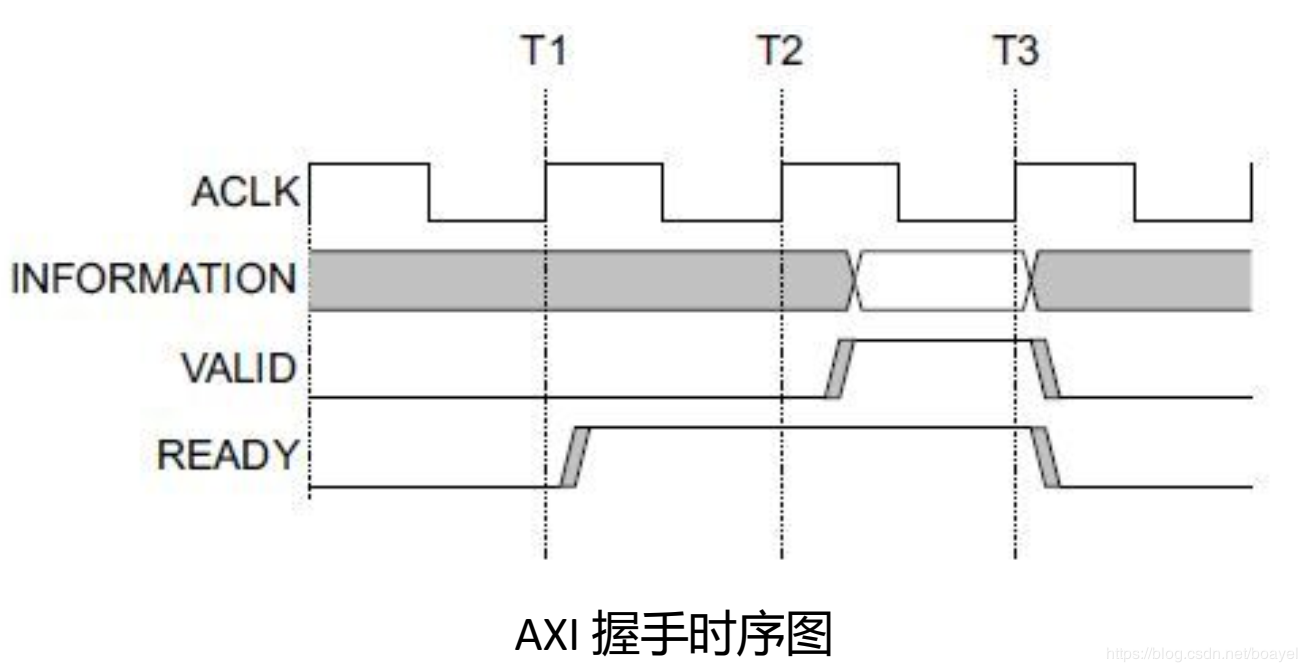

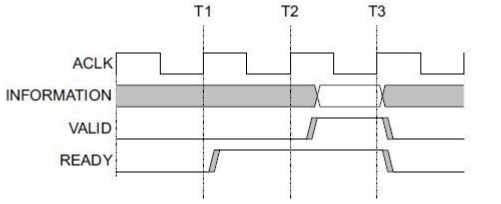

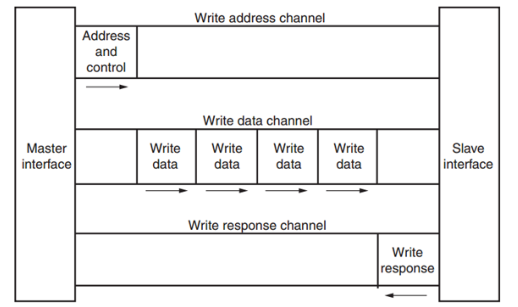

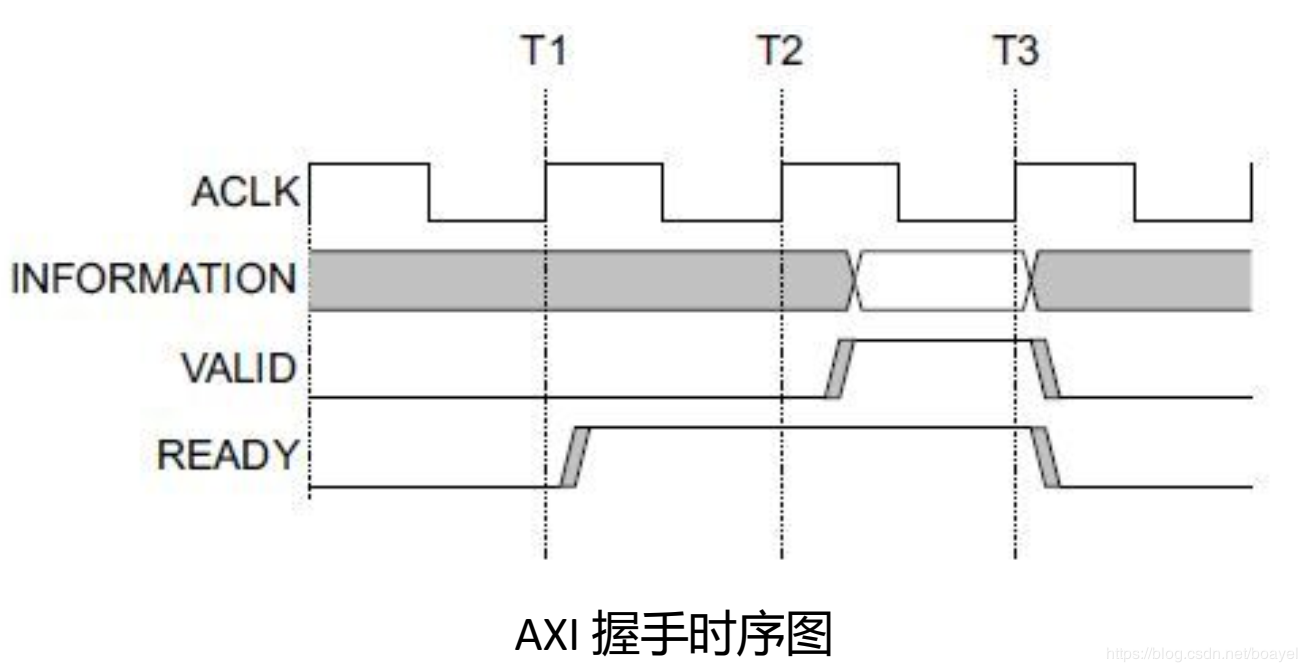

12770 AXI 协议主要描述了主设备和从设备之间的数据传输方式,主设备和从设备之间通过握手信号建立连接。当从设备准备好接收数据时,会发出 READY 信号。

2020-11-13 16:43:47 5099

5099

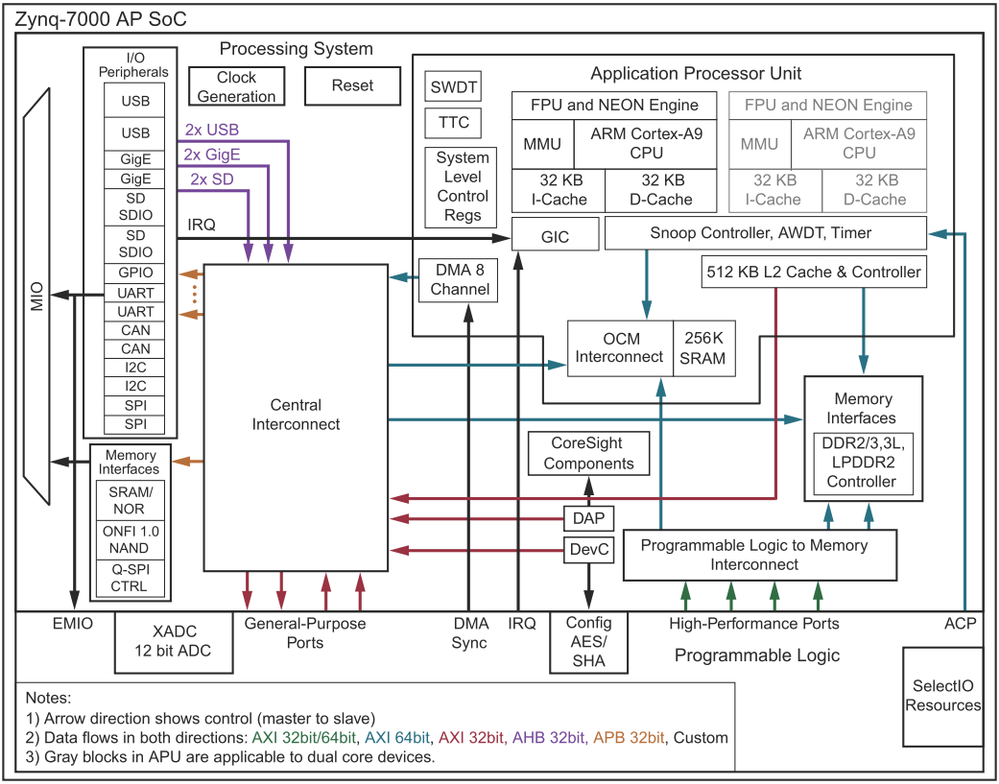

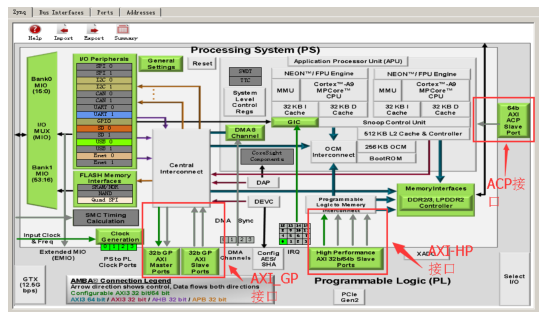

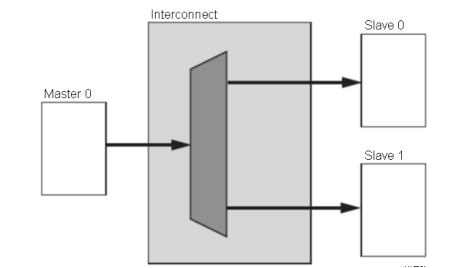

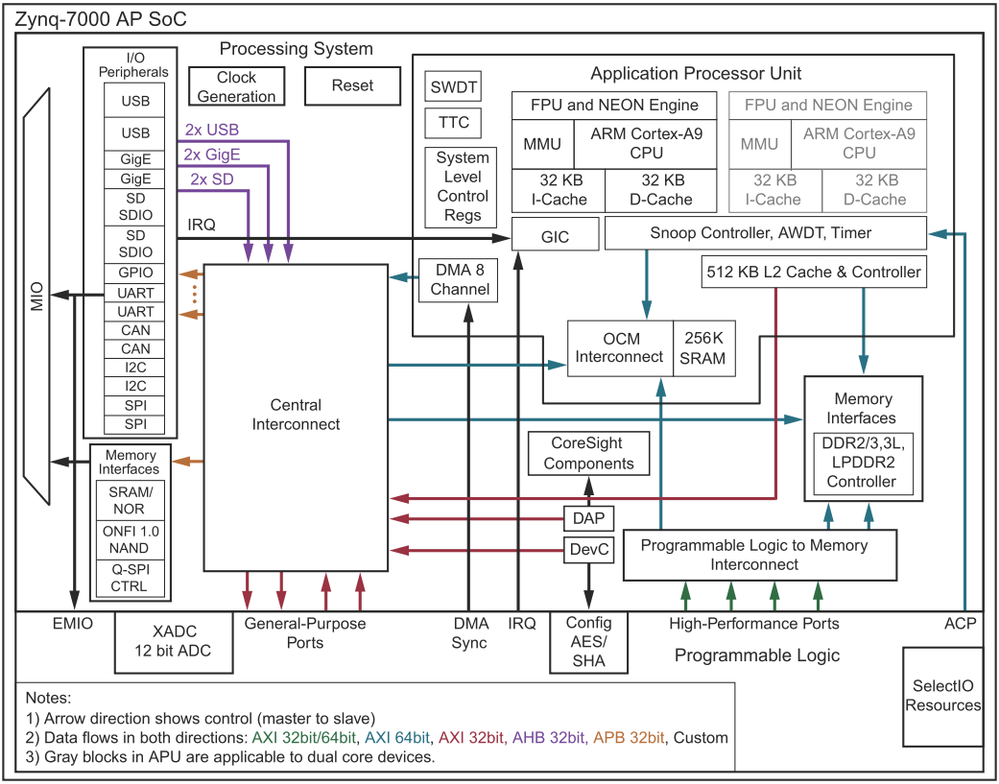

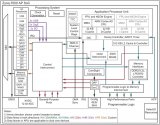

I/O peripherals (IOP) Interconnect ZYNQ内部的总体框架如所示,PS中包含2个ARM Cortex-9的内核,一些基本的外设扩展口以及Memory接口。PS和PL的相互通信通过

2020-11-03 12:33:13 4586

4586

的逻辑部分,PS侧为arm端以及一些AXI接口控制部分,二者实际上通过AXI接口实现通信和互联。PS可以通过AXI来对PL逻辑部分进行配置和控制,PL侧通过AXI和PS进行数据交互。本章

2020-11-30 11:56:01 3490

3490

。 Pynq降低了开发人员的门槛,但知其然也知其所以然,开发效率将会更高。因此,在进入PYNQ的python开发之前,我们先来学习ZYNQ的PL与PS开发,为接下来的学习提供良好的基础。 本部分的学习

2020-12-25 14:11:50 6843

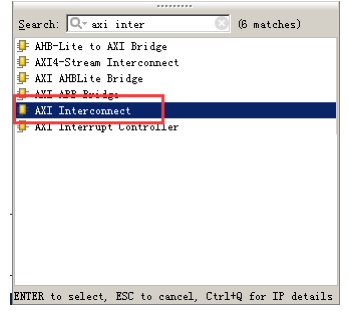

6843 使用zynq最大的疑问就是如何把PS和PL结合起来使用,在其他的SOC芯片中一般都会有GPIO,本实验使用一个AXI GPIO的IP核,让PS端通过AXI总线控制PL端的LED灯,实验虽然简单,不过可以让我们了解PL和PS是如何结合的。

2021-02-01 10:06:00 6183

6183

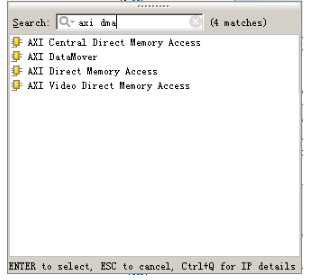

PL和PS的高效交互是zynq soc开发的重中之重,我们常常需要将PL端的大量数据实时送到PS端处理,或者将PS端处理结果实时送到PL端处理,常规我们会想到使用DMA的方式来进行,但是各种协议非常

2021-01-30 09:54:00 12917

12917

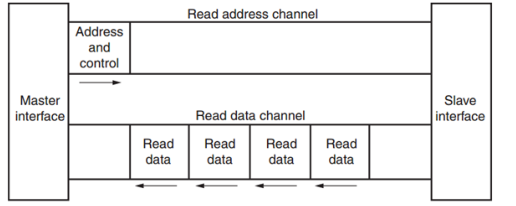

有时CPU需要与PL进行小批量的数据交换,可以通过BRAM模块,也就是Block RAM实现此要求。本章通过Zynq的GP Master接口读写PL端的BRAM,实现与PL的交互。在本实验中加入了自定义的FPGA程序,并利用AXI4总线进行配置,通知其何时读写BRAM。

2021-02-22 13:51:00 7359

7359

/p/005899fe6815 二、ZYNQ7020 分为PS端、PL端 PS: 处理系统 (Processing System) , 就是与 FPGA 无关的 ARM 的 SOC 的部分。 PL: 可编程逻辑

2021-05-12 10:25:31 13960

13960

本文主要介绍ZYNQ PS + PL异构多核案例的使用说明,适用开发环境:Windows 7/10 64bit、Xilinx Vivado 2017.4、Xilinx SDK 2017.4

2021-09-07 17:03:30 2881

2881

交互数据将会经过Zynq子系统的内部总线(用空再考证一下是什么名称)控制器“Central Interconnect”转发给Memory Interfaces。

2022-09-16 10:33:44 6493

6493 xilinx mpsoc 平台中,PS 和 PL 进行交互时,PS 需要获取 PL 发出的中断信号。从 mpsoc 技术参考手册 ug1085 TRM 中可知,PL 给到 PS 的中断有两组

2023-08-24 16:06:22 560

560

ZYNQ进阶之路9--PS端实现FreeRTOS嵌入式系统导论FreeRTOS简介实现步骤导论在之前的章节中我们我们完成了PS端、PL端和PS+PL的一些工程,本章节我们插入一个小插曲,讲解

2021-12-22 08:29:20

本帖最后由 何立立 于 2018-1-9 15:03 编辑

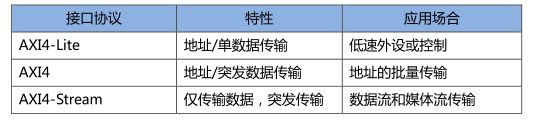

ZYNQ 、AXI协议、PS与PL内部通信 三种AXI总线分别为:AXI4:(For high-performance

2018-01-08 15:44:39

本帖最后由 Tronlong创龙科技 于 2021-6-7 08:48 编辑

本文主要介绍ZYNQ PS + PL异构多核案例的使用说明,适用开发环境:Windows 7/10 64bit

2021-05-28 14:28:28

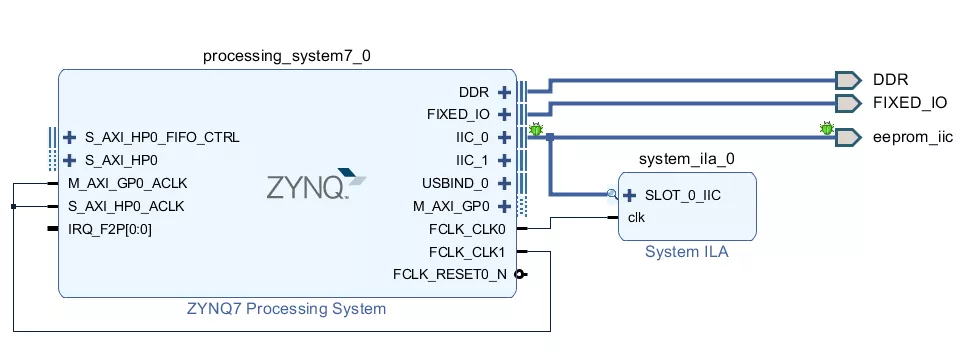

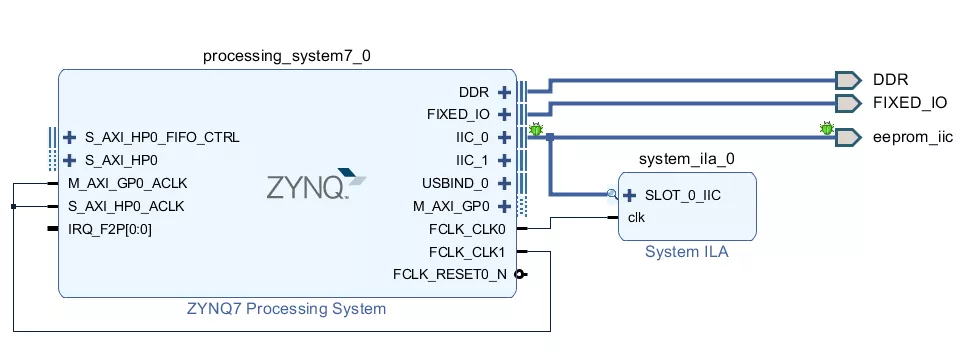

ZYNQ PS端IIC接口使用笔记

2021-02-23 06:23:31

不同类型的DMAHigh performance w/DMA几种DMA的总结ZYNQ中不同应用的DMA几个常用的 AXI 接口 IP 的功能(上面已经提到):AXI-DMA:实现从 PS 内存

2022-03-31 11:39:10

。

③EMIO :由于MIO管脚有限,PS端可以通过EMIO访问PL端引脚。

④GP :通用AXI接口,用来实现一般主从互联、数据交互,不用于高性能。

⑤HP :是高性能/带宽的标准接口,主要用于PL访问PS上

2023-11-03 10:51:39

ZYNQ 分为 PS 和 PL 两部分,那么器件的引脚(Pin)资源同样也分成了两部分。ZYNQ PS 中的外设可以通过 MIO(Multiuse I/O,多用输入/输出)模块连接到 PS 端的引脚

2022-02-08 07:27:16

ZYNQ学习笔记_ZYNQ简介和Hello WorldZYNQ介绍PS和PL的连接ZYNQ开发工具链在PS端编写Hello World程序ZYNQ介绍ZYNQ-7000系列是基于Xilinx开发环境

2022-02-17 07:37:36

PS和PL互联技术ZYNQ芯片开发流程的简介

2021-01-26 07:12:50

本文主要介绍说明XQ6657Z35-EVM 高速数据处理评估板ZYNQ(FPGA)与DSP之间GPIO通信的功能、使用步骤以及各个例程的运行效果。1.1 ZYNQ与DSP之间GPIO通信1.1.1

2023-06-16 16:02:47

实现程序的下载。 从另一个角度来说,PL和PS的配置都可以认为是电脑主机通过 JTAG 完成的。 但是,在实际中,Zynq 开发板不可能实时与电脑连接,当 JTAG 不起作用时,Zynq 芯片

2021-01-08 16:33:01

嗨,我必须找出zynq 7020 PS和zynq PL如何通话,特别是我必须找到将在ARM中处理的SDK C代码。你能用一个明确的C代码告诉我,它解释了数据如何从PS转移到PL,这是ARM用来做这个的基本程序吗?谢谢

2020-05-08 09:37:11

体验,包括了Eclipse IDE 和完整的设计环境,支持Zynq® All Programmable SoC 开发,同时集成了Vivado设计环境;PS端在Linux系统的基础上,支持上位机配置AD9361和模拟数据的采集分析。五、应用领域:软件无线电处理平台;模拟数据采集处理。

2020-03-24 09:39:49

进行编程的初步PS和PL。如果上面有必要的信息,请提供。7.请提供ZYNQ 7Z020-CLG484芯片的所有I / O文档8.如何在没有AXI的情况下将处理器(PS)地址,数据,WRB,RDB连接到PL)。如何使用emio PINS来PL和PL到PS)。请提供必要的信息

2020-03-12 14:39:42

PL端软件PL端完成主要完成的设计功能为 AD、DA 数据输入、输出以及 PL和PS之间的数据交互功能。测试项测试内容测试状态1FPGA程序烧写Sdk程序能够正常烧写2PL端指示灯程序及IO控制下载点

2020-12-08 15:12:32

差分数据传输通道之间的映射关系上述28位并行数据是如何通过4路差分数据传输通道进行传输的呢?28位并行数据映射到4路差分数据传输通道各个时刻点的位置关系如下图所示:1.1.4 管脚约束ZYNQ PL

2023-02-24 10:00:56

设置为5Gbps,参考时钟设置为100MHz。1.1.3 管脚约束ZYNQ PL工程管脚约束如下图所示: 1.1.4 例程使用1.1.4.1 连接光纤模块将光模块插入光模块笼子,并使用光纤线缆将光模块

2023-02-20 17:27:57

一直纠结于怎样给PL提供时钟,zynq开发不同于一般的FPGA开发。其中时钟和复位问题就是相当重要的问题,有两种方式可以为PL部分提供时钟和复位:1、PS部分可以产生四个毫无关系的输出时钟和复位信号

2015-06-08 17:29:32

输入到PL的管脚上一个时钟信号,另一种方法则是使用PS提供给PL的时钟信号。从ZYNQ的技术手册里我们得知,PS部分可以提供给PL四路相对独立的时钟信号(它们之间不保证时序上的关系),因此我们的任务就是

2015-06-01 11:54:12

ARM与PL端Artix-7架构可编程逻辑资源。PS端可通过EMIO配置PL端IO,支持共享内存,支持PS和PL端数据协同处理,可通过PS端配置及烧写PL端程序,且PS端和PL端可以独立开发,互不

2020-04-23 10:32:27

GFLOP,算法能力强,满足目标追踪算法要求。ZYNQ Z-7045/7100集成PS端双核ARM Cortex-A9 + PL端Kintex-7架构28nm可编程逻辑资源,ARM主频800MHz

2021-05-19 17:10:50

_KEY0~PL_KEY1)是直接连接在PL端的IO口上的,可以作为人机交互的输入信号。这2个按键信号默认都是高电平的,当按键被按下之后,按键信号变为低电平。5.2个PS LED领航者底板板载2个PS LED灯

2020-09-21 16:42:52

原子公众号,获取最新资料第十四章基于BRAM的PS和PL的数据交互在ZYNQ SOC开发过程中,PL和PS之间经常需要做数据交互。对于传输速度要求较高、数据量大、地址连续的场合,可以通过AXI DMA来

2020-09-04 11:08:46

之间的高速通信和数据交互,发挥ARM处理器和FPGA的性能优势,需要设计高效的片内高性能处理器与FPGA之间的互联通路。因此,如何设计高效的PL和PS数据交互通路是ZYNQ芯片设计的重中之重,也是

2021-01-07 17:11:26

错误。然后,我在SDK中编程PS端,led闪烁正确的频率!我的问题,当锁定Zynq PL时钟? PS程序之后?需要多长时间?是不是意味着,PL配置期间LED闪烁错误,在非易失性Flas Boot中编程PS期间(或之后)闪烁?谢谢的Berker

2020-08-27 15:09:19

我正在设计使用Zynq(7Z020)作为核心的SIL2产品。我们正在实施Xilinx Zynq安全手册中所述的冗余。在硬件要求一章中,明确指出PS和PL需要两个独立的电源才能达到HFT = 1。在数据

2020-05-22 16:14:42

嗨,我正在寻找一款价格合理的Zynq Ultrascale +主板,其中DDR4接口连接到PL。我想使用一个软核内存控制器。问候,Mosfa

2019-10-17 08:45:37

操作系统开发嵌入式ARM处理通用Zynq-7000 EPP 原型设计Zynq-7000 芯片内部集成了处理器和可编程逻辑,我们知道它的内部大体可以划分为PS(Processing System)和PL

2016-10-05 14:05:31

你好我在Zynq 7010设计上添加了一个UART 16550 IP,中断直接连接到Zynq INTC。在petalinux中导入硬件设计后,pl.dtsi结构似乎没问题,但是当我编译图像并启动板

2020-04-08 07:50:34

://pan.baidu.com/s/1XTQtP5LZAedkCwQtllAEyw提取码:ld9c 1功能概述Zstar的Zynq PL连接了3个LED指示灯。如图所示,3个LED指示灯分别在正极串联

2019-08-28 09:26:47

sd_image文件夹下。打开...zstar.sdkzstar_zynq_ps_wrapper_hw_platform_0文件夹,把PL配置文件zstar_zynq_ps_wrapper.bit也复制到

2019-09-30 14:11:59

`玩转Zynq连载2——Zynq PS的GPIO外设更多资料共享 链接:https://share.weiyun.com/5s6bA0s1 概述 Zynq的GPIO外设控制最多54个MIO引脚,也

2019-04-18 16:33:51

用于GPIO的MIO捉襟见肘时也不用当心,可以打开GPIO EMIO,连接PL端的IO作为PS可控的GPIO使用,这个功能下一个例程我们会讲,这里我们重点要来看看GPIO MIO怎么用。Zstar板载2个

2019-10-10 11:21:06

的就是PL的引脚)。关于MIO和EMIO的关系,更形象直接的可以示意如图所示。MIO和EMIO都是PS的一部分,但是MIO可以直接连接到Zynq芯片的引脚上,和PL无关;而EMIO需要通过PL的IO

2019-10-12 17:35:16

zstar_zynq_ps_wrapper.v,可以看到有很多AXI_GP0打头的信号增加到了系统中,这些信号就是Zynq系统作为主机连接到PL的AXI GP总线接口。接下来我们要做的事就是设计一个

2019-11-12 10:23:42

总线读或写通道每秒的数据传输字节数。4 PL代码解析工程代码的层次结构如图所示。zstar.v模块是顶层模块,将ZYNQ Procssing System引出的4条AXI HP总线的读写通道分别连接

2019-11-28 10:11:38

请问zynq 怎么实现PS与PL数据交互,然后通过UART串口打印出来?前辈们做过的指导我一下。

2020-08-03 15:53:30

想让FX3的UART口和Xilinx ZYNQ7000的PS(Processor system)端的内置UART相互通信,两个芯片使用的是同一个电源(同在一块板子上或分别在两块相互连接的板子上),请教一下它们之间的硬件连接需要TTL电平转换(使用2块MAX3232ESE芯片,如下图所示)么?谢谢

2024-02-28 08:32:43

XAPP1251说明显示,可以在Zynq ARM处理器上运行XVC服务器来控制FPGA中的JTAG端口。但是,我不清楚,是否可以在同一个FPGA中控制PL JTAG?可以使用运行在设备PS部分上

2020-07-30 13:51:19

开发。因为模组支持MQTT协议,所以直接采用AT指令进行数据命令交互通信,这种方式也是最简单,开发最快的。如下截图,乃是其AT指令手册的MQTT有关的AT指令篇。在开发使用了多款不同的通信模块之后,也知道其无非分为这几个步骤:1.等待模块初始化;2.注册激活网络3.MQTT连接参数配置4.MQTT登

2022-01-27 06:18:59

本文通过实例详细解析如何利用Zynq-7000的PL和PS进行交互。实际上,Zynq就是两大功能块:双核Arm的SoC和FPGA。根据Xilinx提供的手册,PS: 处理系统 (Processing System) , 就是与FPGA无关的A

2012-12-12 13:40:22 53205

53205

分享下PS与PL之间数据传输比较另类的实现方式,实现目标是: 1、传输时数据不能滞留在一端,无论是1个字节还是1K字节都能立即发送; 2、PL端接口为FIFO接口; PS到PL的数据传输流程: PS

2017-02-08 01:00:11 1431

1431

作者:Hello,Panda Part3 I/O资源 和Zynq-7000相比较,Zynq UltraScale+ 增强了PS端的IO性能;PL端每个产品系都有HR和HP两种类型的IO。 1.PS

2017-02-08 08:29:11 491

491

到目前为止,我们已经在之前的文章中聊过Zynq SOC内部的 PS和PL,以及在Zynq SoC PS部分的ARM Cortex-A9处理器上运行的操作系统。但是有一个领域我们还没有去探索过,那就是在芯片的PL上构建软核处理器。

2017-02-08 14:04:41 989

989

了解Zynq PS / PL接口之后;到目前为止,我们已经分析了Zynq All Programmable SoC芯片中的PS (处理器系统)与PL(可编程逻辑)之间的接口。

2017-02-10 12:00:11 957

957

我们先来了解一下上节中介绍的Zynq SoC PS/PL接口,我创建一个很简单的外设,使用的是DSP48E1的DSP逻辑片,依靠这个外设第一个寄存器内的控制字执行乘法,加法或减法。

2017-02-10 12:04:41 469

469

《一步一步学ZedBoard & Zynq》系列第二篇,目的是为了学习不使用ARM PS情况下,只对Zynq PL的编程方法,同时学习Xilinx?PlanAhead工具的使用方法?

2017-02-10 20:24:11 3749

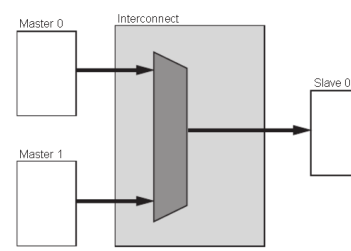

3749 构建SoC系统,毕竟是需要实现PS和PL间的数据交互,如果PS与PL端进行数据交互,可以直接设计PL端为从机,PS端向PL端的reg写入数据即可,本节研究如何再实现PL端对DDR3的读写操作。

2017-09-18 11:08:55 23

23 Zynq芯片中,PS(ProcessorSystem)和PL(Programmable Logic)之间提供了一共9个双向读写的通信端口,他们分别是: M_GP0 M_GP1 S_GP0 S_GP1

2017-11-17 10:03:39 11543

11543 相比较经典的FPGA,Zynq-7000系列最大的特点是将处理系统PS和可编程资源PL分离开来,固化了PS系统的存在,实现了真正意义上的SOC(System On Chip)。 1.

2017-11-18 05:11:01 18880

18880

Zynq-7000 PL端HDMI的显示控制 Zynq-7000 PS到PL端emio的使用 Vivado 专家文章:Tcl 是什么? Zynq-7000 ARM端MIO的使用 Zynq

2019-09-15 14:57:00 3305

3305 ZYNQ-7000如何生成从Flash和SD卡启动的镜像文件 将PL与PS部分一起使用,并且通过JTAG下载到板子运行。对于ZYNQ,有多种启动方式

2018-12-01 08:38:18 7278

7278

Zynq在PS和PL之间有9个AXI接口。

2018-12-30 09:45:00 6907

6907 在ps的控制下,可以实现安全或非安全的配置所有ps和pl。通过zynq提供的JTAG接口,用户可以在外部主机的控制下对zynq进行配置,zynq不支持最开始就配置pl的过程。

2019-05-15 11:41:31 7190

7190

因为ZYNQ 的PS 和PL 部分的电源有上电顺序的要求,在电路设计中,按照ZYQN 的电源要求设计,上电依次为1.0V -> 1.8V -> 1.5 V -> 3.3V -> VCCIO,

2020-01-01 17:27:00 10685

10685

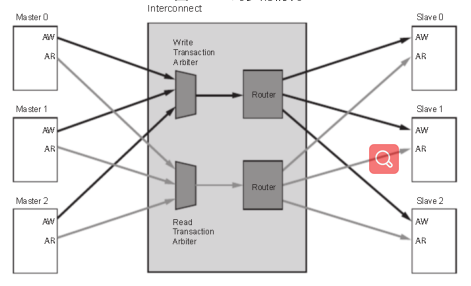

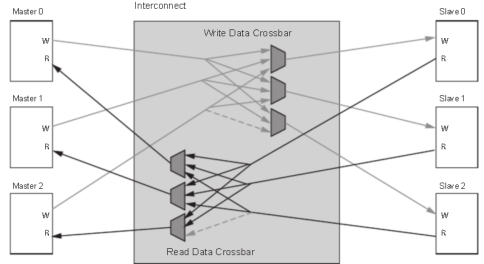

如何设计高效的 PL 和 PS 数据交互通路是 ZYNQ 芯片设计的重中之重。AXI 全称 Advanced eXtensible Interface,是 Xilinx 从 6 系列的 FPGA 开始引入的一个接口协议,主要描述了主设备和从设备之间的数据传输方式。

2020-03-15 17:04:00 10317

10317

MPSoC是Xilinx基于16nm工艺推出的异构计算平台,由于灵活、稳定,在业界得到了广泛的使用。异构计算是一个比较新的领域,需要协调硬件设计、逻辑设计、软件设计,对工程师的要求很高。实际设计过程中,很多工程师对实现PS/PL之间的数据交互感到头疼。

2020-09-15 09:27:00 11208

11208

在ZYNQ中,支持AXI-Lite,AXI4和AXI-Stream三种总线,但PS与PL之间的接口却只支持前两种,AXI-Stream只能在PL中实现,不能直接和PS相连,必须通过AXI-Lite

2020-09-24 09:50:30 4289

4289

ZYNQ中DMA与AXI4总线 为什么在ZYNQ中DMA和AXI联系这么密切?通过上面的介绍我们知道ZYNQ中基本是以AXI总线完成相关功能的: 图4‑34连接 PS 和 PL 的 AXI 互联

2020-11-02 11:27:51 3880

3880

Xilinx 用两个 96 位独特器件标识符(称为器件 DNA)为每个 Zynq UltraScale+ 器件编程。一个 DNA 值位于可编程逻辑 (PL) 中,另一个 DNA 值位于处理系统 (PS) 中。这两个 DNA 值是不同的,但每个 DNA 都有以下属性及读取访问方法。

2022-02-08 14:19:49 1149

1149

Xilinx 用两个 96 位独特器件标识符(称为器件 DNA)为每个 Zynq UltraScale+ 器件编程。一个 DNA 值位于可编程逻辑 (PL) 中,另一个 DNA 值位于处理系统 (PS) 中。这两个 DNA 值是不同的,但每个 DNA 都有以下属性及读取访问方法。

2021-01-23 06:32:33 10

10 ZYNQ7000系列FPGA的PS自带两个IIC接口,接口PIN IO可扩展为EMIO形式即将IO约束到PL端符合电平标准的IO(BANK12、BANK13、BANK34、BANK35);SDK

2021-01-28 08:05:27 25

25 FPGAs,Zynq 和 Zynq MPSoC! Zynq MPSoC是Zynq-7000 SoC(之后简称Zynq)的进化版本。Zynq是赛灵思发布的集成PL(FPGA)和PS设计的最早的一代产品

2021-04-02 17:20:14 13783

13783

刚学ZYNQ的时候,看到里面反复提到PS和PL,还以为PS是PhotoShop的意思,PL是哪种型号的简称。 稍微了解之后才知道,ZYNQ是ARM和FPGA的组合,PS是programming

2021-06-18 16:09:46 8666

8666 ZYNQ 分为 PS 和 PL 两部分,那么器件的引脚(Pin)资源同样也分成了两部分。ZYNQ PS 中的外设可以通过 MIO(Multiuse I/O,多用输入/输出)模块连接到 PS 端的引脚

2021-12-04 18:51:06 16

16 ZYNQ学习笔记_ZYNQ简介和Hello WorldZYNQ介绍PS和PL的连接ZYNQ开发工具链在PS端编写Hello World程序ZYNQ介绍ZYNQ-7000系列是基于Xilinx开发环境

2021-12-22 19:11:29 10

10 的协议,可用于寄存器式控制/状态接口。例如,Zynq XADC 使用 AXI4-Lite 接口连接到 Zynq PS。

2022-05-10 09:52:12 1949

1949 这篇文章记录ZYNQ7020的PS端的基本开发流程,关于PL端的开发流程,参考之前文章,这里放个超链接。

2022-07-24 18:12:57 5860

5860 MPSoC含有PS、PL;在PS和PL之间有大量接口和信号线,比如AXI、时钟、GPIO等。缺省情况下,PS和PL之间有接口和信号线被关闭。加载bit后,软件才会打开PS和PL之间的接口和信号线

2022-08-02 09:45:03 676

676 Zynq MPSoC是Zynq-7000 SoC(之后简称Zynq)的进化版本。Zynq是赛灵思发布的集成PL(FPGA)和PS设计的最早的一代产品。如图2.1所示,在相对较高层次对比了三种器件。Zynq MPSoC的PS部分比Zynq的PS部分面积更大,也更复杂。本章,将介绍这三种器件的特点.

2022-08-15 09:16:38 1629

1629 ZYNQ处理系统端PS所有的外设都连接在AMBA(Advanced Microcontroller Bus Architecture)总线,而基于FPGA设计的IP则可以通过AXI接口挂载在AMBA总线上,从而实现内部各组件的互联互通。这里涉及到两个概念:

2022-08-15 09:42:24 1345

1345 zynq 中带有两个硬核千兆以太网MAC,ENET0,ENET1。与普通SOC 芯片不同,zynq PS 断地外设可以通过MIO连接到芯片的引脚上,也可以通过EMIO 接口连接到PL 端。连接到PL端后,带来了灵活性,可以转换成各种接口。比如设计一个交换机。定义端其它的引脚。

2022-09-23 15:19:58 2023

2023 在无 JTAG 的模式下,Zynq 是通过片上CPU完成对芯片的配置,也就是PS和PL的配置是通过 PS 处理器 ARM 核来实现的。需要注意的是,与传统的 Xilinx 7 系列 FPGA 芯片不同,Zynq 是不支持从 PL 端进行直接启动配置的,一定要通过 PS 部分来完成。

2022-10-19 09:11:55 986

986 电子发烧友网站提供《将Zynq PS和PL与内存映射寄存器集成.zip》资料免费下载

2022-12-06 15:14:29 2

2 S_AXI_ACP_FPD接口实现了PS 和PL 之间的低延迟连接,通过这个128位的接口,PL端可以直接访问APU的L1和L2 cache,以及DDR内存区域。故PL侧可以直接从cache中拿到APU的计算结果,同时也可以第一时间将逻辑加速运算的结果送至APU。

2023-02-01 15:36:53 1708

1708 ZYNQ 芯片分为 PL 和 PS, PS 端的 IO 分配相对是固定的,不能任意分配,虽然 PS 端的 ARM 是硬核,但是在 ZYNQ 当中也要将 ARM 硬核添加到工程当中才能使用,FPGA

2023-08-11 09:36:34 4805

4805

ZYNQ内部的总体框架如所示,PS中包含2个ARM Cortex-9的内核,一些基本的外设扩展口以及Memory接口。PS和PL的相互通信通过两个通路完成,分别是GP(General Purpose)Ports和HP(High Performance)Ports。

2023-09-22 09:26:13 492

492

前言本文主要介绍PS+PL端异构多核案例的使用说明,适用开发环境:Windows7/1064bit、XilinxVivado2017.4、XilinxSDK2017.4。案例位于产品资料“4-软件

2023-01-03 15:50:37 18

18

电子发烧友App

电子发烧友App

评论